在宽带隙半导体开关的新时代,器件类型的选择包括具有自己的特性并声称具有最佳性能的SiCMOSFET和GaN HEMT单元。但是,这两者都不是理想的开关,这两种器件类型在某些方面都有局限性,特别是在栅极驱动要求和“第三象限”操作方面。

SiC FET是替代选择

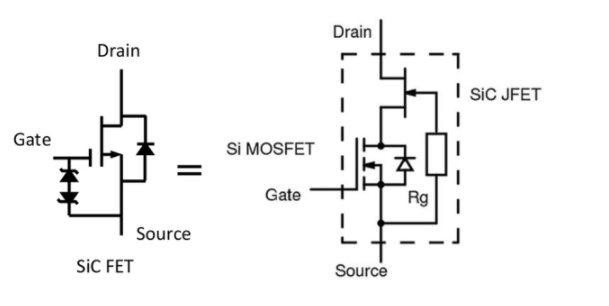

但是,还有另一种选择。UnitedSiC FET是SiC JFET和低压Si MOSFET的共源共栅组合,可生产出具有SiC所有速度的器件,并具有SiC最低的导通损耗优势,但栅极驱动容易且快速,低功耗。用于三象限传导的损耗体二极管(图1)。

图1:SiC FET — SiC JFET和Si MOSFET的级联

SiC FETS的速度非常快,其边沿速率为50 V / ns或更高,这对于最大程度地降低开关损耗非常有用,但所产生的di / dt可以为每纳秒许多安培。通过封装和电路电感,这会产生高电平的电压过冲和随后的振铃。在这些电流变化速率下,简单的分析告诉我们,即使几十纳米的亨利也可能产生数百伏的过冲(来自E= –L(di/dt))。对于快速切换的WBG器件,最小化该杂散电感至关重要。但是,这在实际的布局中很难实现,因为这些布局必须在高压组件之间实现安全距离,并且为了获得更好的热性能而使用更大的半导体封装。

过冲有超过器件额定电压的风险,并增加了组件的长期应力,但是快速边缘也会引起绝缘击穿,并会产生更多的EMI,因此需要更大,更昂贵且损耗更高的滤波器。因此,实用电路通常会故意降低此类快速开关的边沿速率,从而可能允许使用具有更好传导损耗和更小滤波器的低压设备,从而抵消了稍高的开关损耗。

缓慢的开关沿可减少过冲和EMI

有两种常见的减慢开关沿速度的方法:通过增加栅极电阻和在器件的漏极-源极端子之间使用缓冲器来实现。

栅极电阻的增加确实会降低dV / dt,从而减少过冲,但是对漏极电压的随后振铃影响很小。栅极电阻器的减慢效果取决于器件的总栅极电荷,而栅极电荷又取决于诸如栅极-源极电容和“米勒”效应的参数,随着器件切换,“米勒”效应表现为变化的栅极-漏极电容。可以通过使用两个带二极管控制的栅极电阻来分别控制导通和关断延迟,但是要在所有工作条件下优化条件都很难实现总体效果。此外,增加栅极电阻会给栅极驱动波形带来延迟,这在高频时可能会出现问题。

相反,简单的Rs-Cs缓冲器可通过有效地向开关的漏极增加电容来减慢dV / dt。另一个效果是,由于一些电流被转移到充电Cs中,因此减小了关断时电压上升和电流下降之间的重叠,从而降低了器件开关损耗。开关导通时,必须限制电容器的放电电流,因此要串联一个电阻,当器件关闭时,该电阻还可以抑制振铃。缺点是电阻器在此过程中不可避免地会消耗一些功率,并且半导体开关效率的增益会在一定程度上被抵消。

缓冲器可以成为低损耗的解决方案

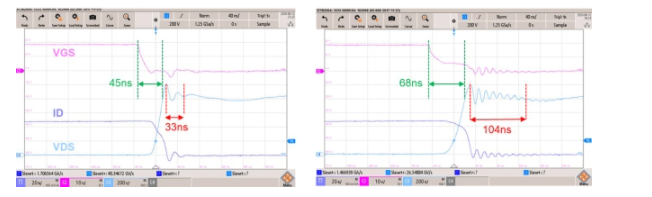

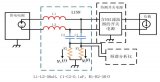

SiC FET技术的领导者UnitedSiC所做的工作表明,与增加栅极电阻相比,只需要一个非常小的缓冲电容器和一个相应的低功率电阻即可实现dV / dt,过冲和振铃的更有效控制。独自的。当小型设备缓冲器与可以使用的较低Rg结合使用时,结果是波形更清晰的总损耗也更低。这种方法对于UnitedSiC的FET和传统的SiC MOSFET都适用。在图2中比较了阻尼器为200 pF / 10Ω的器件(左)与添加了5Ω栅极电阻的器件(右)之间的振铃和dV / dt。虽然两种方法都类似地调整到相同的VDS在关断期间达到峰值时,缓冲版本明显显示出更短的延迟时间和更好的振铃阻尼。

图2:使用RC器件缓冲器可降低dV / dt,ID / VDS重叠以及SiC MOSFET的振铃。(ID = 50 A,V = 800 V,TO247-4L;左,SiC MOSFET的关断波形,Rg,off = 0Ω,Rs = 10Ω,Cs = 200 pF;右,SiC MOSFET的关断波形,Rg,off = 5Ω,无设备缓冲)

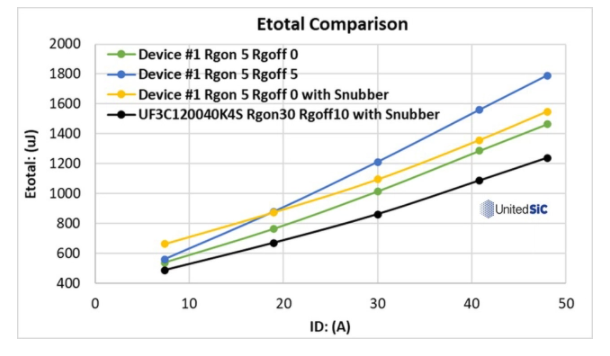

总损耗是传导损耗,上升沿和下降沿上的器件开关损耗以及缓冲电阻器中消耗的任何功率的总和。通过与SiC MOSFET器件进行比较,在UnitedSiC上进行的测试表明,在高漏极电流下,采用缓冲解决方案时的关断能量损耗(EOFF)可能仅为峰值电压仅通过栅极电阻器等效调谐时的损耗的50%。同时,导通能量(EON)略高(仅约10%),因此,例如,对于以40 kHz和48 A / 800 V开关的40mΩ器件,净效应是总的好处。每个周期约275 µJ的缓冲器,或11W。这种比较在图3中以蓝色和黄色曲线表示。黑色曲线是具有缓冲和优化的栅极开/关电阻的40mΩUnitedSiC SiC FET器件的性能,

图3:比较有无缓冲的SiC开关的总开关损耗

缓冲电容器在每个开关周期都充满电和放电,但要注意的是,这种存储的能量并没有全部消耗在电阻器中。实际上,大多数CV2能量实际上是在导通期间在设备中耗散的。在引用的示例中,在40 kHz,ID 40 A,VDS 800 V和220-pF /10-Ω缓冲器的情况下,耗散的总功率约为5 W,但电阻中只有约0.8W。其余的在开关中。这样就可以在适当的额定电压下使用物理上较小的电阻器(甚至是表面贴装电阻器)。

UnitedSiC提供D2pk7L和DFN8×8封装的器件以及TO247-4L,以实现最佳的散热性能。TO247-4L部件与源极之间具有开尔文连接,可有效消除源极电感的影响,改善开关损耗,并在高漏极di / dt时产生更清晰的栅极波形。

结论

器件缓冲似乎是管理开关过冲,振铃和损耗的“强力”解决方案,而诸如IGBT之类的较老技术的情况则尤其如此,因为它们的“尾电流”长,需要大型且有损耗的缓冲网络。但是,宽带隙器件,特别是SiC FET,可以使用该技术作为栅极电阻调谐的优良替代方案,以提供总体较低的损耗,并且可以采用紧凑,廉价的组件来实现。

编辑:hfy

-

电容器

+关注

关注

64文章

6278浏览量

100528 -

MOSFET

+关注

关注

147文章

7364浏览量

214955 -

缓冲器

+关注

关注

6文章

2000浏览量

45804 -

SiC

+关注

关注

30文章

2959浏览量

63228 -

栅极驱动器

+关注

关注

8文章

775浏览量

39134 -

宽带隙半导体

+关注

关注

0文章

34浏览量

80

发布评论请先 登录

相关推荐

高开关频率对电机驱动系统的影响

开关电源的EMI/EMC测试标准

浮思特 | 宽带隙半导体技术能否引领汽车行业的电动化革命?

宽带隙功率半导体双脉冲测试解决方案

负载开关芯片-负载开关电路芯片

如何减少半导体行业温室气体排放

如何减少开关电源的导通损耗

英国Pickering公司发布新款开关保护模块,面向半导体参数测试中的低漏电流测试

Nexperia斥资2亿美元加速汉堡工厂宽带隙(WBG)半导体研发与生产

宽带隙(WBG)半导体助力可持续电动汽车电源转换,顶部冷却(TSC)技术提升热性能

功率半导体市场将迈向550亿美元新高度

宽带隙半导体开关:缓慢的开关沿可减少过冲和EMI

宽带隙半导体开关:缓慢的开关沿可减少过冲和EMI

评论