走线熙熙,汲汲交期;走线攘攘,亟亟归档。

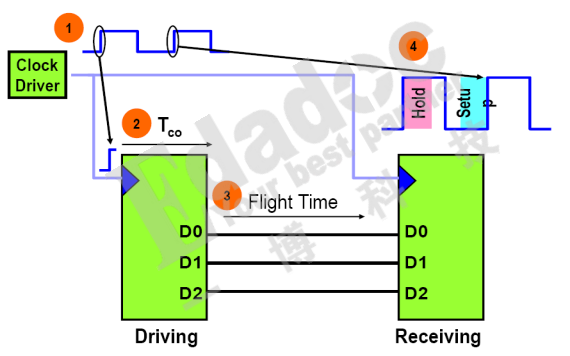

项目伊始,高速先生的内心其实是抗拒的,因为实在看不出仿真的必要:目标信号是DDR3L,数据速率最高800Mbps,地址控制类信号走线拓扑为一拖二、T型拓扑。信号普通、速率寻常、拓扑简单。

架不住客户的一再坚持,加上前期项目介入阶段,客户言辞闪烁,提供PCB文件时也不大爽快,似乎有难言之隐,高速先生渐生警觉——事情可能并没有想象的那么简单。客户最终还是提供了单板文件,不过一直强调是外协设计的。

打开板子仔细查看,却是险象环生,高速先生精神为之一振,心里大概有了谱。虽然有了预判,不过,对于如此不走寻常路的设计以前只是耳闻,今日一见,难免兴奋,实在想看看仿真结果与预期是否一致。

考虑选择地址控制类信号作为仿真对象,之所以这么做除了因为该单板的此类信号布线激进,另一个原因是相对于绝大多数数据信号的点到点拓扑,地址控制类信号通常是一拖多,而且没有数据信号对应的片内端接来减小反射,因此出问题的概率相对较大。先看DDR3L地址控制类走线最长的信号波形(如下图):高低电平分明,满足阈值要求,边沿单调,没有回沟,整体看来虽然有轻微的过冲和振铃,不是十分完美,也算比较正常。

难道就这样愉快的PASS了?不,还没到重点。因为通道整体仿真的结果会让你得出截然相反的结论!不信请看同组地址信号同时运行时黯然失色的眼图:仿佛熬夜之后勉强睁开的眼睛,布满血丝,感受到他的疲惫了吗?

不好意思,放错图了,应该是这张。

单拎出来的信号质量没问题,同组信号一起运行却不给力,想必一直关注高速先生公众号的朋友已经想到了答案:串扰!是的,高速先生也这么想。尤其是在高速先生新近推出一期关于层间串扰的短视频之后,串扰问题更是引起了不少人的关注。

回到本期案例,继续抽丝剥茧。仔细观察DDR3L地址信号走线之间的间距就能发现端倪:线宽0.1mm,相邻走线air-gap也是0.1mm!而且还不是零散的个别现象,整个通道的地址控制类信号都是如此处理。

当然了,以上关于串扰的推断还只是大胆的假设,下面就需要小心的求证。既然怀疑问题的症结在于串扰,那么对比不同程度的串扰对通道信号的影响最具有说服力。好在仿真的时候可以调整串扰系数,这样就不必等客户提供不同的PCB版本来逐一验证。提取参数时通过调整串扰系数,先将串扰降低为原版本的75%,由于振铃的减小,眼睛中的“血丝”开始减少,眼图如下:

继续调整串扰系数,将串扰减小至原设计的50%,信号振铃进一步减小,眼图逐渐恢复正常。

直接将串扰减小到原设计的5%,整个眼图都变的精神抖擞,十分清爽。

通过仿真反馈,客户最终还是把DDR3L的走线中心距调整至3W,线距调整后的通道仿真结果达到了预期的要求。

后来才了解到,初始版本PCB是客户的一个Layout新手设计,初生牛犊不怕虎,加上交期的压力,走线约束设置出现偏差,于是就出现了这么一版试探信号底线的设计,相信经过这次返工的煎熬,串扰对这名Layout攻城狮而言不会再是书本上苍白的理论。正所谓:走线熙熙,急赶交期;走线攘攘,串扰飙涨。只是,有多少走线可以重来,有多少单板经得起等待?

编辑:hfy

-

pcb

+关注

关注

4319文章

23094浏览量

397716 -

DDR3

+关注

关注

2文章

276浏览量

42259

发布评论请先 登录

相关推荐

pcb开窗怎么设计_PCB设计怎样设置走线开窗

PCB设计有哪些误区PCB设计的十大误区上部分内有下部分链接

PCB设计有哪些误区PCB设计的十大误区下部分内有上部分链接

高速PCB设计有没有什么技巧

PCB设计有着怎样的规范

SMT生产设备对PCB设计有哪些要求

可以优化ESD防护的PCB设计准则

有关PCB走线以及如何为PCB设计正确走线的重要事项

PCB设计有多少线可以重来?

PCB设计有多少线可以重来?

评论