DC-DC转换器所产生的EMI,一直给无线和物联网设备的设计人员造成困扰。宽带谐波成分通常会达到1.5GHz,从而涵盖大多数无线协议、蜂窝LTE和GPS/GNSS频段。

在如何减少无线和物联网设备自我产生的EMI方面,我已经写了几篇文章并主持了几场网络研讨会,而解决这类EMI的关键方法之一,是实现适当的PCB设计。最近我就这个主题主持了一场很长的网络研讨会。如果您错过了这个演讲,欢迎您观看其网络录像回放。这场研讨会中探讨了几个有关PCB设计和降低DC-DC转换器EMI的问题,我的回答如下。

问:什么时候可以以电源平面作为电路走线的参考?

图1:常见的四层层叠示例,其EMI非常差。

这是个常见问题,它是由于使用了典型的四层和六层电路板设计所引起,其中电源平面和地回路平面通常完全分开(图1)。高频(>100kHz)信号实际上是电磁波,其返回电流通常以数字地回路作为参考,如果您了解这点,那么您就能更好地理解为什么参考电源平面是个坏主意。这类返回电流需要找到一种方法“以某种方式”返回数字回路,因此其所经过的路径可能会产生EMI。在我看来,当且仅当电源平面和返回平面之间实现紧密耦合并且通过去耦电容很好地实现旁路时,才可以将非关键信号(低频、控制信号等)以电源作为参考。对于典型的四层板和六层板层叠,则通常不是这种情况。在大多数情况下,以电源平面作为参考运行高频数字信号,对EMI来说存在高风险。我建议您在设计电路板时参考我的四部分系列文章“Design PCBs for EMI”以实现低EMI。

问:“铺地”是否有助于隔离噪声信号?

隔离噪声信号的最佳方法是实现适当的PCB层叠。也就是说,所有高频(>100kHz)数字信号的走线都应与实心返回平面相邻。这就可以抑制电磁波。返回平面的断裂会导致EMI增加15至20dB(请参阅参考资料中我的视频演示)。根据Eric Bogatin博士的说法,取决于电路板设计,铺地通常实际上并没有帮助,而且还可能有害,因为在某些情况下,铺地可能会在返回平面上表现为“断裂”。有兴趣者可访问他的网站,获取更多有关PCB设计和铺地的信息。

问:从电路板的顶部到底部运行时钟走线时,在附近为返回电流增加通孔有多重要?

这要视情况而定,并且其答案通常也可以用来回答许多EMC问题!如果电源平面和返回平面之间的距离很近(最大2~3mil),并且电路板上有足够的去耦电容,那么为返回电流路径添加邻近过孔就没有那么重要了。但是,对于诸如时钟之类的关键走线,我会添加一个或多个过孔以确保对电磁波严格控制。这里我再次向您推荐我上述“通过PCB设计降低EMI”的系列文章。

问:上升时间和下降时间对EMI有什么影响?脉冲宽度的上升和下降所占百分比应是多少?

Eric Bogatin博士在他的Signal and Power Integrity Simplified, 3rd edition一书中对这个主题做出了出色的讨论(请参见下面的推荐书列表)。简而言之,可以使用公式BW=0.35/RT,其中,BW(带宽)以GHz为单位,RT(10~90%上升时间)以ns为单位。因此,对于1ns的上升时间,带宽约为0.35×1GHz,即350MHz。脉冲宽度会影响谐波的幅度。随着其减小,总振幅也将减小。随着脉冲宽度的减小,到某个点后,上升时间和下降时间会开始变成一个圆角的脉冲(在固定RT/FT的情况下),因此存在某个点,好的矩形脉冲形状到此就开始瓦解。我不确定RT与脉冲宽度的百分比是否有通用规则。

问:电子仅以1cm/s的速度传播?

这个问题与我对数字信号如何在PCB中传播的解释有关。我们中的大多数人都被教导(或至少暗示)了信号实际上是电子在铜线或走线中的流动,而且电子是以接近光速的速度而运动。尽管对于DC电路而言确实如此,但电子不会以接近光速的速度行进,因为它们在铜原子中的结合非常紧密。在高频(>100kHz)下,数字信号实际上是电磁波,它通过铜走线和返回平面之间的介电层传播。在DC和100kHz之间存在一个过渡区域,在此,信号从纯DC电流转变为电磁波。

图2:地回路平面上的微带截面图,借此即可从物理上了解,数字信号在走线和返回平面之间的介电空间内是以电磁波形式传播。

这个电磁传播模型由两个元素组成:传播波本身——其在电介质(假设为FR4电介质)中传播的速度约为光速的一半;传导电流(即电子在铜原子中的流动)和位移电流(“通过”电介质)的组合(图2)。这个传导电流可以使用电流表来测量,但是电子仅以约1cm/s的速度运动。我发现在大多数领域和电波教科书中通常都没有对这种数字信号传播的物理模型进行教授。但是,我推荐两个参考文献:Eric Bogatin博士撰写的Signal and Power Integrity Simplified, 3rd edition(第245至252页),以及Ron Schmitt撰写的Electromagnetics Explained – A Handbook for Wireless/RF, EMC, and High-Speed Electronics(第33~34、84~86和96~98页)。另请参阅我的“通过PCB设计降低EMI”的系列文章。

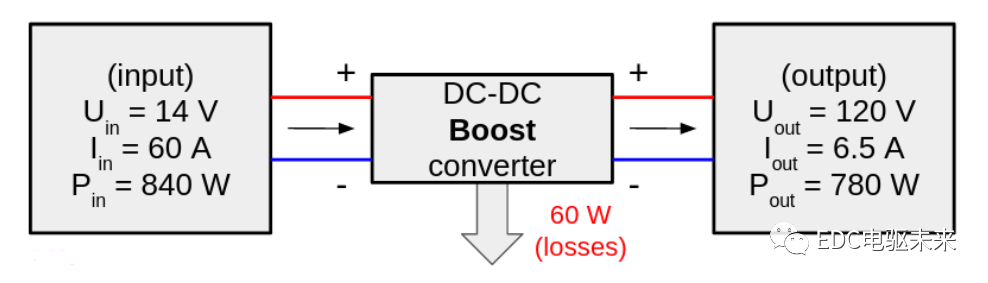

问:具有集成电感的电源模块是否对降低EMI更好?

是的,因为输入输出回路的面积实现了最小化。一个例子是凌力尔特的“μModule”片上系统(SoC)。请参见图3以及ADIμModule升降压稳压器页面。

图3:这个来自凌力尔特公司的DC-DC转换器的例子,显示其将集成电感(在本例中为变压器)Cin和Cout全部集成到了SoC中。这种设计最大程度地减少了噪声电流回路,从而可以降低EMI。(图片来源:凌力尔特)

问:开关节点平面下方直到底部是否需要开孔以减少电场耦合?

这是个很好的问题!显然,我们希望最大程度降低开关节点(SW)到电感的走线的面积,以减少到该点的耦合,在上例中,该点可能开关高达42V的方波而产生强烈的电场(图4)。

图4:这是个典型的DC-DC降压转换器,其上显示了开关节点(SW)和输出电感。争论的焦点是是否要在SW节点或电感或者两者的附近将返回平面切掉。(图片来源:凌力尔特)

几年前,我觉得把开关节点(SW)区域中的返回平面切掉对于减少电容耦合很重要,直到我真正开始从物理角度研究数字(在上述情况中为功率开关)的工作方式为止。虽然我现在坚信返回平面在DC-DC转换器的所有部分下面都应保持为实心平面,但您的论点也不能完全忽视,这可能取决于实际情况。

EMC和PCB设计领域的著名专家Todd Hubing博士、Rick Hartley和Daniel Beeker都认为,返回平面应为实心。另一方面,我所认识的信号完整性(SI)和配电网络(PDN)专家,例如Steve Sandler,正在沿着您的思路进行思考。目前,我已经和Steve Sandler和Todd Hubing开始了一项研究,其中就包括对这个问题进行调查。Steve已同意制作几块电路板来测试信号完整性和电源完整性,而我则会测量辐射发射和传导发射。这个研究应该会引起关注,而有可能最终形成技术论文。目前,我对实心返回平面的看法不会改变,除非得到其他证明。

问:使用吸波材料后,我们看到EMI衰减了。但是否需要将它放到电路内部的某个其他地方(未知)而不是放在外面呢?

实际上,来自IC或电路走线的辐射发射,会受到有损铁氧体材料吸收而转化为热量。

问:在DC-DC转换器输入和输出上串联铁氧体磁珠,是否是个好主意?

结合我的RF设计背景,这是RF电路非常普遍的做法——我仍然相信该技术可能会获得成功使用。近年来,随着我研究电源完整性,我开始改变主意。为了获得良好的PDN性能,我们不希望PDN中有任何串联阻抗。已故的Steve Weir在其PowerCon演讲中,以及Eric Bogatin博士和Larry Smith在其著作Principles of Power Integrity for PDN Design Simplified的最新教材中,都清楚地说明了这一点。如果确实想要在输入或输出滤波器中这样做,那么就需要确保在铁氧体磁珠和数字开关转换器IC之间添加一个额外的大容量电容(4.7至27μF陶瓷)。我仍然不建议添加它。

编辑:hfy

-

emi

+关注

关注

53文章

3588浏览量

127651 -

物联网

+关注

关注

2909文章

44624浏览量

373177 -

DC-DC转换器

+关注

关注

10文章

617浏览量

55561

发布评论请先 登录

相关推荐

面向新太空应用的DC-DC转换器解决方案

dc-dc转换器工作原理

DC-DC转换器控制电路大约多少钱?

DC-DC转换器电路图 Boost升压型DC-DC转换器的工作原理

DC-DC电源转换器的布局布线建议

为什么DC-DC转换器这么有用?

关于PCB设计和降低DC-DC转换器EMI的解决方案(一)

关于PCB设计和降低DC-DC转换器EMI的解决方案(一)

评论