作者:Eric Braun,Jinghai Zhou等

作为开关电源损耗的一部分,印刷电路板(PCB)主回路纹波电流阻抗的损耗常被忽略不计。然而,对于采用大电流核心电压和高纹波电流工作的应用而言,这种损耗却不容忽视。使用Ansys Q3D,可以提取典型核心电压功率级 PCB 布局中主回路纹波电流的频变电阻参数,还可以看出这一损耗成分是如何显著改善建模与测量总损耗之间的相关性(开关频率函数)。为了在负频率系数PCB与无源元件损耗和正频率系数MOSFET常规开关损耗之间的平衡点处达到峰值效率,我们提出了一种优化开关频率的解析表达式。

介绍

过去,建模降压变换器功率损耗的主要研究对象是半导体器件损耗[1-5],还有小部分集中在无源元件损耗上[1-2],但针对PCB损耗和PCB 交流电阻损耗,却鲜有触及。对于这些损耗,可以通过使用Ansys Q3D,提取出典型核心电压驱动器和MOSFET(DrMOS)应用的PCB主回路交流电阻(ACR),从而计算出相关的纹波电流ACR损耗。由于峰 - 峰纹波电流的增加,这些损耗会随着频率的降低而非线性地增加,导致在较高的开关频率下,峰值效率低于传统的损耗分析预测数值。

PCB 主回路交流电阻的模型、仿真和测量

同步降压变换器的主要功率损耗可归纳为有源元件损耗(MOSFET 直流和开关损耗、MOSFET 驱动器损耗)、无源元件损耗(电感直流电阻、交流电阻和核心损耗、电容等效串联电阻损耗)和印刷电路板损耗(PCB 直流电阻和交流电阻损耗)。

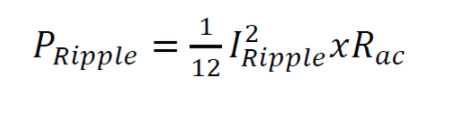

PCB频变电阻损耗是由于主回路中循环的锯齿纹波电流所造成的,该纹波电流可根据公式(1)计算得出:

(1)

其中 Rac 为纹波电流波形的PCB频变有效电阻。核心电压(Vcore) DrMOS 同步降压变换器在峰值效率运行条件下具有较大的纹波电流,为研究提供了案例。可将多相核心电压 PCB功率级布局的单相部分导入Anysis Q3D(参见图1a)中,并估计出PCB 交流电阻损耗成分。图1b显示了PCB主回路纹波电流循环路径中Q3D仿真的交流电流分布图。

图1:PCB核心电压主回路 Q3D 结构模型和 AC 电流仿真

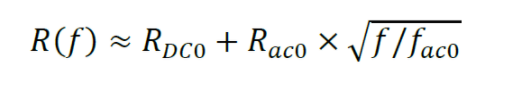

Q3D提取的频变电阻与图2所示的板级LCR测量值非常匹配。另外,PCB 频变电阻也与公式(2)中所示的理想集肤效应模型相当一致:

(2)

通过对 15% 占空比三角波的加权傅里叶分析,估算出功率级锯齿波功率损耗的有效纹波电流电阻(Rac),所得到的等效功率损耗交流电阻,几乎等于仿真基本开关频率成分交流电阻的1.1倍。

图2:仿真和测量PCB核心电压主回路频变电阻(交流电阻)

总变换器损耗模型与测量

总开关损耗测量在单相DrMOS核心电压评估板上进行,利用推荐的150nH电感器,在Vin = 12V和Vout = 1.8V的典型工作条件下,频率为700kHz时的峰-峰纹波电流 (Ipp) 约为14.5A。同时,在400kHz至2.5MHz的频率范围内,分析了变换器在15A负载电流下的功率损耗,在700kHz时提取损耗成分(图3和图4)。通过对设备的测量和仿真,估算出MOSFET损耗。电感的绕组交流电阻损耗是基于Q3D的仿真数据,而电感的磁芯损耗和交流电阻损耗则是基于供应商提供的规格书数据。输出POSCAP ESR损耗,是依据陶瓷电容与POSCAP的功率损耗差异而来。PCB 交流电阻损耗来自上述Q3D的频变电阻分析。其中,PCB 交流电阻损耗,约占纹波电流电阻损耗的25%,大约为700 kHz频率下峰值效率工作总损耗的5%。

图3:700 kHz下的功率损耗成分图

总功率损耗可用公式(3)表示:

(3)

其中,A为直流功率损耗,B × f为比例×频率的MOSFET开关功率损耗,C × f −1.5为纹波电流电阻功率损耗。根据公式计算,峰值效率频率出现在比例×频率MOSFET功率损耗为纹波电流功率损耗的1.5倍时,此时可得到最小总功率损耗。在DrMOS核心电压操作条件下,此穿越频率发生在约700kHz时(图4)。

图4:功率损耗与频率的关系

结论

PCB主回路纹波电流电阻损耗可能是总体损耗的重要组成部分,它大大限制了峰值效率,使其低于传统分析估算方法得出的数值。我们可以使用Q3D工具提取电阻参数,并合理地估算出这些损耗,以便提高效率和频率估算准确度。还可发现,峰值效率的工作频率高于没有PCB 交流电阻损耗因素的频率值。由于MPS将驱动器和MOSFET集成在一起,使得它的DrMOS设备本身就具有更高的频率,从而也减轻这种损耗因素。

1Gregory Sizikov, Edy G. Fridman, and Michael Zelikson, “Efficiency Optimization of Integrated DC-DC Buck Converters,” IEEE ICECS, 2010, pp. 1208-1211.

2Volkan Kursun, Siva G. Narendra, Vivek K. De, and Eby G. Friedman, “Efficiency Analysis of High Frequency Buck Converter for On-Chip Integration with a Dual-VDD Microprocessor,” ESSCIRC, 2002, 743-746.

3Yuancheng Ren, Ming Xu, Jinghai Zhou, Fred C. Lee, “Analytical Loss Model of Power MOSFET,” IEEE, Power Electronics, Vol.21 NO.2, 2006 , pp. 310-319.

4Wison Eberle, Zhiliang Zhang, Yan-Fei Liu, and Paresh C. Sen, “A Practical Switching Loss Model for Buck Voltage Regulators,” IEEE, Power Electronics, Vol.24 NO.3, 2009 , pp. 700-712.

5Yali Xiong, Shan Sun, Hongwei Jia, Patrick Shea, and Z. John Shen, “New Physical Insights on Power MOSFET Switching Losses,” IEEE, Power Electronics, Vol.24 NO.2, 2009 , pp. 525-531.

编辑:hfy

-

pcb

+关注

关注

4322文章

23120浏览量

398478 -

开关电源

+关注

关注

6467文章

8350浏览量

482477

发布评论请先 登录

相关推荐

PCB 主回路交流电阻的模型、仿真和测量

PCB 主回路交流电阻的模型、仿真和测量

评论