在电气和电子工程中,开关是一种能够“接合”或“断开”电路的组件,从而中断电流或将电流从一个导体转到另一个导体。正如工程师们所知,开关有许多不同的类型,包括拨动开关、摇臂开关、按钮开关、微动开关和限位开关、磁性开关和磁簧开关以及继电器等。所有开关都有一个共同点:就是有抖动。这就是它们的工作方式。

通常情况下,这种抖动对电路几乎没有影响,但如果是数字电路,只要速度足够快,就能检测到多次抖动并对之作出响应,并因此造成严重后果。工程师的任务就是要避免或减轻这种抖动的影响,或者给开关“去抖动”。虽然业界长期以来一直都在采取硬件去抖动,但直到最近才转向基于软件的去抖动方式。然而,在某些情况下,硬件去抖动是更好的选择。

本文解释了什么是抖动,并讨论了去抖动的软件和硬件方法。然后用实例证明硬件去抖动是更好的选择,并阐述如何实现该方法。最后以来自 NKK Switches、ON Semiconductor、Texas Instruments、Maxim Integrated 和 LogiSwitch 等公司的产品为例,展示了几个具体的开关器件和硬件去抖动组件。

什么是开关抖动?

当开关或继电器翻转或拨动,或者每次设备改变状态时,人们通常视之为瞬间单一反应,但实际上可能涉及 100 个以上的接合或断开动作,这些动作持续几千分之一秒,最后接触才会稳定下来。

例如像 NKK 的 M2011SS1W01 这样的单刀单掷 (SPST) 常开 (NO) 面板安装拨动开关。假设该开关的一侧(可视为输入端)连接到地(0 伏),而另一侧(在本例中为输出端)通过上拉电阻 (R1) 连接到 5 伏电源(显示为 +ve)(图 1)。

观察到开关抖动在开关启动(闭合)和停用(打开)时都可能发生。有时抖动可能会全程跨越两个电源轨,即不是逻辑 0 就是逻辑 1 状态。在这种情况下,这些都是“干净”的抖动。相比之下,如果信号只达到一个中间电压,这些被称为“脏”抖动。

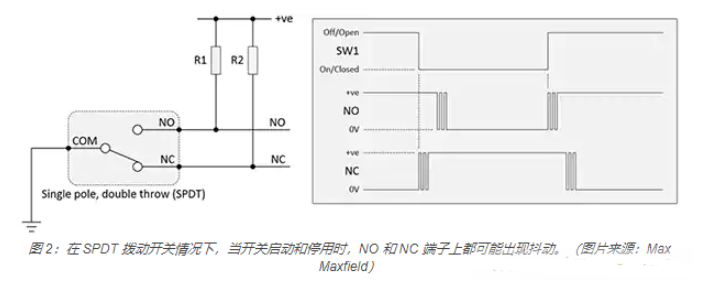

对于像 NKK 的 M2012SS1W01-BC 这样的单刀双掷 (SPDT) 面板安装拨动开关,在常开 (NO) 和常闭 (NC) 端子上都可能发生抖动(图 2)。在这种情况下,为了简单起见,只显示了“干净”的抖动。

在许多情况下,这种信号抖动持续是没有影响的。当一个开关连接到一个电子设备上时,如果这个设备的速度足够快,可以检测到多次抖动并做出响应,那么就会引起问题。需要做的是,在电子设备对开关发出的信号进行响应前就对其进行去抖动。

软件与硬件去抖动比较

在 20 世纪 60 年代和 70 年代,开关去抖动采用了各种硬件技术,从与 SPST 开关一起使用的简单电阻电容 (RC) 延迟电路到更复杂的置位/复位 (SR) 锁存器功能。

最近,由于许多系统都采用了微处理器单元 (MPU) 或微控制器单元 (MCU),因此使用软件技术来消除来自任何开关的信号已经变得很普遍。然而,软件去抖动并不总是最好的方法。有一些采用小型、低性能、存储空间有限的处理器的应用,其代码空间和/或时钟周期有限,就无法实现去抖动例程。在这些情况下,硬件实现可能是一个更好的解决方案。

另外,很多软件开发人员对开关的物理特性并不熟悉,比如开关的去抖动特性除了在不同的激活方式下会有不同的变化外,还可能受到温度、湿度等环境条件的影响。

软件开发人员缺乏开关专业技术,加上现有关于开关抖动的文献往往是混乱和矛盾的,进一步加剧了这一问题的严重性。例如,我们通常读到开关在激活或停用后 1 毫秒 (ms) 就会停止抖动。然而,知名嵌入式系统专家 Jack Ganssle 对各种类型的开关进行了实证测试,将每个开关激活 300 次,并记录下了触点打开和关闭的最小和最大抖动量。据其报告记录,平均抖动持续时间为 1.6 ms,最大抖动持续时间为 6.2 ms。一些工业和军事“最佳实践”建议在初始激活后等待 20 ms,然后再假设开关已经停止抖动;另一些人则主张在最终检测到抖动后等待 20 毫秒再触发任何动作。

此外,还有很多简单的无处理器的系统也需要消除开关抖动。举几个这类系统的例子:驱动七段式显示器对来自继电器的脉冲进行计数的二进制计数器;用作门或闸电机控制装置的555 单次定时器的触发输入;以及采用键控输入的基于寄存器的有限状态机 (FSM)。还有电子微调电位器 (Pot),其值是用开关输入(加、减,有时是存储)修改的,这时开关抖动就会有问题。

所有这些例子都清楚地表明,掌握一些如何进行硬件去抖动的知识对任何设计人员或开发人员都是有用的。

用 RC 网络对 SPST 开关进行硬件去抖动

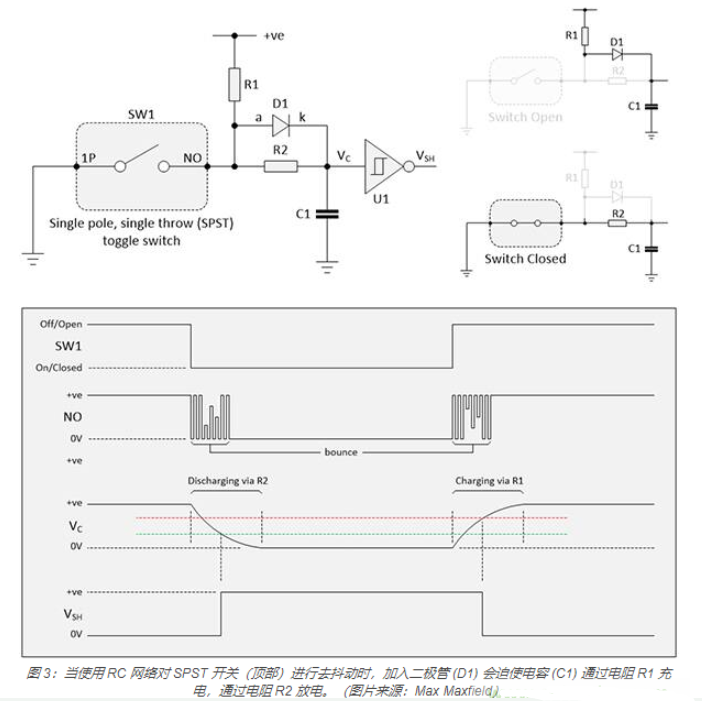

一个最简单的基于硬件的开关去抖动方案就是将电阻电容 (RC) 网络与 SPST 开关结合起来使用。这种电路有很多变型。其中一个较通用的实现方案是采用两个电阻和一个二极管(图 3)。

当开关启动(闭合)时,电容 C1 通过电阻 R2 放电。如果这个电路中省略了二极管 D1,那么当开关停用(打开)时,C1 将通过电阻 (R1 + R2) 充电。但是,D1 的存在意味着 C1 只能通过 R1 充电。

在某些情况下,人们只关注开关的激活(即触发动作发生),在这种情况下,D1 可以省略。但是,如果要在开关被激活和停用时触发动作,并且要考虑将延迟降到最低,建议增加 D1。

观察电容器电压 VC 所表现出的指数充放电曲线。将此信号直接送入下游数字逻辑功能的输入端并不是一个好主意,因为下游数字逻辑功能不会喜欢看到一个在“好”的逻辑 0 和逻辑 1 值之间的未定义区域徘徊的信号。相反,该信号应被送入带有施密特触发器输入的缓冲器的输入端。此外,通常要使用反相缓冲器,如 Texas Instruments 的 CD74HC14M96 的一个通道,因为反相功能的切换速度比非反相功能快。

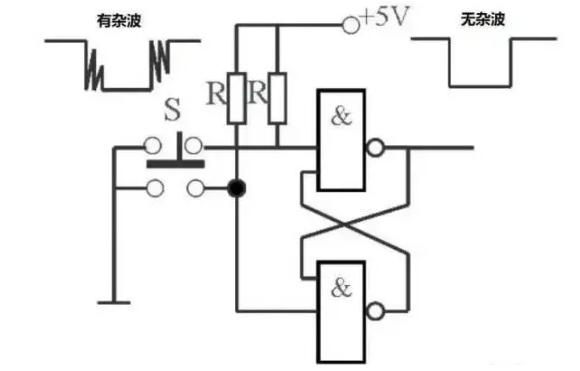

用 SR 锁存器对 SPDT 开关进行去抖动

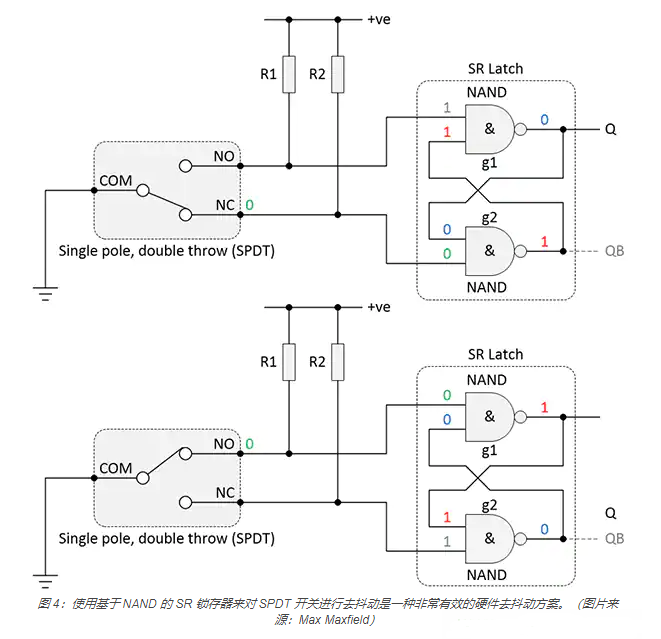

在 SPDT 开关情况下,常见的硬件去抖动方案是采用 SR 锁存器。自从 20 世纪 60 年代 IBM 等公司将这种技术应用于大型计算机的开关面板后,这种方法就被认为是简单硬件去抖动解决方案中的精华。这种锁存器可以使用两个背对背的双输入 NAND 门形成;例如,采用 Texas Instruments 的 SN74HC00DR 四路双输入 NAND IC 的两个通道(图 4)。

当开关的 NC 端子接地时,如图 4 上半部分所示,这将迫使门 g2 的输出变为逻辑 1。反过来,门 g1 输入端的两个逻辑 1 又迫使其输出端变为逻辑 0。相比之下,当开关的 NO 端子接地时,如图 4 下半部分所示,这就迫使门 g1 的输出变为逻辑 1。反过来,门 g2 输入端的两个逻辑 1 又迫使其输出端变为逻辑 0。

这个电路之所以工作得这么好,是因为当它的两个输入都处于不活动的逻辑 1 状态时,SR 锁存器会记住它以前的值。请记住,如图 2 所示,当一个 SPDT 开关被拨动时,在该时刻,无论其哪一个端子接地,都会发生抖动。由于这些抖动信号在其原值(逻辑 0)和新值(逻辑 1)之间,所以对 SR 锁存器的当前状态没有影响。只有在这个端子停止抖动后,其相对的端子才开始抖动,此时 SR 锁存器才会改变其状态。

用专用设备对 SPST 开关进行去抖动

前面的解决方案有一个问题,就是很多设计者喜欢使用 SPST 开关,因为它们的成本普遍低于 SPDT。市场上有很多有名的专用 SPST 去抖动器件,如 ON Semiconductor 的 MC14490DWG 和 Maxim Integrated 的 MAX6818EAP+T。

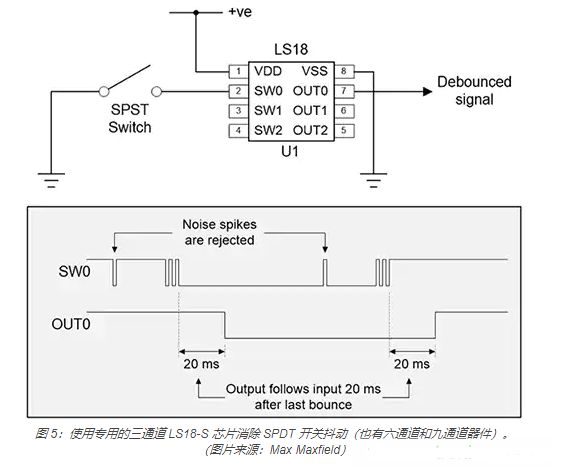

另一家制造商 LogiSwitch 也提供了一套三通道、六通道和九通道的去抖动解决方案,同时采用通孔和表面贴装 (SMD) 封装。例如,考虑使用 LogiSwitch LS18-S 器件的电路(图 5)。

与 LogiSwitch 产品家族所有成员一样,LS18-S 支持 2.5 至 5.5 伏的工作电压范围(供电电压值不影响器件的响应时间)。此外,与其他一些专用 IC 解决方案不同,LogiSwitch 去抖动器件不需要任何额外的元件,如外部时钟、RC 时序网络或输入或输出上的上拉电阻。

LS18-S 采用 LogiSwitch 专有的自适应 NoBounce(无抖动)技术,实现了高水平抗噪能力。在启动或终止一个周期时禁止小于 20 ms 持续时间的噪声尖峰,然后在开关激活和释放的最后一次抖动后,无论抖动持续时间长短,输出都会延迟 20 毫秒。

结语

开关有很多不同的类型,包括拨动开关、摇臂开关和按钮开关,这些开关都可能会抖动。如果开关抖动不得到缓解,就会导致微处理器和其他电子电路将一次开关激活视为多个事件。

人们常常利用微控制器中运行的软件对开关发出的抖动信号进行消抖。如上所述,虽然这是一种低成本的解决方案,但它可能并不是所有情况下的最佳选择。这些情况包括:系统基于性能和存储空间有限的微控制器,软件开发人员缺乏开关相关问题专业知识,或者系统实现没有微控制器。

作为替代选择,我们可以使用各种方法在硬件中进行去抖动,具体方法包括电阻电容网络、SR 锁存器以及专用集成电路。

(来源:Digi-Key,作者:Clive "Max" Maxfield)

编辑:hfy

-

微控制器

+关注

关注

48文章

7679浏览量

152328 -

继电器

+关注

关注

132文章

5368浏览量

149795 -

锁存器

+关注

关注

8文章

918浏览量

41707 -

Digi-Key

+关注

关注

4文章

135浏览量

52757

发布评论请先 登录

相关推荐

RAID 5 硬件与软件 RAID 的区别

如何实现软件的emulate功能 emulation和虚拟化的区别是什么

raid 硬件与软件的区别

SRC4392怎么实现硬件控制?

抖动定义和测量

两种常见的硬件消抖实现方式

CDR电路设计与抖动管理

抖动的概念和类型 量化时域抖动、随机抖动和频域抖动的方法

如何实现软件与硬件的开关抖动设计

如何实现软件与硬件的开关抖动设计

评论