在线调试

在线调试也称作板级调试,它是将工程下载到FPGA芯片上后分析代码运行的情况。有人会以为,我们不是已经做了仿真了,甚至是时序仿真都通过了,还会存在问题么?在实际中,存在这么些情况我们需要用到在线调试:

仿真不全面而没有发现的FPGA设计错误。很多情况下,由于太复杂,无法做到100%的代码覆盖率;

在板级交互中,存在异步事件,很难做仿真,或者仿真起来时间很长,无法运行;

除了本身FPGA外,还可能存在板上互连可靠性问题、电源问题和IC之间的信号干扰问题,都可能导致系统运行出错;

其他潜在问题:

在线调试的方式主要有两种,一种是利用外部测试设备,把内部信号传送到FPGA针脚上,然后用示波器或者逻辑分析仪观察信号;另一种就是利用嵌入式逻辑分析仪,在设计中插入逻辑分析仪,利用JTAG边缘数据扫描和开发工具完成数据交互。

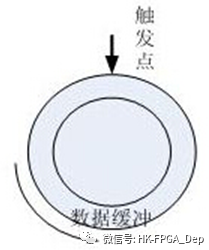

嵌入式逻辑分析仪的原理相当于在FPGA中开辟一个环形存储器,存储器的大小决定了能够查看的数据的深度,是可以人为设定的,但是不得超出资源。在FPGA内部,根据设置的需要查看的信号节点信息和驱动的采样时钟,对信息进行采样,并放置到设定的存储空间里,存储空间是环形的,内容随时间更新。然后通过判断触发点来检查采集数据,一旦满足触发条件,这个时候会停止扫描,然后将触发点前后的一些数据返回给PC端的测试工具进行波形显示,供开发者进行调试。

目前的调试工具都是和本身的FPGA开发平台挂钩的,不同FPGA厂商都会有开发软件平台,嵌入式逻辑分析仪也就不同。Altera 厂家提供的是SignalTapII,而 Xilinx厂家提供的是 ChipScope,这些工具的具体使用在后面工具中详解。

当然这里除了嵌入式逻辑分析仪外,各厂家还提供了一些其他的在线调试工具,例如SignalProbe等等,但是或多或少的用的人不是很多,有兴趣的可以找到该功能使用的说明手册。

配置及固化

好了,到了我们最后一个环节就可以完成FPGA的流程了。这一部分我们分四个小节来讲,首先是针对大家很多人不是太清楚的FPGA配置过程安排的,随后一节为了更加深理解,举了altera 的FPGA叙述配置全过程,第三小节是探讨FPGA主要的配置模式,最后一节就是针对这些配置模式展开的对比选择探讨。

FPGA配置过程

在FPGA正常工作时,配置数据存储在SRAM中,这个SRAM单元也被称为配置存储器(configure RAM)。由于SRAM是易失性存储器,因此在FPGA上电之后,外部电路需要将配置数据重新载入到芯片内的配置RAM中。在芯片配置完成之后,内部的寄存器以及I/O管脚必须进行初始化(initialization),等到初始化完成以后,芯片才会按照用户设计的功能正常工作,即进入用户模式。

FPGA上电以后首先进入配置模式(configuration),在最后一个配置数据载入到FPGA以后,进入初始化模式(initialization),在初始化完成后进入用户模式(user-mode)。在配置模式和初始化模式下,FPGA的用户I/O处于高阻态(或内部弱上拉状态),当进入用户模式下,用户I/O就按照用户设计的功能工作。

举例——altera FPGA配置全过程

一个器件完整的配置过程将经历复位、配置和初始化等3个过程。FPGA正常上电后,当其nCONFIG管脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空,并且所有I/O处于高阻态,FPGA的状态管脚nSTATUS和CONFIG_DONE管脚也将输出为低。当FPGA的nCONFIG管脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。随之,芯片将释放漏极开路(open-drain)输出的nSTATUS管脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。在配置之前和配置过程中,FPGA的用户I/O均处于高阻态。

在接收配置数据的过程中,配置数据由DATA管脚送入,而配置时钟信号由DCLK管脚送入,配置数据在DCLK的上升沿被锁存到FPGA中,当配置数据被全部载入到FPGA中以后,FPGA上的CONF_DONE信号就会被释放,而漏极开路输出的CONF_DONE信号同样将由外部的上拉电阻拉高。因此,CONF_DONE管脚的从低到高的跳变意味着配置的完成,初始化过程的开始,而并不是芯片开始正常工作。

INIT_DONE是初始化完成的指示信号,它是FPGA中可选的信号,需要通过Quartus II工具中的设置决定是否使用该管脚。在初始化过程中,内部逻辑、内部寄存器和I/O寄存器将被初始化,I/O驱动器将被使能。当初始化完成以后,器件上漏极开始输出的INIT_DONE管脚被释放,同时被外部的上拉电阻拉高。这时,FPGA完全进入用户模式,所有的内部逻辑以及I/O都按照用户的设计运行,这时,那些FPGA配置过程中的I/O弱上拉将不复存在。不过,还有一些器件在用户模式下I/O也有可编程的弱上拉电阻。在完成配置以后,DCLK信号和DATA管脚不应该被浮空(floating),而应该被拉成固定电平,高或低都可以。

如果需要重新配置FPGA,就需要在外部将nCONFIG重新拉低一段时间,然后再拉高。当nCONFIG被拉低后,nSTATUS和CONF_DONE也将随即被FPGA芯片拉低,配置RAM被清,所有I/O都变成三态。当nCONFIG和nSTATUS都变为高时,重新配置就开始了。

配置模式

这一块分成两部分,一部分是在线调试配置,另一块是固化,即将工程配置到相应存储单元中,上电后,通过存储在存储器中的内容配置FPGA。

1)在线配置

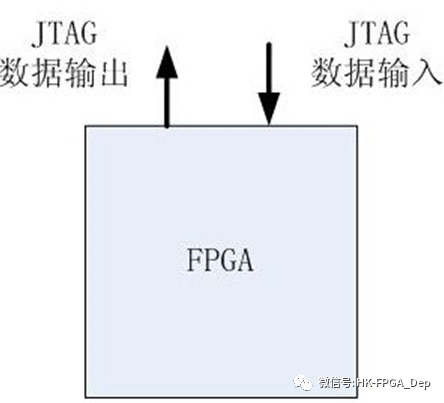

第一部分在线调试配置过程是通过JTAG模式完成的,如下图所示,在JTAG模式中,PC和FPGA通信的时钟为JTAG接口的TCLK,数据直接从TDI进入FPGA,完成相应功能的配置。

JTAG接口是一个业界标准接口,主要用于芯片测试等功能。FPGA基本上都可以支持JTAG命令来配置FPGA的方式,而且JTAG配置方式比其他任何方式优先级都高。JTAG接口由4个必需的信号TDI, TDO, TMS和TCK以及1个可选信号TRST构成,其中:

TDI,用于测试数据的输入;

TDO,用于测试数据的输出;

TMS,模式控制管脚,决定JTAG电路内部的TAP状态机的跳变;

TCK,测试时钟,其他信号线都必须与之同步;

TRST,可选,如果JTAG电路不用,可以将其连到GND。

2)固化

第二部分固化程序到存储器中的过程可以分为两种方式,主模式和从模式。主模式下FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程;从模式下则由外部计算机或控制器控制配置过程。主、从模式从传输数据宽度上,又分别可以分为串行和并行。

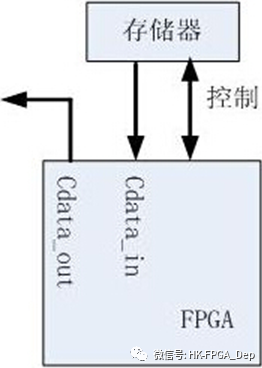

I)主串模式

主串模式是最简单的固化模式,如下图所示,这个模式过程不需要为外部存储器提供一系列地址。它利用简单的脉冲信号来表明数据读取的开始,接着由FPGA提供给存储器时钟,存储器在时钟驱动下,将数据输入到FPGA Cdata_in端口。

II)主并模式

主并模式其实和主串模式的一样机理,只不过是在主串的基础上,同周期数内传送的数据变成8位,或者更高,如下图。这样一来,主并行相比主串行的速度要优先了。现代有些地方已采用这种方式来配置FPGA的了。

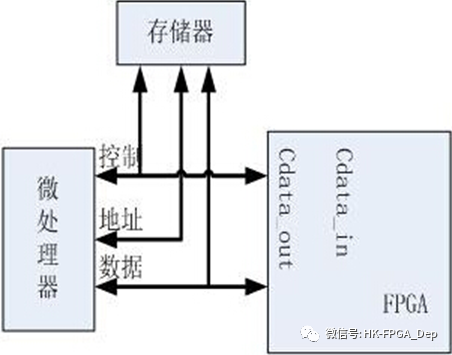

III)从并模式

从上面看到,主模式下的连接还是很简单的。但是有时候,系统可能用其他微处理器来对FPGA进行配置。这里的微处理器可以指FPGA内嵌的处理器,比如说Nios。微处理器控制着何时配置FPGA,从哪读取配置文件。如下图,这种方式的优点是处理器可以灵活随时变更FPGA配置,同时配置的速度也快。微处理器先从外部存储设备里读取一个字节的数,然后写到FPGA里。

IV)从串模式

理解了从并模式,从串模式就不用很多解释了,它的特点就是节约FPGA管脚I/O。

V)多片级联

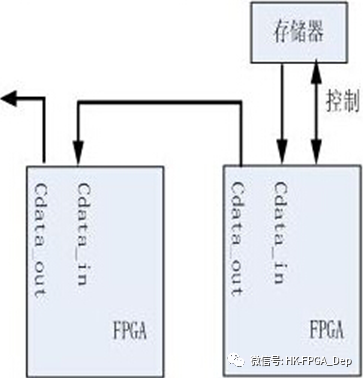

多片模式有两种,一种是采用菊花链的思想,多片FPGA共享一个存储器,另外一个是可以使用其他存储器配置不同的FPGA。如果所示是一个共享型的结构,显示启动了。这里分主FPGA和从FPGA,主FPGA和存储器是使用串行主模式来配置,而后面那个的配置是通过第一配置好的FPGA上微处理器进行协调的。

模式选择

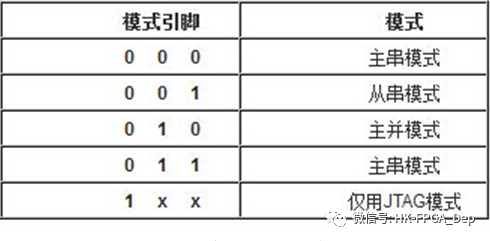

现今FPGA应该可以支持上面五种配置模式,是通过3个模式引脚来实现的,具体的映射如下表,在今后模式还是有可能增加的。

在PS模式下,如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号。一般平时调试时不会把配置芯片焊上的,这时候用缆线下载程序。只有在调试完成以后,才把程序烧在配置芯片中, 然后将芯片焊上.或者配置芯片就是可以方便取下焊上的那种。这样出了问题还可以方便地调试.。

对FPGA芯片的配置中,可以采用AS模式的方法,如果采用EPCS的芯片,通过一条下载线进行烧写的话,那么开始的”nCONFIG,nSTATUS”应该上拉,要是考虑多种配置模式,可以采用跳线设计。让配置方式在跳线中切换,上拉电阻的阻值可以采用10K一般在做FPGA实验板的时候,用AS+JTAG方式,这样可以用JTAG方式调试,而最后程序已经调试无误了后,再用AS模式把程序烧到配置芯片里去。

责任编辑人:CC

-

FPGA

+关注

关注

1664文章

22545浏览量

640414 -

FPGA开发

+关注

关注

1文章

56浏览量

15906

原文标题:详解FPGA开发在线调试&配置及固化

文章出处:【微信号:HK-FPGA_Dep,微信公众号:FPGA技术支持】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA实战演练逻辑篇69:基于FPGA的在线系统调试概述

Xilinx FPGA在线更新配置数据交流

玩转Zynq连载5——基于Vivado的在线板级调试概述

FPGA在线配置模块和自动测试模块实现过程

可在线升级的FPGA并行配置方法的实现

简化Xilinx和Altera FPGA调试过程

简化FPGA配置设计过程

FPGA开发板使用和配置方式

STM8S 使用IAR在线调试配置

7.22在线研讨会 | 基于高层级设计的FPGA开发快速迭代

FPGA开发在线调试和配置过程

FPGA开发在线调试和配置过程

评论