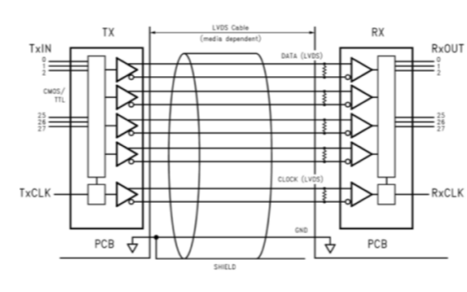

什么是LVDS,LVDS的全称是Low-Voltage Differential Signaling ,即低电压差分信号。LVDS可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。

1、LVDS的特点和分类

LVDS为克服以TTL电平方式传输的高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS是利用低电压差(典型值为350 mV)进行编码信息的。

LVDS信号的分为单路6位LVDS,双路6位LVDS,单路8位LVDS和双路8位LVDS,特点对比如下表:

我们常用的是HDMI高清接口,那么LVDS与HDMI又有哪些区别呢。

它们都是高清输出接口,LVDS由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

HDMI的TMDS是3.3V,而DDC电路的电平则是5V。传统的TTL驱动电平带来的噪声和功耗相对较大,要是对产品的EMI和EMC要求比较严格,则应该优选LVDS接口。

LVDS的应用

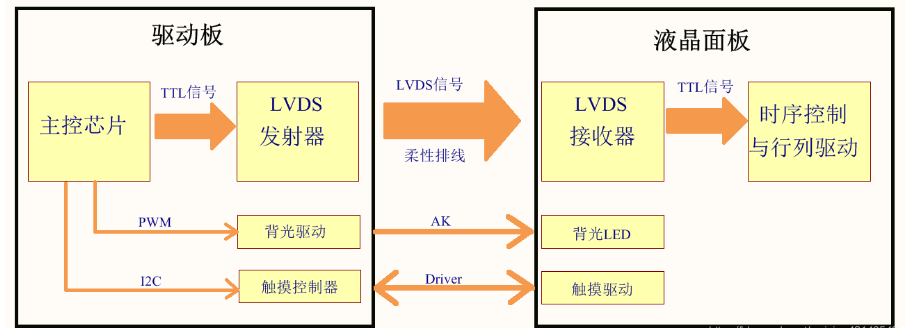

这里来看一个LVDS应用的例子:

整个应用分为LVDS输出驱动板和LVDS接收液晶面板,一般主控芯片内部没有集成的LVDS发射模块,只提供6或8 bit RGB接口,传输的是TTL电平,这时候需要加一块TTL转LVDS的转换芯片,然后将LVDS信号传输给液晶面板。液晶面板的LVDS接收器再对信号做转换处理并显示。

另外需要给液晶面板提供液晶的背光,背光电路一般放在驱动板,主控通过PWM信号对面板背光进行调节。若液晶面板带触摸功能,还需要设计触摸控制电路,触摸控制器与主控通过I2C通信,再去驱动液晶面板。

那么对于产品设计,LVDS接口有单6,双6,单8,双8之分,我们怎么选LVDS接口呢?经过咨询相关屏幕厂家,得到以下回复。

也就是说,选接口是由屏幕分辨率决定的,你选的屏幕分辨率高了,就得用高位数的,毕竟高分辨率要求基色信号的位数越多,才能在屏幕上显示更多色彩。

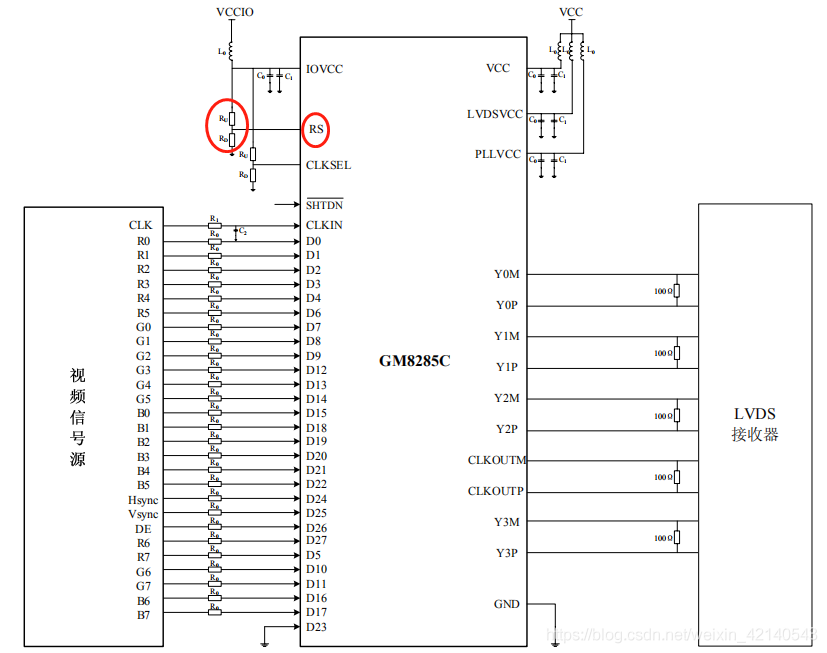

上面是不集成LVDS的主控的应用方案,如全志的H6,显示接口只有6bit 的RGB接口和HDMI接口,无LVDS接口。但像性能更强大一点的全志T3和瑞芯微RK32x8平台等,就内部集成专门的LVDS接口,不用再桥接一片转换IC。

在实际应用中,通常我们可以调节LVDS转换芯片的RS管脚配置去控制信号的摆幅,低摆幅LVDS输出可以进一步降低系统的EMI,并减小芯片功耗。

关于LVDS Layout

下面介绍一下关于LVDS的PCB 板布线时需要注意的点:

1) 由于差分线较多并为了方便做阻抗匹配,PCB 至少采用四层板设计;

3) 每组电源都需要通过磁珠进行隔离,且都要增加电源滤波电容;

4) PCB 板尽可能铺设大面积的 GND ;

5) LVDS 输出差分信号走线设计成 100Ω差分匹配,走线尽可能保持等长;

6) LVDS 输出差分信号正负通道间隔 S1 尽可能的小;

7) LVDS 各输出差分信号通道间的间隔至少要大于 2 倍 S1;

8) 100Ω终端电阻要尽可能的靠近 LVDS 接收器输入端口;

9) LVDS 输出差分信号通路尽可能的少用通孔,且走线避免设计成 90°弯角。

责任编辑人:CC

-

FPGA

+关注

关注

1629文章

21743浏览量

603555 -

接口

+关注

关注

33文章

8610浏览量

151215 -

lvds

+关注

关注

2文章

1043浏览量

65818

原文标题:FPGA | LVDS屏幕接口的应用

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

简易USB与LVDS接口转换器

AD9684与FPGA用LVDS模式接口互联时,FPGA端如何使用?

基于FPGA的LVDS接口应用

LVDS高速ADC接口_Xilinx FPGA实现

LVDS在FPGA中的使用教程之LVDS的介绍

具有LVDS输出的LTM9011 ADC的AN147-Altera Stratix IV FPGA接口

wp02-将凌力尔特公司的DDR LVDS ADC与Altera Stratix IV FPGA接口

LVDS接口有哪些分类

高速ADC与FPGA的LVDS数据接口中避免时序误差的设计考虑

基于FPGA的LVDS屏幕接口应用

基于FPGA的LVDS屏幕接口应用

评论