晶振为什么不能放置在PCB边缘?现象描述:

某塑料外壳产品,带一根I/O 电缆,在进行 EMC 标准规定的辐射发射测试时发现辐射超标,具体频点是 160 MHz。需要分析其辐射超标的原因,并给出相应对策。

原因分析:

该产品只有一块 PCB,其上有一个频率为 16MHz 的晶振。由此可见,160MHz 的辐射应该与该晶振有关(注意:并不是说辐射超标是晶振直接辐射造成的,可能是倍频产生的)。图 1 所示的是该产品局部PCB 布局实图,从图 1 中可以明显看到,16MHz 的晶振正好布置在PCB 的边缘。

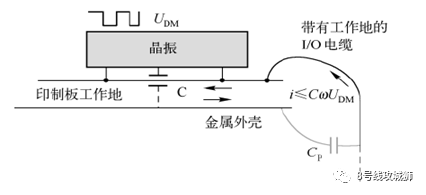

图 1 该产品局部 PCB 布局实图 当一个被测产品置于辐射发射的测试环境中时,被测产品中的高速信号线或高速器件与实验室中参考接地板会形成一定的容性耦合(本产品中晶振属于高速器件,其对应的上升下降沿较陡,晶振在工作时,其引线部分的 dU/dt 比较大,属于强干扰源,在辐射发射测试中是隐患),即被测产品中的高速信号线或高速器件与实验室中参考接地板之间存在电场分布或寄生电容,这个寄生电容很小(如小于0.1pF),但是还是会导致产品出现一种共模辐射,产生这种共模辐射的原理如图 2 所示。在图2 中,晶振壳体上的电压(外壳不接大地的晶振)或晶振时钟信号引脚上的电压Udm 和参考接地板之间产生寄生回路,回路中的共模电流通过电缆产生共模辐射,共模辐射电流 Icm ≈C * w * Udm,其中,C 为 PCB 中信号印制线与参考接地板之间的寄生电容, 约在十分之一皮法到几皮法之间;Cp 为参考接地板与电缆之间的寄生电容,约为 100 pF;w 为信号角频率。共模辐射电流 Icm 会在几微安到数十微安之间,经分析可知,电缆上流过这个数量级的共模电流已足够造成辐射发射测试的超标。

图 2 晶振与参考接地板之间的容性耦合导致辐射发射原理

为什么晶振布置在 PCB 边缘时会导致辐射超标,而向板内移动后,可以使辐射发射测试通过呢?

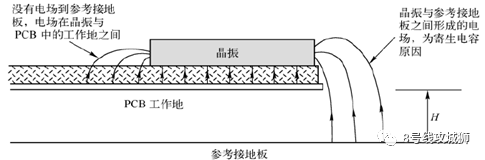

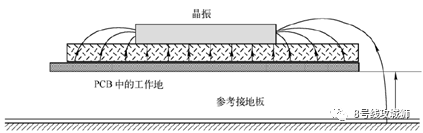

从以上分析已经可以看出,晶振与参考接地板之间的耦合导致电缆共模辐射的实质是晶振与参考接地板之间的寄生电容,也就是说这个寄生电容越大,晶振与参考接地板之间的耦合就越厉害,流过电缆的共模电流也越大,电缆产生的共模辐射发射也越大;反之辐射发射就越小。那这个寄生电容的实质是什么呢,实际上这个晶振与参考接地板之间的寄生电容就是由于晶振与参考接地板之间存在的电场分布,当两者之间的电压差恒定时,两者之间电场分布越多,两者之间的电场强度就越大,两者之间寄生电容也会越大。当晶振布置在 PCB 的边缘时,晶振与参考接地板之间的电场分布示意图如图 3 所示。当晶振布置在 PCB 中间,或离 PCB 边缘较远时,晶振与参考接地板之间的电场分布示意图如图4 所示。

图 3 PCB 边缘的晶振与参考接地板之间的电场分布示意图

从图 3 和图 4 的比较可以看出,当晶振布置在 PCB 中间,或离PCB 边缘较远时,由于 PCB 中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地(GND)之间,即在 PCB 内部,分布到参考接地板的电场大大减小,即晶振与参考接地板之间的寄生电容大大减小。这时也不难理解为何晶振布置在PCB 边缘时会导致辐射超标,而向板内移动后,辐射发射就降了。

图 4 PCB 中间的晶振与参考接地板之间的电场分布示意图

处理措施:

方案一:将晶振内移,使其离 PCB 地平面边缘至少有1 cm 以上的距离,并在 PCB 表层离晶振 1 cm 的范围内敷铜,同时把表层的铜通过过孔与 PCB 地平面相连。

方案二:不改电路板的情况下选择放弃使用外部晶振,在软件中屏蔽外部晶振,采用单片机内部晶振。

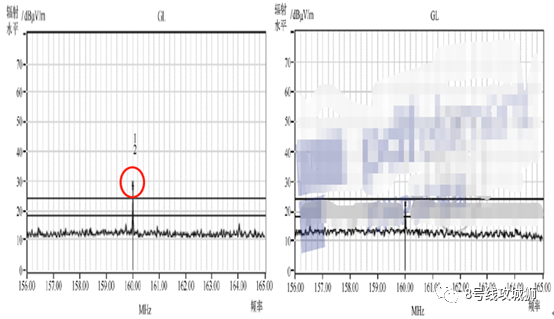

本次实验采用方案一,经过修改后的测试结果有明显的改善,如下图 5 所示,左右分别是整改前与整改后的整改前后辐射发射测试频谱图,可以明显看出整改后,辐射发射有明显的改善。

图 5 整改前后辐射发射测试频谱图

思考与启示

(1) 高 dU/dt 的印制线或器件与参考接地板之间的容性耦合,会产生 EMI 问题,敏感印制线或器件布置在 PCB 边缘会产生抗扰度问题;

(2) 杜绝高 dU/dt的印制线或器件放置在PCB 的边缘,如果设计中由于其他原因一定要布置在 PCB 边缘,那么可以在晶振印制线边上再布一根工作地(GND)线,并注意一定要在包地线上间隔一段距离就打过孔,把晶振部分围起来,如下图6 示意;

图 6 晶振包地示意图

其理论依据同法拉第电笼:由于金属的静电等势性,可以有效屏蔽外电场的电磁干扰。法拉第屏罩无论被加上多高的电压内部也不存在电场。而且由于金属的导电性,即使笼子通过很大的电流,内部的物体通过的电流也微乎其微。在面对电磁波时,可以有效的阻止电磁波的进入。 由于法拉第屏罩的静电屏蔽原理,在汽车、飞机等交通工具中的人是不会被雷击的。同样,也是因为法拉第屏罩的原理,有金属外皮的同轴电缆也可以不受干扰地传播讯号。如果电梯内没有中继器的话,那么当电梯关上的时候,里面任何电子讯号也收不到。为防止干扰,一些精密仪器需放在笼内才可进行运作或量测。或者也可以再开一个洞,例如金属机身构造的的智能手机。

(3) 消除一种误解:不要认为辐射是由晶振直接造成的,事实上晶振个体较小,它直接影响的是近场辐射(表现为晶振与其他导体(如参考接地板)之间形成的寄生电容),造成远场辐射的直接因素是电缆或产品中最大尺寸与辐射频率波长可以比拟的导体;

(4)此外,将晶振外壳接地可以在一定程度上减少这种干扰叠加到系统上。

责任编辑人:CC

-

pcb

+关注

关注

4338文章

23289浏览量

403671 -

晶振

+关注

关注

34文章

3081浏览量

68996

原文标题:晶振为什么不能放置在PCB边缘?

文章出处:【微信号:gh_3a15b8772f73,微信公众号:硬件工程师炼成之路】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电磁兼容(EMC):晶振为什么不能放置在PCB边缘?

晶振不能放置在PCB边缘的原因?

晶振不能放置在PCB边缘的原因是什么

晶振为什么不能放置在PCB边缘?

晶振不能放置在PCB边缘的原因是什么

晶振不能放置在PCB边缘的原因是什么

评论