一、并行ADC

1.ADC简介

背景知识:模数转换器(Analog to digital Converter,简称ADC)是模拟与数字世界的接口,为了适应计算机、通讯、多媒体技术的飞速发展以及高新技术领域的数字化进程的不断加快,ADC正朝着低功耗、高速、高分辨率方向发展。目前市场化的ADC有很多种类型。

近年来,我国在有限的工艺水平条件下积极开展了对ADC的研究,并取得了令人鼓舞的成果,但是与国际水平相比尚有差距,电路结构设计也略显单调,折叠式、流水线型、E一△型结构鲜见报道。统计资料表明,8-12位精度范围的高速A/D转换器是应用最广泛、需求最迫切的品种,因此研制出我国具有自主知识产权的高速高精度、高速、低功耗的ADC具有十分重要的意义。目前市场化的ADC有多种结构,如并行(Flash,或称Parallel)A DC,逐次逼近型ADC、积分型ADC,压频变换型ADC以及流水线型ADC和Delta-Sigma型ADC等,其中后两种ADC是新发展起来的,这些ADC各有各的特点,根据不同的应用场合,选用的ADC的结构也是不同的。

2.基本原理

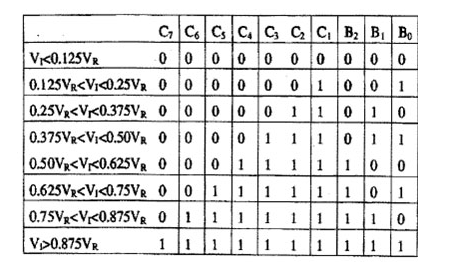

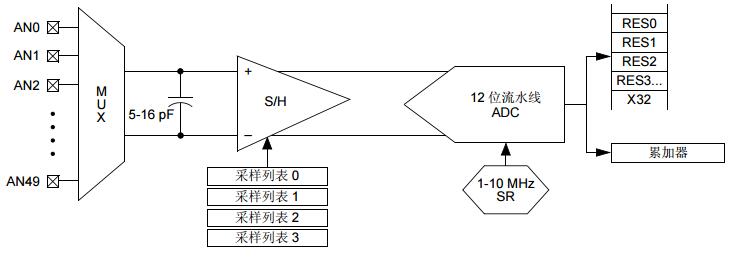

并行ADC转换器是目前速度很快的一种结构。该结构在设计思想很容易理解。一个n位的并行ADC包含2n-1个比较器和2n-1个参考电压值(对于一般的电压模电路,对于电流模电路,是参考电流值)。每一个比较器对输入信号采样并把输入信号与参考电压相比较,然后每一个比较器产生一位输出,表明输入信号比参考电压大还是小。2n-1个比较器输出通常称为温度计代码。该名称的来源是,如果把比较器的输出根据参考电压值的大小顺序排成一列,所有的1都在下面,所有的0都在上面,0和1的分界线表示信号值所在的范围,由于和水银温度计表示温度的方法相类似,因此称为温度计代码。如图为一个简单的3位并行ADC的结构图。译码器把比较器产生的温度计代码转换成如表所示的二进制代码。如图所示,所有的比较器并行工作。因此,转换速度仅仅受比较器的速度或采样速度的限制,所以并行ADC具有很高转换速度。

并行ADC的不足之处是硬件需求量大和对比较器偏移比较敏感。上面己经提到,一个n位的ADC需要2n-1个比较器。因此,高分辨率的并行ADC需要较大的芯片面积,这样电路的功耗也增加很多。此外,大量的比较器使采样电路要驱动很大的电容。n位分辨率的并行ADC要求比较器的偏移小于VR/2n。在较高的分辨率下,这要求比较器的偏移非常小。由于小偏移的比较器设计难度大、价格高,而且所用的比较器数量很大,因此超过8位的ADC很少用全并行结构。

二、流水线ADC和其它ADC的比较

1. 与逐次逼近型比较

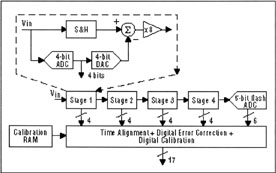

在逐次逼近(SAR)ADC中,用一个高速高精度比较器将模拟输入和前一次得到的模数转换结果通过DAC后的输出相比较,依次得到MSB到LSB的每一位,逐渐逼近输入模拟信号。SAR的这一串行工作方式从本质上限制了它的工作速度,最高约为几Msps左右,对更高的分辨率(14到16位)速度就更低。流水线ADC则不同,它是并行结构,各级同时以逐次方式得到1位或几位。虽然SAR中只需一个比较器,但是这个比较器必须高速工作(速率约为总位数×采样速率),其精度必须与ADC本身一样高,相反,流水线ADC内的比较器则不需要这一速度和精度。

当然,流水线ADC通常比相同位数的SAR占据更多的硅片面积。SAR只需一周期的延迟时间(=1/Fsample)就得到结果,而流水线ADC需要3或更多周期的延迟。与流水线ADC一样,12位精度以上的SAR也需要某些形式的校正和标定。

2. 与闪速型比较

尽管流水线ADC是并行机制,但它还需要DAC的精密转换和级间增益放大,因此存在建立时间问题。纯闪速型ADC不同,它有大量的比较器,每个比较器由宽带,低增益前置放大和锁存器构成。该前置放大器不像流水线ADC中的放大器,它只需提供增益,不需要线性和精度,只是比较器的触发点要很精确。因此流水线ADC速度根本比不上设计得很好的闪速型ADC.

虽然超高速8位闪速ADC(及各种合并/插值变体)的采样速率高达1.5Gsps(比如MAX104/MAX106/MAX108),但是很难找到10位的闪速ADC,特别是12位及高于12位的ADC还没有商用化。这是因为闪速ADC分辨率每增加1位,比较器数量就增加1倍,同时每个比较器的精度必须增加1倍。流水线ADC则不同,它的复杂性随分辨率线性增加,不是指数增加。

在相同的采样速率下,流水线ADC比闪速ADC消耗功率少得多。流水线ADC不易受比较器亚稳态的影响。闪速ADC中的比较器亚稳态会导致火花码错误(即ADC输出不可预测、不稳定结果的情况)。

3. 与Σ-Δ型比较

过采样/Σ-Δ型ADC多用于带宽限于22KHz以内的数字音响中。但是最近一些Σ-Δ型转换器已经在12到16位的分辨率下达到了1至2MHz的带宽。它们通常是高阶的Σ-Δ调制器(比如4阶或更高),同一个多位的ADC和多位的DAC一起工作,主要应用于ADSL。Σ-Δ型转换器无需校正/标定,即使是16到18位分辨率,也不需要模拟输入前的陡峭滚降的抗混叠滤波器,因为它的采样频率远远高于有效带宽,它由后端的数字滤波器来处理混叠问题。Σ-Δ型转换器的过采样本质还把模拟输入中的任何系统噪声“平均滤除”。

但是Σ-Δ型转换器是以牺牲速度换取分辨率的。每输出一次采样结果都需要对输入采样很多次(比如至少16次,甚至更多),这就需要Σ-Δ调制器中模拟元件的工作速率要比最终数据输出速率快很多。数字滤波器的设计比较繁琐,另外,它也占据了一些硅片面积。目前,最快的高分辨率Σ-Δ型转换器还达不到几MHz的带宽。像流水线ADC一样,Σ-Δ型转换器也有延迟。

责任编辑人:CC

-

adc

+关注

关注

98文章

6489浏览量

544415 -

流水线ADC

+关注

关注

0文章

3浏览量

1826

发布评论请先 登录

相关推荐

流水线ADC结构解析 流水线ADC和其它ADC的比较

一种流水线结构AD转换器的速度分析方法

流水线ADC

流水线ADC的行为级仿真

新型流水线实现高速低功耗ADC的原理及方法

移植到全新的PIC24F流水线ADC和Σ-ΔADC

了解流水线型ADC

流水线ADC和其它ADC对比分析

流水线ADC和其它ADC对比分析

评论