在上周公布Q3财报时,三星同时重修了先进制程进展情况,将已经稳定投产的最新节点从7nm LPP升级为5nm LPE。

此前有消息称,三星5nm产能遇困,阻碍了其规模量产工作,现在看起来情况已经好转甚至得到了完全解决。

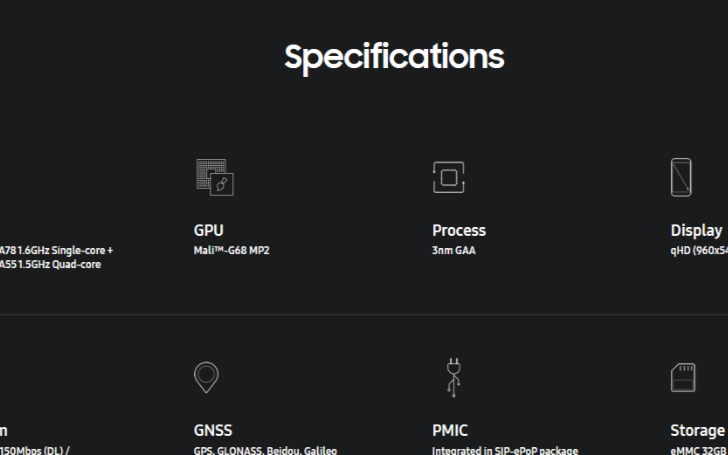

新的5nm旨在取代7nm,官方标称可带来10%的性能提升和同频下20%的功耗减少。密度方面,是上一代的1.33倍。

据悉,5nm LPE引入了多层EUV工艺过程,FinFET晶体管在微观层面也上马了智能双熔点分离、柔性放置触点等转为低功耗场景优化的技术。

三星还强调,5nm LPE和7nm在设计套件上兼容,以加快厂商部署芯片设计的速度。不过,这在某种程度上似乎也暗示,5nm下芯片的性能不会有令人印象深刻的提升。

外媒称,三星5nm工艺的首发SoC将是骁龙875 5G SoC,后者定于12月1日在骁龙技术峰会上推出。

责任编辑:PSY

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

三星电子

+关注

关注

34文章

15865浏览量

181040 -

soc

+关注

关注

38文章

4173浏览量

218382 -

5nm

+关注

关注

1文章

342浏览量

26089 -

骁龙875

+关注

关注

1文章

32浏览量

9300

发布评论请先 登录

相关推荐

台积电产能爆棚:3nm与5nm工艺供不应求

台积电近期成为了高性能芯片代工领域的明星企业,其产能被各大科技巨头疯抢。据最新消息,台积电的3nm和5nm工艺产能利用率均达到了极高水平,其中3nm

三星将为DeepX量产5nm AI芯片DX-M1

人工智能半导体领域的创新者DeepX宣布,其第一代AI芯片DX-M1即将进入量产阶段。这一里程碑式的进展得益于与三星电子代工设计公司Gaonchips的紧密合作。双方已正式签署量产合同,标志着DeepX的5nm芯片DX-M

三星开始量产其最薄LPDDR5X内存产品,助力端侧AI应用

深圳2024年8月6日 /美通社/ -- 2024年8月6日,三星电子今日宣布其业内最薄的12

可穿戴芯片进阶至3nm!Exynos W1000用上了面板级封装,集成度更高

电子发烧友网报道(文/莫婷婷)关于可穿戴芯片,三星已经推出了多款产品。2021年8月,三星发布Exynos W920,彼时是业内首款采用

三星首款3nm可穿戴设备芯片Exynos W1000发布

在科技日新月异的今天,三星再次以其卓越的创新能力震撼业界,于7月3日正式揭晓了其首款采用顶尖3nm

消息称台积电3nm/5nm将涨价,终端产品或受影响

据业内手机晶片领域的资深人士透露,台积电计划在明年1月1日起对旗下的先进工艺制程进行价格调整,特别是针对3nm和

三星发布三款新型移动图像传感器

6月27日,三星发布了三款专为智能手机主摄像头和副摄像头设计的新型移动图像传感器:ISOCELL HP9、ISOCELL GNJ和ISOCE

传三星电子12nm级DRAM内存良率不足五成

近日,据韩国媒体报道,三星在其1b nm(即12nm级)DRAM内存生产过程中遇到了良率不足的挑战。目前,该制程的良率仍低于业界一般目标的80%~90%,仅达到五成左右。为了应对这一局

三星、Meta等公司将用高通骁龙XR2+ Gen 3芯片,追赶苹果

据TechRadar 23日报道,三星与Meta已确定应用高通骁龙XR2+Gen3芯片组于各自的XR头显设备中,以此试图超越苹果Vision Pro头显。

三星电子开始量产其首款3nm Gate All Around工艺的片上系统

据外媒报道,三星电子已开始量产其首款3nm Gate All Around(GAA)工艺的片上系统(SoC),预计该芯片预计将用于Galax

台积电扩增3nm产能,部分5nm产能转向该节点

目前,苹果、高通、联发科等世界知名厂商已与台积电能达成紧密合作,预示台积电将继续增加 5nm产能至该节点以满足客户需求,这标志着其在3nm制程领域已经超越竞争对手三星及英特尔。

三星发布首款12层堆叠HBM3E DRAM

近日,三星电子宣布,已成功发布其首款12层堆叠的高带宽内存(HBM3E)产品——HBM3E 12H,再次巩固了其在半导体技术领域的领先地位。

三星电子成功发布其首款12层堆叠HBM3E DRAM—HBM3E 12H

2024年2月27日 - 三星电子今日宣布,公司成功发布其首款12层堆叠HBM3E DRAM——

三星推出全球首款AI手机

三星电子近日在美国举行的全球新品发布会上,发布了全新的Galaxy S24系列智能手机。这款手机最大的亮点在于搭载了人工智能(AI)技术,成为全球首款AI手机。

三星解决5nm产能问题 首款SoC骁龙875定于12月1日

三星解决5nm产能问题 首款SoC骁龙875定于12月1日

评论