这几天多篇文章爆出了“中芯国际涉军”,已被美国列入黑名单,深知信息搬运工的责任重大,秉着“不忘初心,牢记使命”的宗旨,外加周末有点自我安排的时间,所以也就有了本篇文章,另外作为模拟IC设计师,还是很有必要知道国内有哪些集成电路代工厂+工艺节点+工艺特征,毕竟我也是填过坑的人,项目指标来了首先需要确定的就是工艺,选择不当来回折腾也是难以避免,不废话上内容了。

责任编辑:xj

原文标题:国内主流集成电路代工厂的工艺特征

文章出处:【微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

集成电路

+关注

关注

5381文章

11387浏览量

360877 -

IC

+关注

关注

36文章

5900浏览量

175240 -

中芯国际

+关注

关注

27文章

1417浏览量

65277

原文标题:国内主流集成电路代工厂的工艺特征

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

集成电路工艺学习之路:从零基础到专业水平的蜕变

集成电路(IC)作为现代电子技术的核心,其制造工艺的复杂性和先进性直接决定了电子产品的性能和质量。对于有志于进入集成电路行业的学习者来说,掌握一系列基础知识是至关重要的。本文将从半导体物理与器件

新思科技针对主要代工厂提供丰富多样的UCIe IP解决方案

Multi-Die设计之所以成为可能,除了封装技术的进步之外,用于Die-to-Die连接的通用芯粒互连技术(UCIe)标准也是一大关键。 通过混合搭配来自不同供应商,甚至基于不同代工厂工艺节点的多个芯片或小芯片,芯片开发者可以

概伦电子NanoSpice通过三星代工厂3/4nm工艺技术认证

概伦电子(股票代码:688206.SH)近日宣布其新一代大容量、高性能并行SPICE仿真器NanoSpice通过三星代工厂3/4nm工艺技术认证,满足双方共同客户对高精度、大容量和高性能的高端电路仿真需求。

专用集成电路包括哪些内容 专用集成电路设计与工艺

专用集成电路(Application Specific Integrated Circuit,简称ASIC)是指为特定应用领域而设计和生产的一类集成电路。相比通用型集成电路,专用集成电路

2024年最新全球EMS代工厂50强(TOP 50)

在科技产业中,EMS(ElectronicManufacturingServices,电子制造服务)代工厂扮演着至关重要的角色。它们为全球各地的品牌商提供从设计到生产、组装、测试到最终出货的全方位

东芝BiCD工艺集成电路硅单片TB67H450AFNG数据手册

电子发烧友网站提供《东芝BiCD工艺集成电路硅单片TB67H450AFNG数据手册.pdf》资料免费下载

发表于 03-20 11:23

•1次下载

Intel Foundry:2030成为全球第二大半导体制造代工厂!

英特尔为英特尔代工厂(Intel Foundry)的首次亮相举行了名为Intel Direct Connect的开幕活动,英特尔在活动中全面讨论了其进入下一个十年的工艺技术路线图,包括其14A前沿节点。

Cadence与Intel代工厂合作通过EMIB封装技术实现异构集成

Cadence 与 Intel 代工厂合作开发并验证了一项集成的先进封装流程。该流程能利用嵌入式多晶粒互连桥接(EMIB)技术来应对异构集成多芯粒架构不断增长的复杂性。

英特尔发力18A工艺节点,力图超越三星跃升全球第二大晶圆代工厂

该美大型芯片厂商正在积极推广旗下Intel 18A(1.8nm级)工艺节点,并出示多种惠及客户的策略;近期,英特尔进一步发布新的Intel 14A(1.4nm级)工艺节点,宣布采用该

无意发展至10nm以下,第二梯队晶圆代工厂的成熟工艺现状

电子发烧友网报道(文/周凯扬)半导体制造工艺经过多年的发展,已经有了翻天覆地的变化。但如果我们单从晶圆代工厂的工艺布局来看,就会发现变化并不算大,领头的台积电、三星等依然在加大先进工艺

走成熟特色工艺路线,有哪些创新之道?

集成电路产业创新发展高峰论坛(ICCAD 2023)上,来自晶圆代工厂、封装企业以及IC设计企业的高管们共同探讨了工艺、技术创新与市场等话题,分享了许多精彩见解。 结合本土化需求的晶圆代工

新思科技携手Ansys和三星共同开发14LPU工艺的全新射频集成电路设计

新思科技(Synopsy)近日宣布,携手Ansys 、三星半导体晶圆代工(以下简称“三星”)共同开发了面向三星14LPU工艺的全新射频集成电路(RFIC)设计参考流程

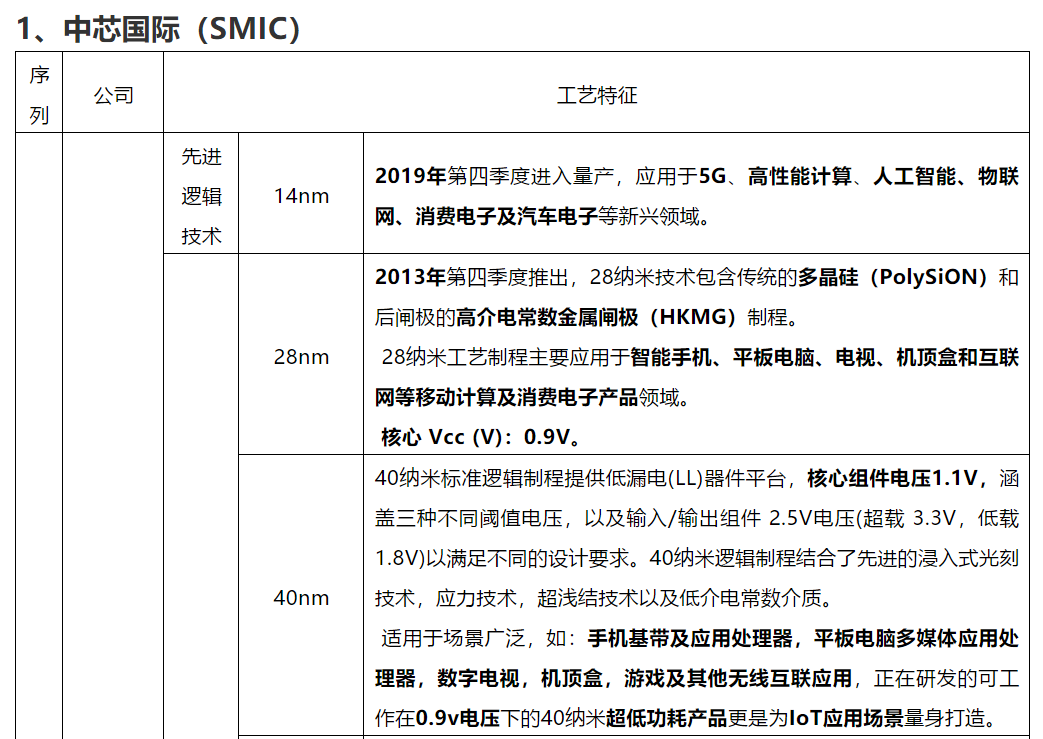

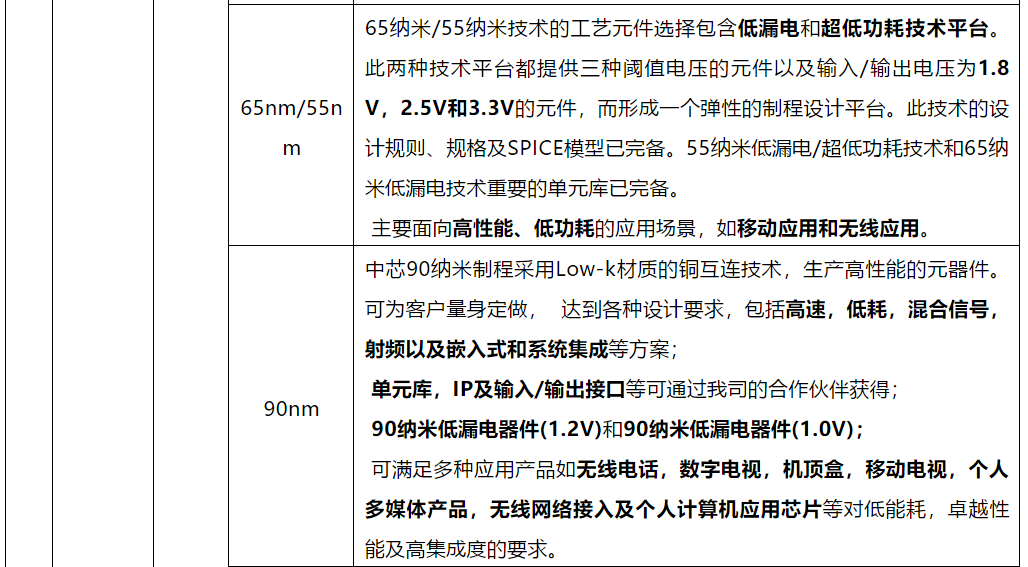

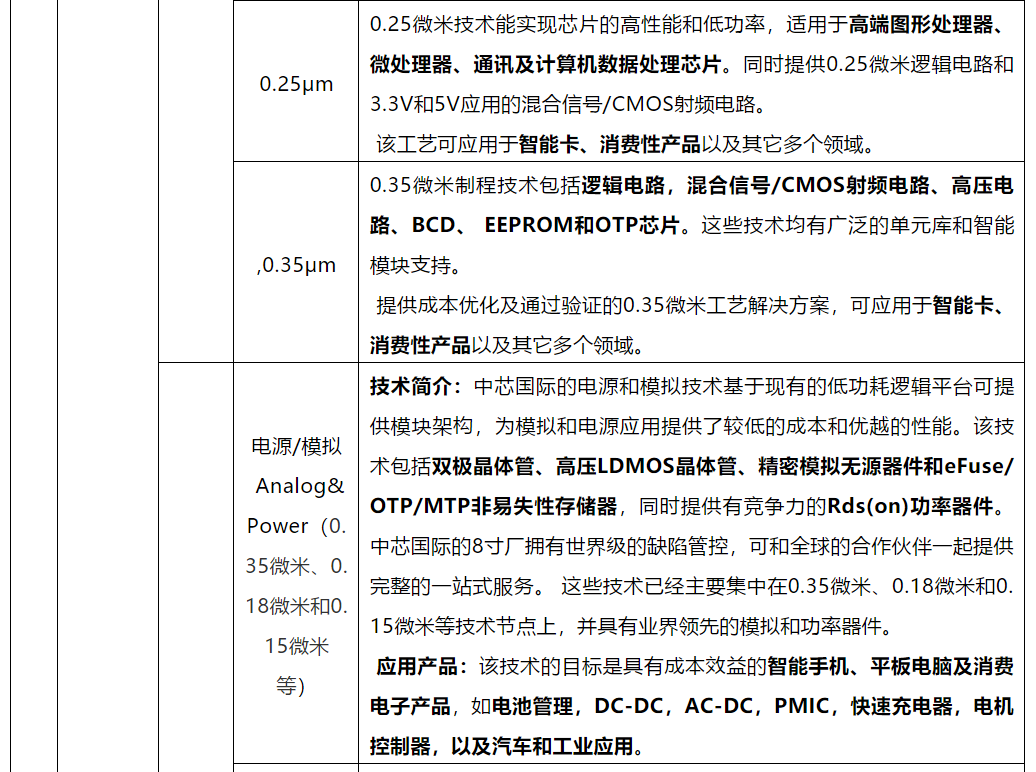

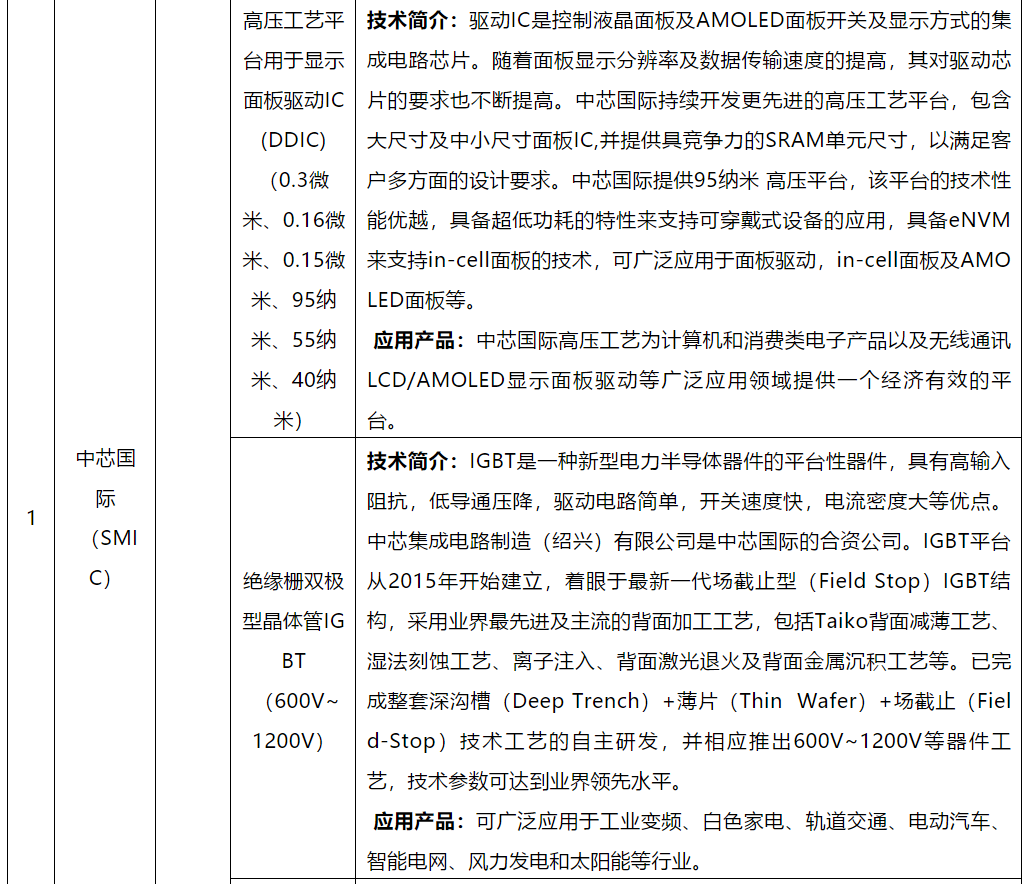

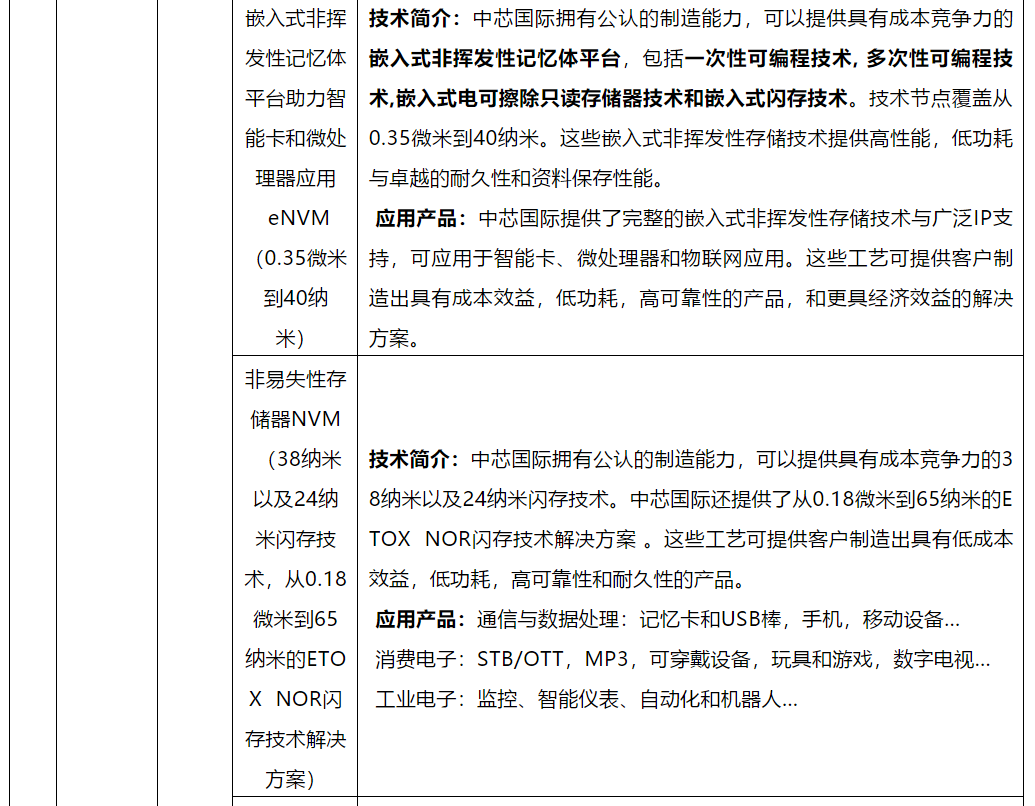

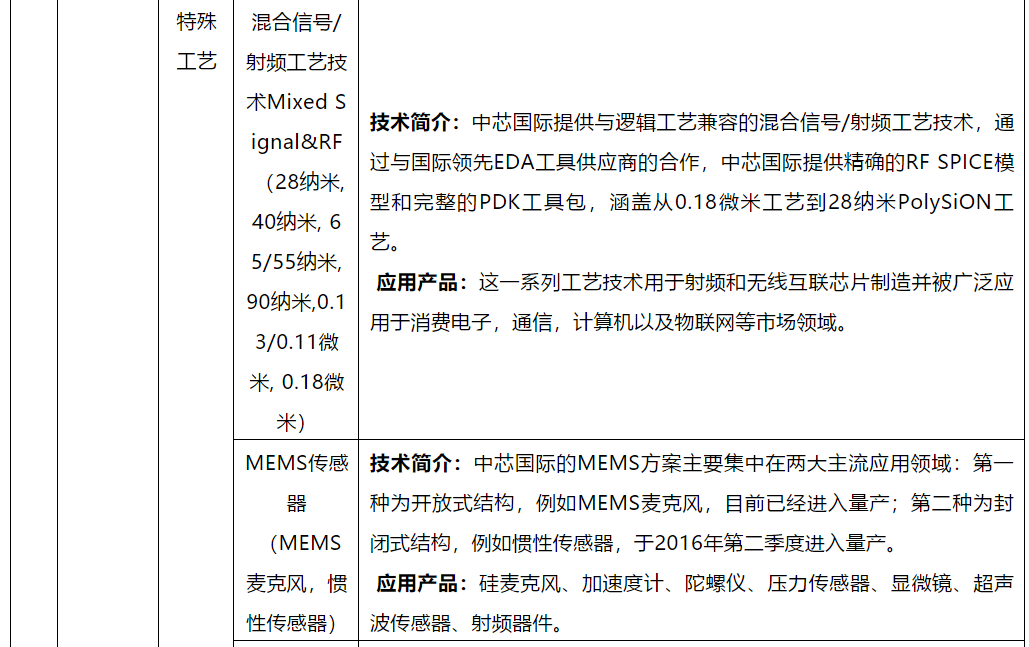

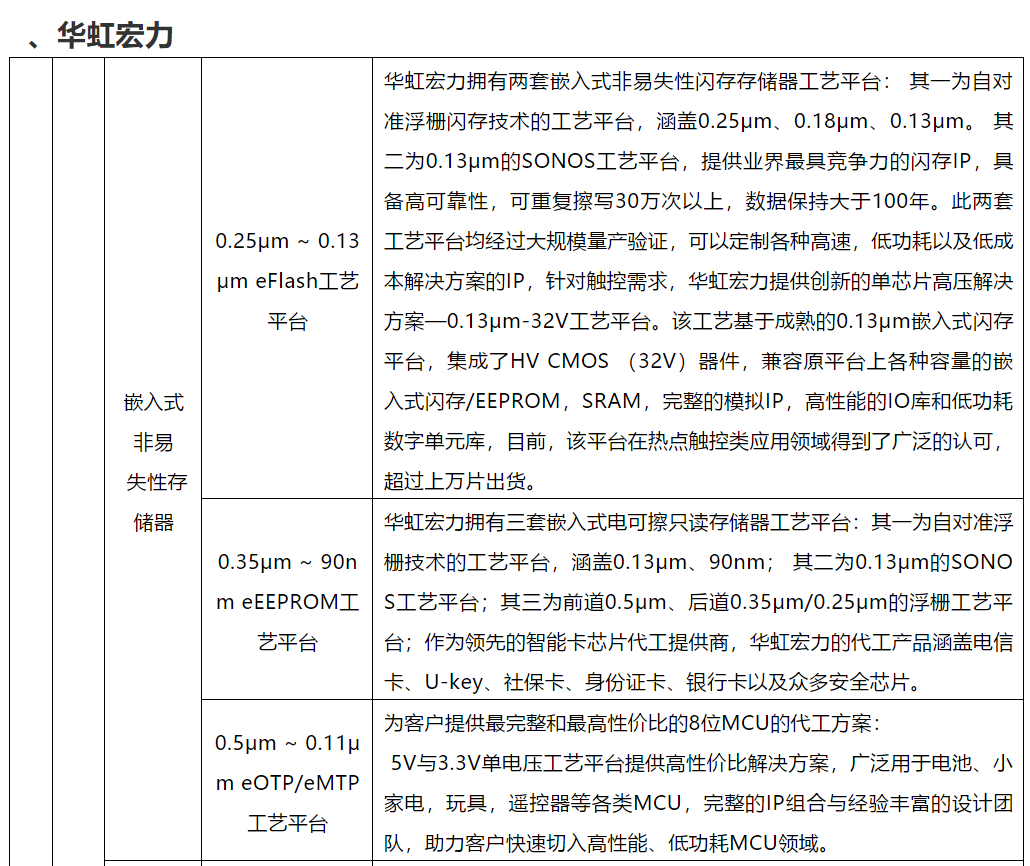

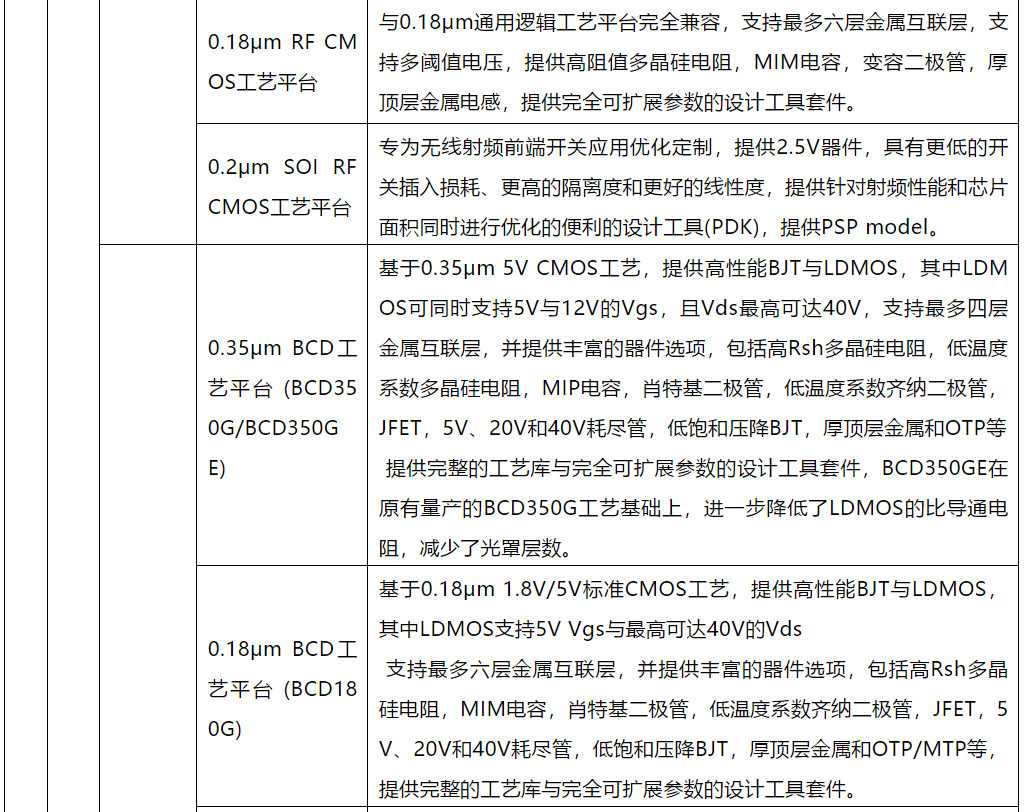

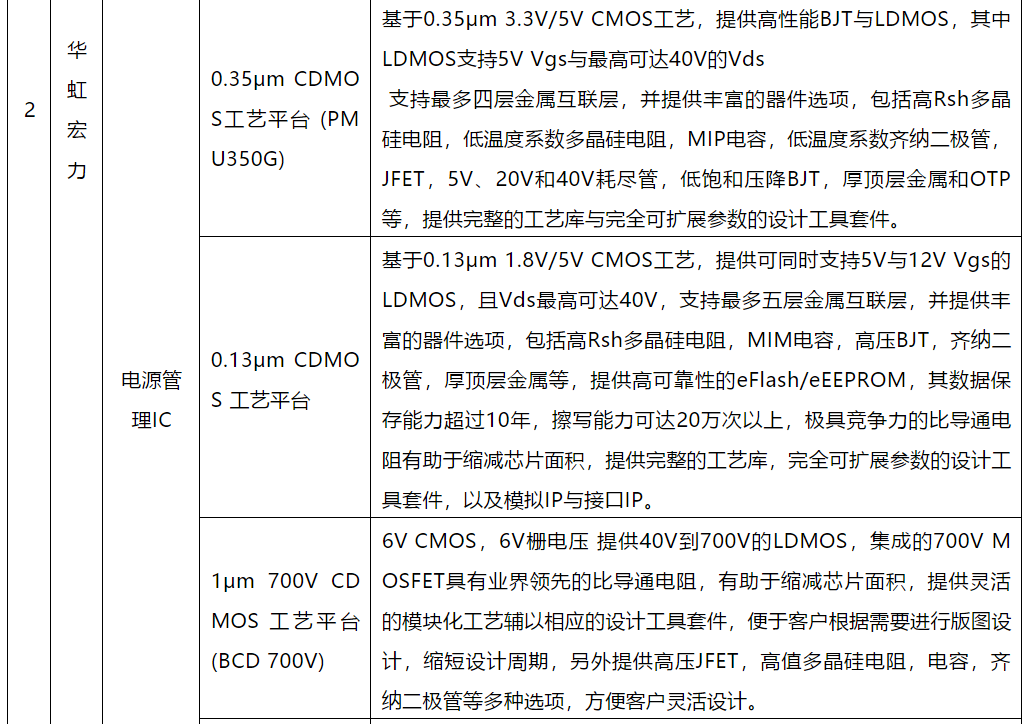

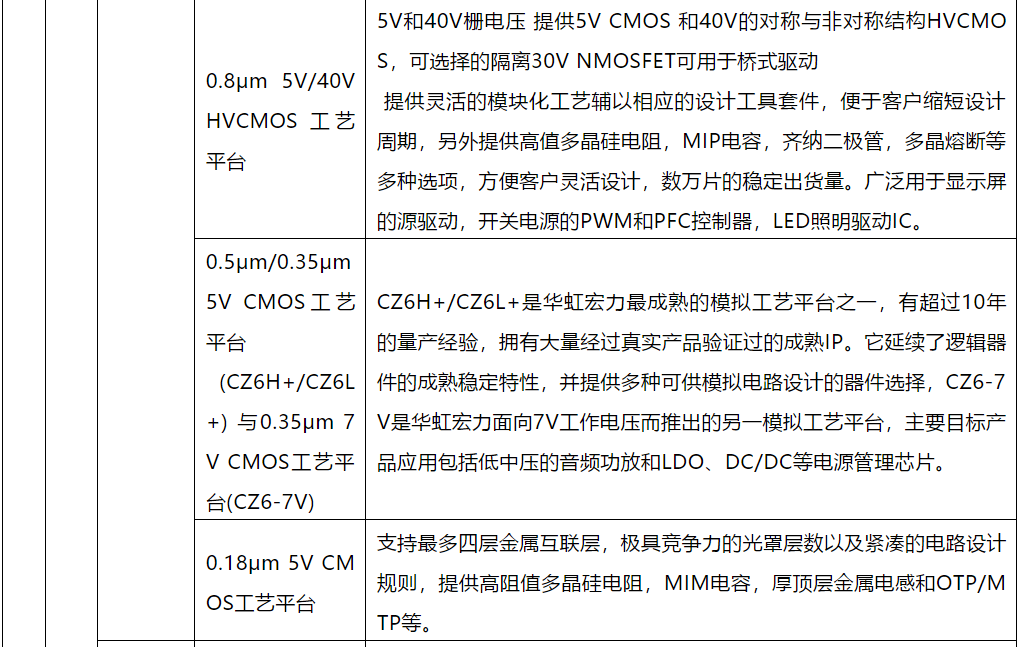

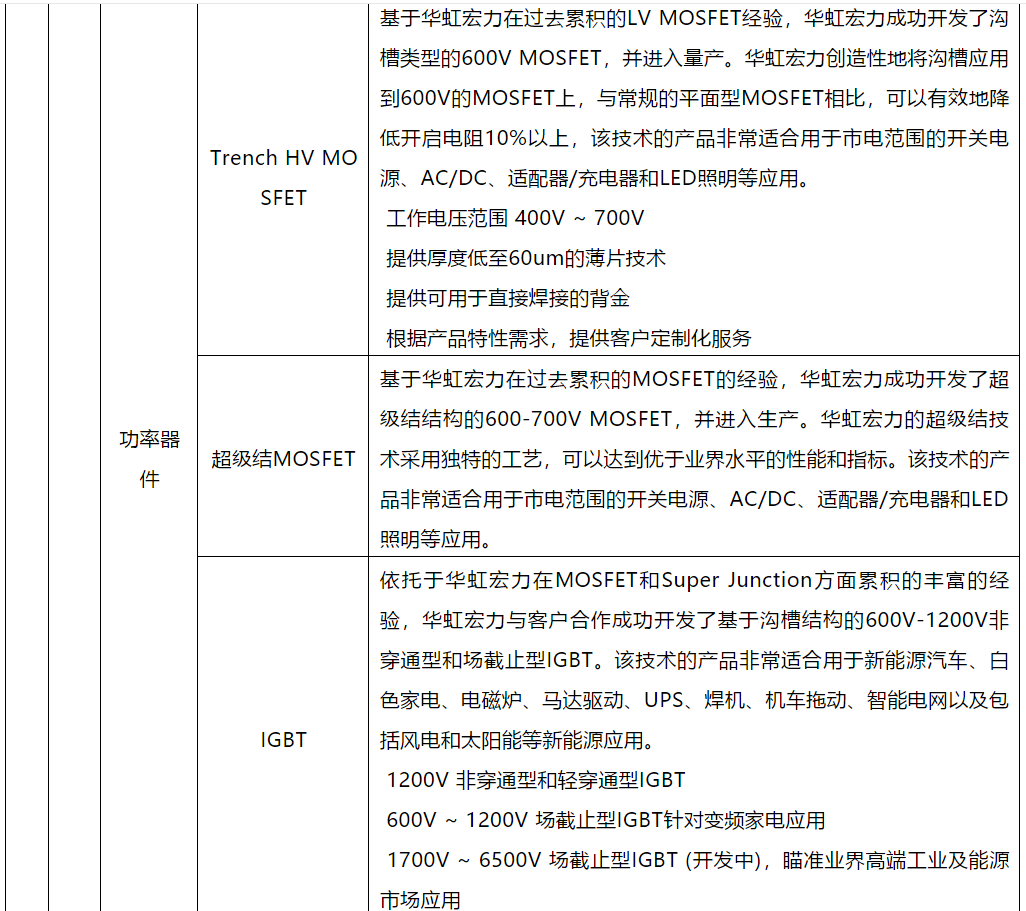

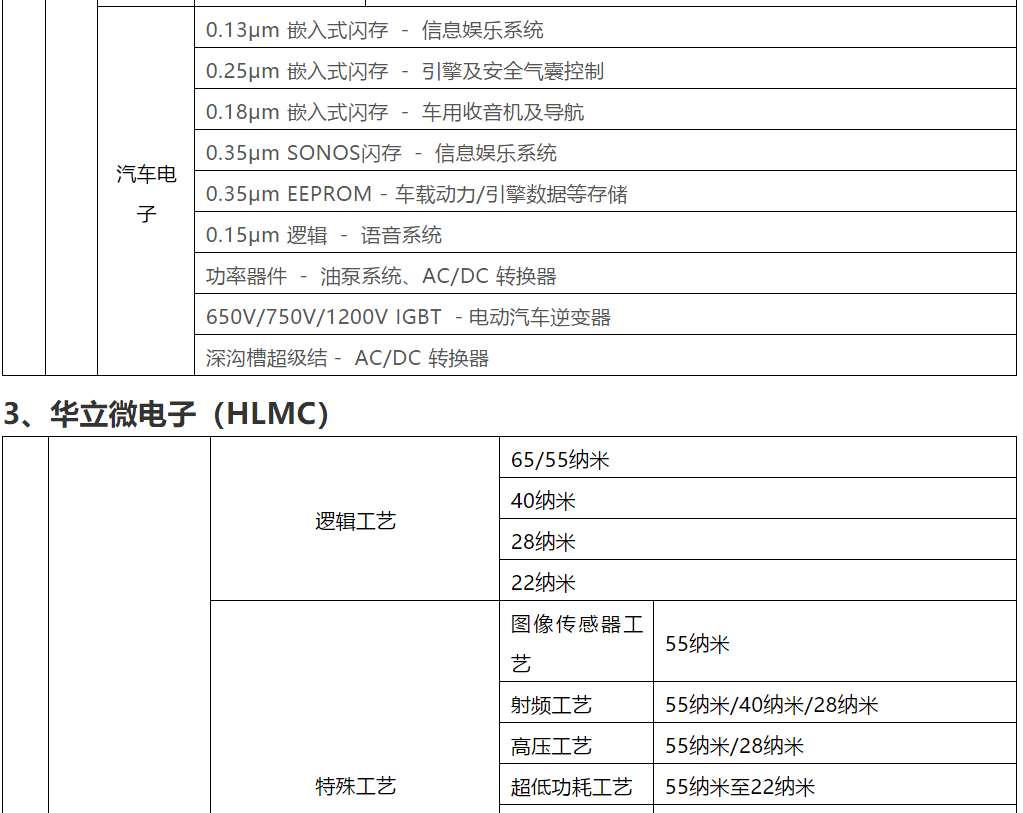

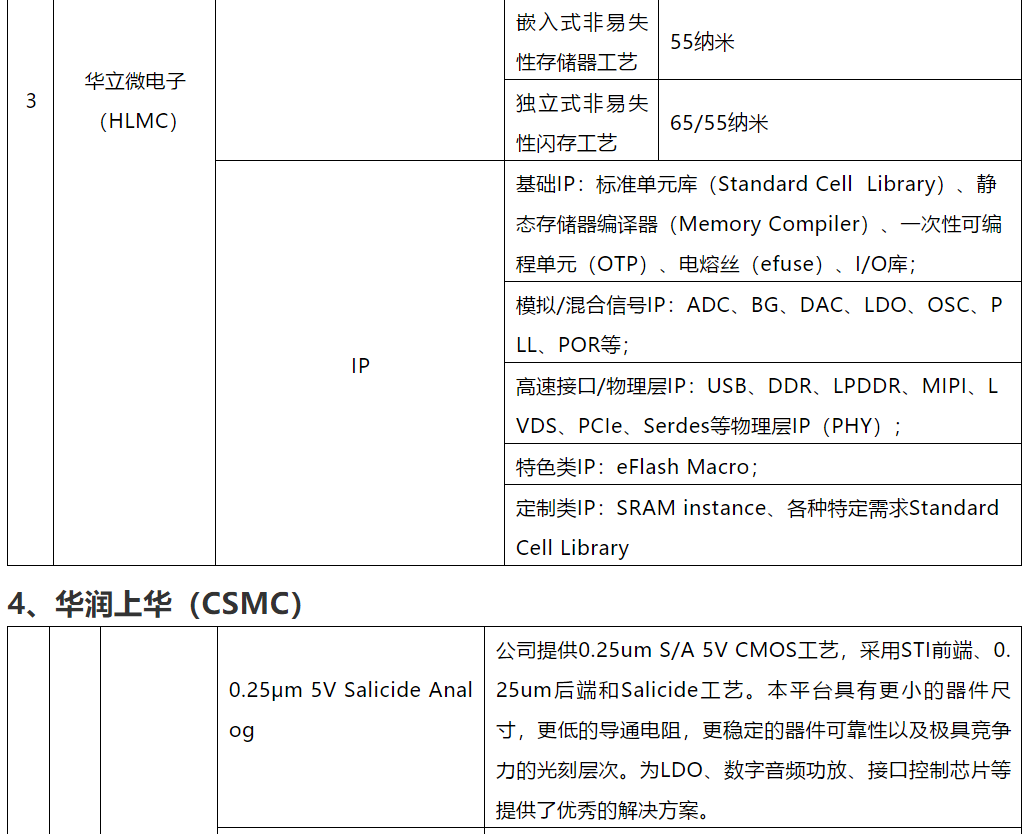

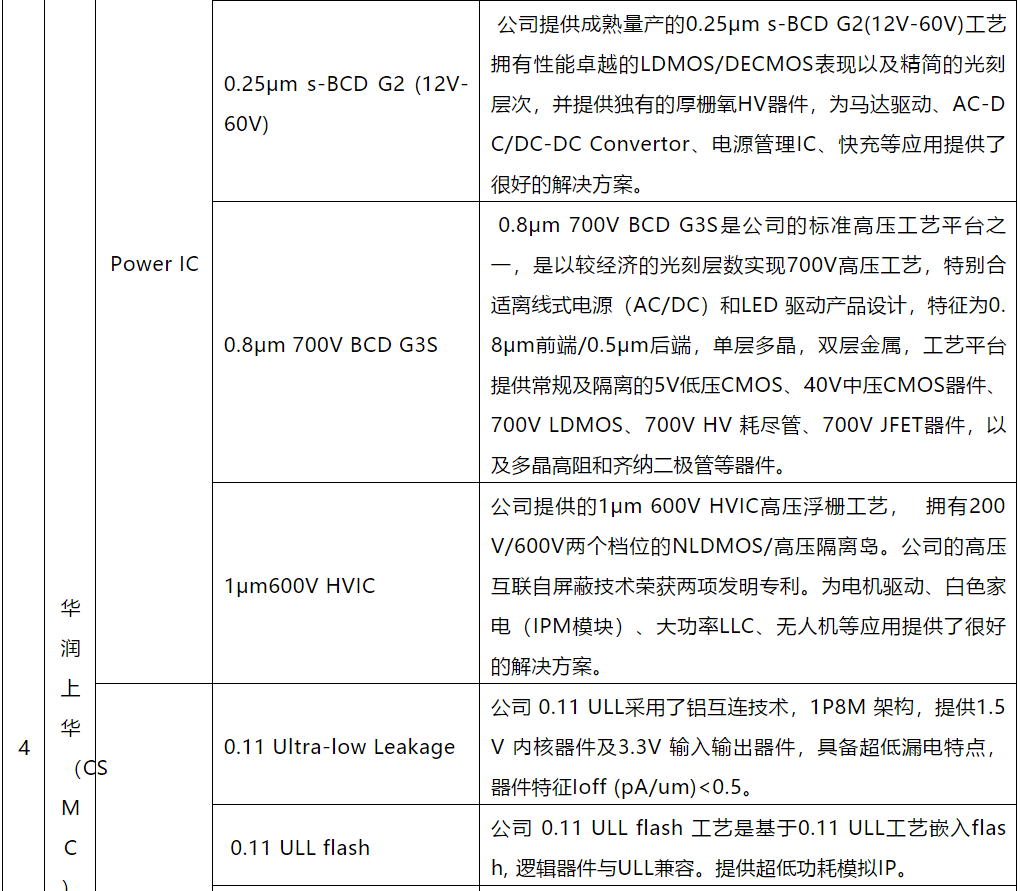

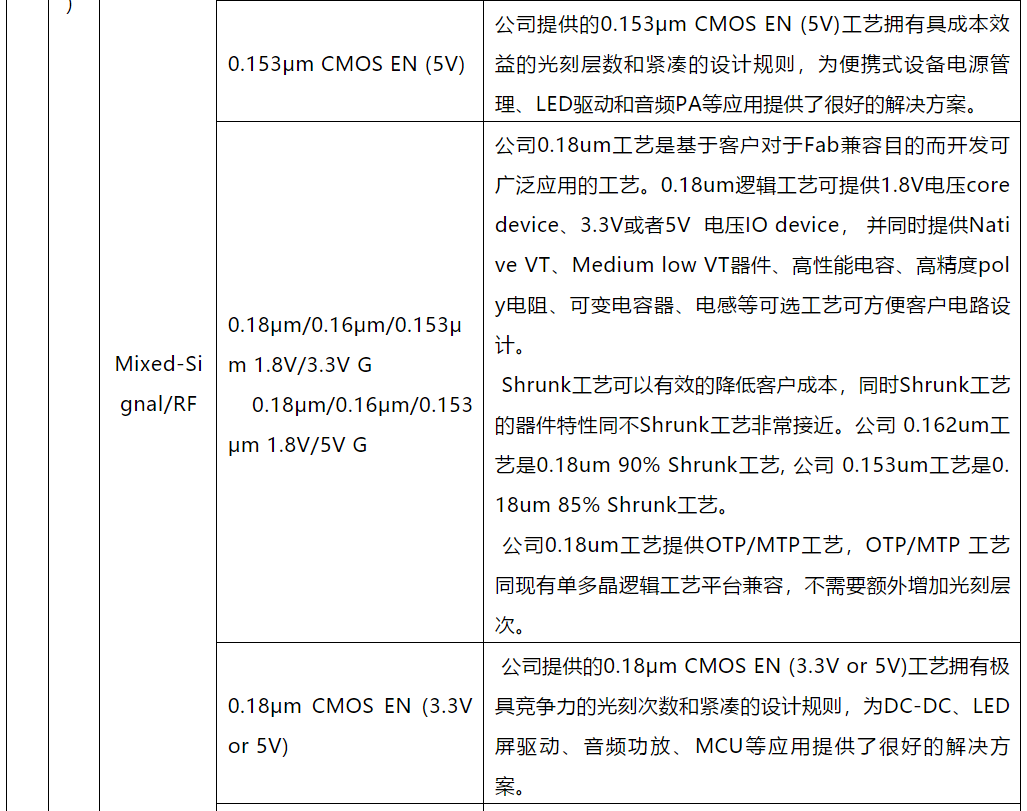

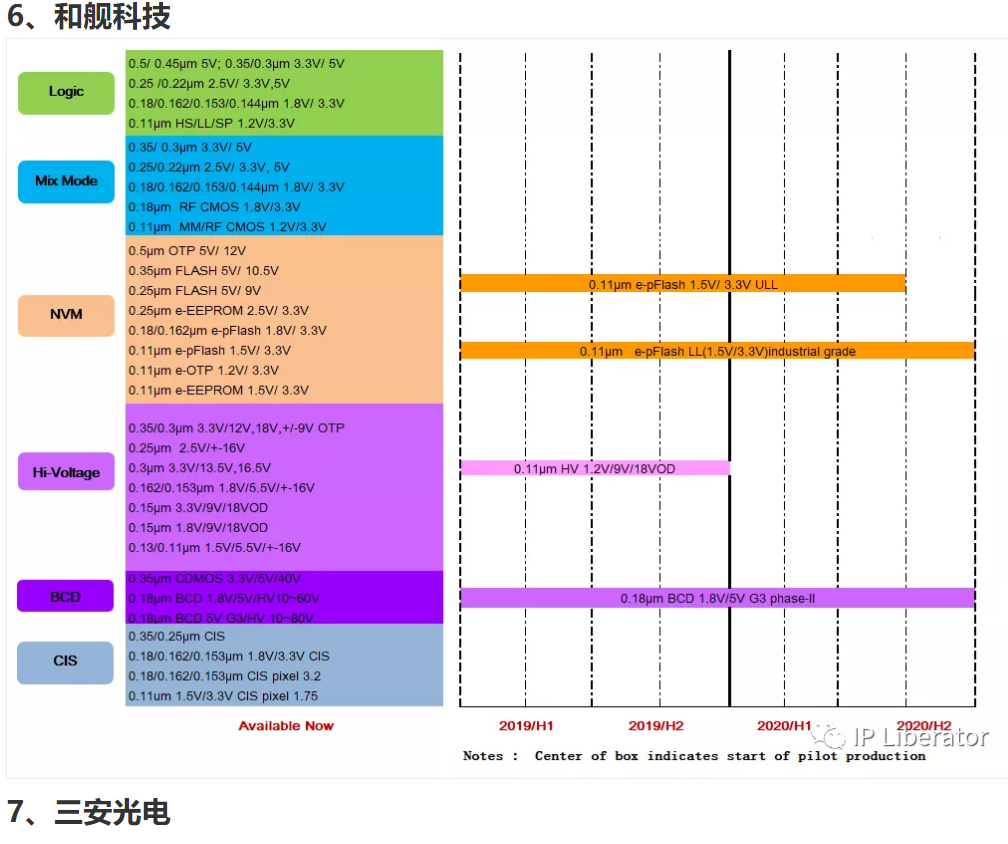

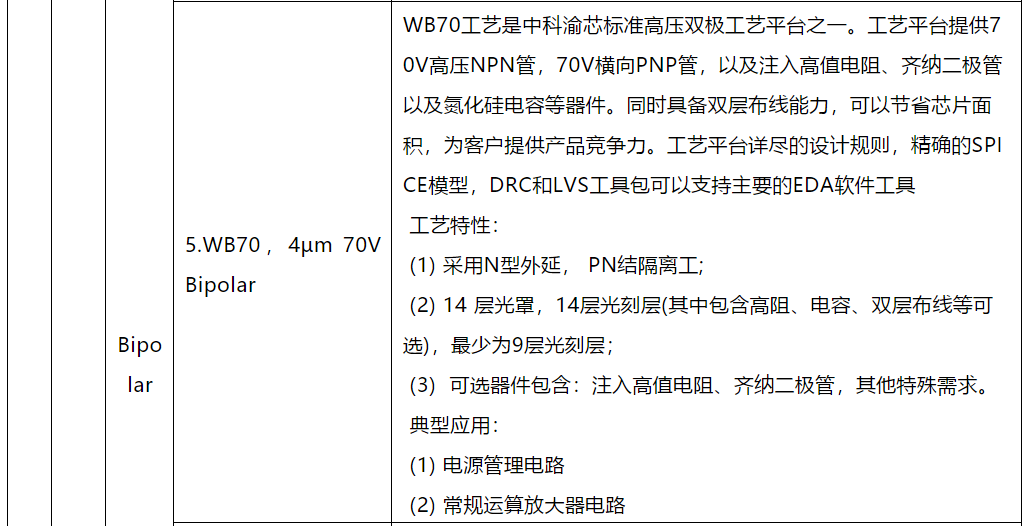

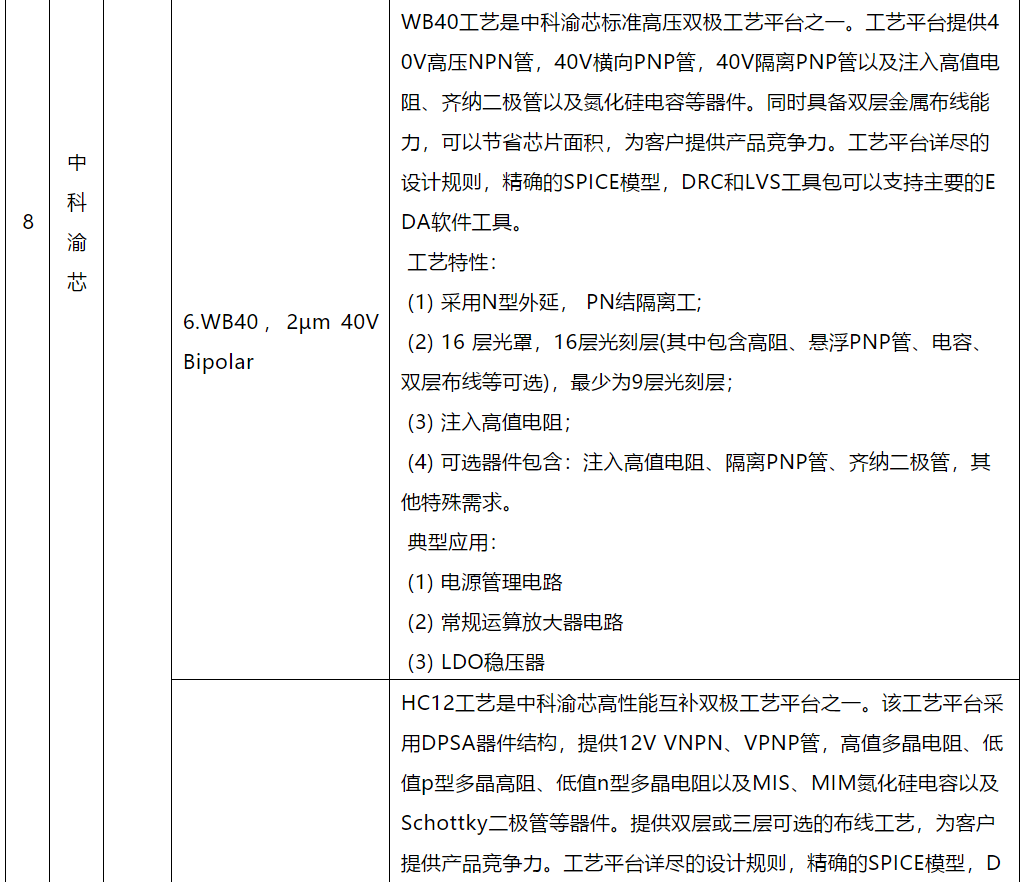

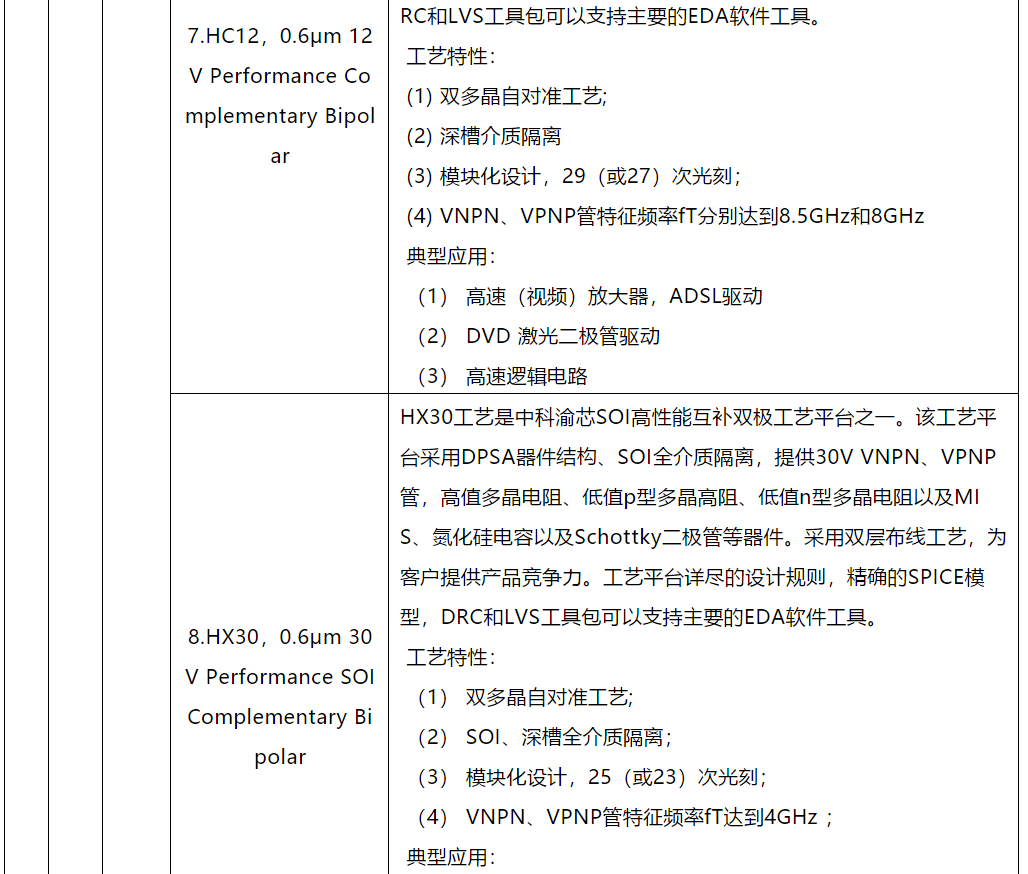

国内主流集成电路代工厂、工艺节点及工艺特征

国内主流集成电路代工厂、工艺节点及工艺特征

评论