在FPGA开发板设计时,为任何基于SERDES的协议选择一个参考时钟源都是非常具有挑战性的。器件成本、通过耦合高速信号使得噪声最小化、超低抖动要求、由于信号长度匹配的要求而对走线的限制、考虑周全的电源供电设计(包括噪声的考虑、元件布局上的限制、信号布线的要求和电源去耦)以及测试/生产要求,这些都必须考虑到并对各个因素的利弊进行权衡分析。

为满足目前的56GPAM-4SerDes技术,以支持更高带宽的100G+以太网和光网络设计。硬件开发人员通常需要100fs(典型值)以下RMS相位抖动规范的时钟。这些设计通常需要与CPU和系统时钟等其他频率时钟混用。

在选取参考时钟参考源时,必须选取超低抖动的时钟芯片以满足互联网基础设施的严格规范和高性能要求,同时也要考虑各种时钟应用的成本和复杂性。

针对56G/112G的Serdes接口,目前市场上知名度大的是Silicon发布的Si539x系列时钟,它能够从任意频率输入时钟产生任意频率输出时钟组合,同时提供业界领先的抖动性能(90fsRMS相位抖动),其中Si5395/4/2P级时钟器件为56G/112GSerDes时钟应用提供了最佳的抖动性能(69fsRMS典型相位抖动)。

责任编辑:lq

-

以太网

+关注

关注

40文章

5480浏览量

173195 -

单通道

+关注

关注

0文章

295浏览量

18347 -

时钟源

+关注

关注

0文章

94浏览量

16085

原文标题:SI-list【中国】单通道56G的SERDES,参考时钟如何选取?

文章出处:【微信号:si-list,微信公众号:高频高速研究中心】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DLPDLCR4710EVM-G2如何实现单通道无闪烁地图像输出?

如何使用ADC08D1000的芯片进行1G双通道采样或2G单通道采样?

config108读取config108寄存器的值时钟为000f,只是serdes_pll未锁定,为什么?

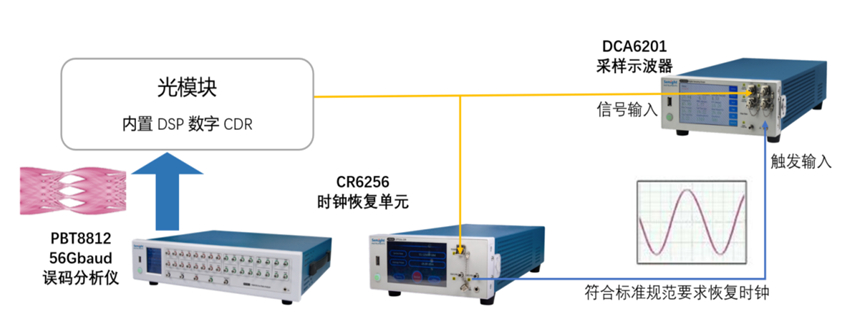

56Gbaud CR6256!400G/800G单多模光模块及接口的时钟提取

单通道56G的SERDES,参考时钟如何选取?

单通道56G的SERDES,参考时钟如何选取?

评论