01

FPGA的设计流程

FPGA是可编程芯片,因此FPGA的设计内容包括硬件设计和软件设计两部分。硬件包括FPGA芯片电路、 存储器、输入输出接口电路以及其他设备,软件即是相应的HDL程序以及最新才流行的嵌入式C程序。

FPGA的开发流程即是利用EDA开发软件以及编程工具对FPGA芯片进行开发的过程。EDA ( Electronic Design Automation,电子设计自动化)是充分发挥LSI性能的关键技术。理论上,一款FPGA所能达到的性能上限是由制程等物理因素决定的,而在实际应用中用户电路的性能很大程度上取决于器件的架构和EDA工具。这就像汽车一样,无论引擎(制程)多么强劲,都需要配合适当的车体(架构)和驾驶技术( EDA工具)才能发挥出极限速度。尤其是与电路实现直接相关的EDA工具,其对性能的影响不可估量。

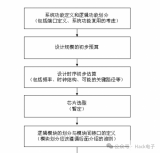

FPGA的设计流程由HDL源代码的逻辑综合开始,经过工艺映射、逻辑打包、布局布线等过程,最终生成比特流。逻辑综合将HDL描述转换为门级网表,工艺映射将这个网表转换为查找表级别的网表。逻辑打包是将多个查我表和触发器集合到一个逻辑块的过程。布局布线工具先决定逻辑块在器件上的位置,然后通过布线结构实现逻辑块之间的连接。最终,基于这些布局布线信息可以决定FPGA中各个开关的连接关系,以此生成比特流。

器件上查找表的输入数是既定的(查找表能实现输人数不大于自己的任意逻辑),而FPGA的设计就是要从目标电路的逻辑函数中不断分离出既定输入数之内的逻辑,并将其映射到查找表上。然后将这些查找表通过布线相连, 就可以在FPGA 上实现目标电路。

FPGA和ASIC的区别在于,ASIC通过组合使用标准单元库中的逻辑实现电路,而FPGA则使用统一构造的查找表。这种区别也体现在了EDA工具上。下面我们就对这种不同于ASIC的EDA技术原理进行详细介绍,具体包括上述的工艺映射、逻辑打包、布局布线。

02

工艺映射

工艺映射是指将不依赖于任何工艺的门级网表转换为由特定FPGA逻辑单元所表示的网表的过程。这里所说的逻辑单元依赖于特定的FPGA架构,是由查找表或MUX等逻辑电路实现的FPGA上的最小逻辑单位。工艺映射是从HDL开始的逻辑转换的最后一步,因此对最终电路实现的质量(面积、速度、功耗等)至关重要。下面我们就通过工艺映射最具代表性的工具FlowMap,来讲解工艺映射的原理。Flow Map是由加州大学洛杉矶分校丛京生教授(Jason Cong)的研究团队开发的工艺映射算法。将目标电路网表转换到k输入的查找表(k-LUT)的工艺映射过程由下面两个步骤组成。

(1)分解:门级网标实际上都是以布尔网络的形式来表示的。先将布尔网络的各个节点不断分解,直至输人数小于查找表的输人数k。

(2)覆盖:基于过程(1)所得到的布尔网络,使用某种基准对输入进行切分,使用k-LUT覆盖多个节点。

FlowMap第(2)步的覆盖过程,是一种可以在多项式时间内找到逻辑层数最优解的方法。

03

3、逻辑打包

目前,主流FPGA的逻辑块都具有多个查找表,因此将查找表高效地打包到逻辑块的过程是不可或缺的。逻辑打包主要有两个要点:第一,逻辑块内部布线(局部布线)和逻辑块外部布线(布线通道中的布线)的延迟相差很大;第二,如果逻辑块中有查找表空闲,资源使用率就会降低(增加逻辑块的使用量),因此要尽量在每个逻辑块内填装更多逻辑。

之前世界上出现了许多可以实现多种性能优化的打包工具,但他们的装箱算法都只能处理单一的查找表结构。近些年的逻辑块包含了自适应查找表等更为复杂的结构。自适应查找表不仅需要在工艺映射时选择最佳输入数的查找表,对装箱算法也有很大影响。比如,在打包自适应查找表的网表时为了改善布通率和延迟,不能只考虑逻辑块中查找表的数量,还要考虑主输入数量、逻辑块所允许的查找表模式组合等因素。因此要找到同时满足逻辑块数最少、延迟最小、布线数最少的解是非常困难的。

VTR(Verilog-to-Routing)中集成的AAPack(ArchitectureAware Packer)就是为了挑战这个问题而诞生的。VTR系统使用XML的形式建立器件的架构模型。其架构的定义分为单元结构( physical block,相当于逻辑块内的逻辑单元)和布线结构( interconnect,相当于physical block间的连接关系和连接方式)。单元结构的描述方式为嵌套式,可以描还含有多个逻辑单元的逻辑块。使用模式单元还可以表达具有多种模式的结构,例如将多输入查找表拆分为多个少输人的查找表(多种模式)等。

AAPack实现了对上述架构模型的支持,其装箱算法如下所示。

(1)如果有未打包的查找表,则选其作为种子并确定要插入的逻辑块。

(2)按照如下算法向当前逻辑块填装查找表。

(a)寻找可填装的候补查找表。

(b)将选择的查找表填入逻辑块。

(c)如果逻辑块还有空位,返回到步骤(2)的(a)。

(3)将装箱完毕的逻辑块输出到文件,返回到步骤(1)。

综上,AAPack可以对结构复杂的逻辑块实现查找表打包功能。

04

布局布线

布局布线是FPGA设计流程的最后一个步骤——在物理上确定逻辑块的位置和信号连接路径。一般来说首先会确定逻辑块的布局,然后再对逻辑块间的连接进行布线。

多数FPGA的逻辑块都呈二维阵列状排列,因此逻辑块布局问题可以视为标准的二次分配问题。然而,此类问题也被公认为是NP问题,通常只能使用SA ( Simulated Annealing)等算法获取近似解。

布线过程中主要使用两种布线方法:全局布线和详细布线。全局布线阶段主要决定线网的布线路径,例如通过哪些通道形成连接。详细布线则基于全局布线所得的信息,确定路径具体使用了哪些布线资源、通过了哪些开关等。

下面我们使用由多伦多大学开发、在学术界被广泛应用的布局布线工具VPR(Versatile Place and Route)进行介绍。VPR的布线过程如下。

(1)先将逻辑块、I/O块随机放置。

(2)计算当前布局的布线拥挤度。

(3)随机选择两个逻辑块并对调其位置。

(4)计算对调后的布线拥挤度。

(5)比较对调前后拥挤度的数值,决定是否接受新的布局。

目前,作为最主要的开源FPGA设计框架,VPR已经发展到了7.0的版本了,其中也加入了一些更加实用的功能和工具,例如支持进位信号等专用连接、多时钟域时序分析、功耗分析等。

责任编辑:xj

原文标题:FPGA设计原理

文章出处:【微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

-

芯片

+关注

关注

455文章

50714浏览量

423132 -

FGPA

+关注

关注

1文章

24浏览量

16013

原文标题:FPGA设计原理

文章出处:【微信号:gh_873435264fd4,微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA与ASIC的优缺点比较

莱迪思Propel工具套件加速FPGA应用开发

FPGA实现LeNet-5卷积神经网络

FPGA的学习笔记---FPGA的开发流程

AMD FPGA中MicroBlaze的固化流程详解

深入探索Vivado非工程模式FPGA设计流程

FPGA设计流程及原理

FPGA设计流程及原理

评论