印制电路板(PCB)易于制造,性能可靠,价格便宜,因此广泛地应用于各种电子设备中。近年来,随着电子技术的发展,印制电路板上微处理器和逻辑电路中的时钟速率越来越快,信号的上升/下降时间越来越短,同时,板上器件密度和布线密度不断增加,印制电路板的电磁兼容问题变得日益突出。

在电磁兼容层面分析印制电路板,要考虑三个基本问题:

保证信号在板上可靠地传输,确保信号的完整性(Signal Integrity);

抑制电磁干扰EMI的传播;

加强防护,防止因为抗扰度不足引起灵敏度故障(Susceptibility Failure)。

对于相对低频的信号(信号的频谱上限为100MHz),通常可以不考虑上述的问题。但是当信号波长(λ)与信号线长度(l)可相互比拟时(l≥0.1λ),就需要考虑印制线的几何尺寸、布线、线间间隔以及传输信号的上升、下降时间,脉冲宽度与周期等因素,以致需要用传输线理论(在某些场合需要用微波理论)来正确地分析信号的传播。

印制电路板上的印制线通常可以用微带线或带状线模型来模拟。微带线模型由介质基片一边的导体带和基片另一边的金属接地板构成,它可用来模拟PCB表面层的印制导线。带状线模型由上下接地导体和中间导体带构成,接地板和导体带之间是绝缘介质,它可以模拟多层PCB中间层的印制导线。

一、 信号完整性

PCB上的信号完整性问题主要包括时延、阻抗不匹配、地弹跳(Ground Bounce)、串音等。信号完整性问题会影响电子器件的稳定工作。

(1)信号时延:对于高频信号,传输时延应该是电路设计者考虑的最基本的问题之一。传输时延与信号线的长度、信号传输速度的关系如下:

式中:c—真空中的光速;

εreff有效的相对电导率;

lp—信号线的长度。

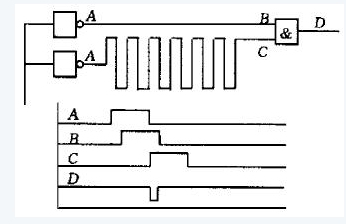

εreff与传输线周围介质有关,对于微带传输线来说,ε介于板的相对电导率与空气相对电导率之间。在大多数系统中,信号传输线长度是影响时钟脉冲相位差(colock skew)的最直接因素。时钟脉冲相位差是指同时产生的两个时钟信号,到达接收端的时间不同步。时钟脉冲相位差降低了信号沿到达的可预测性,如果时钟脉冲相位差太大,会在接收端产生错误的信号,如图l所示。传输线时延已经成为时钟脉冲周期(Clock Cycle)中的重要部分。

图1 传输时延对信号的影响

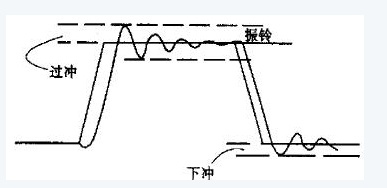

图2 反射引起的振铃现象

(2)阻抗不匹配:

阻抗不匹配可以由驱动源,传输线和负载的阻抗不同引起,也可由传输线的不连续?例如导通孔、短截线?引起,另外由于返回路径上局部电感、电容的变化,返回路径不连续也会导致阻抗不连续。这种阻抗的不匹配,会导致反射和阻尼振荡。反射会引起信号的振铃?Ringing?现象,即在稳态信号上下产生的电压过冲和下冲现象,如图2所示。为了将电压的过冲/下冲限制在合理的范围内(不超出稳态值的l0%~15%),应该遵循下面这样一个原则:信号的上升时间要小于信号在印制导线上来回引起的传输时延。即: tr≤2lp/tppd

式中:tr—指信号的上升时间;

lp—信号线的长度;

tppd—信号线单位长度引起的延时。

振铃现象可能会导致误触发,为了消除振铃现象的影响,方法之一就是等待信号稳定下来,但这又会减小系统最大可能的时钟速率。

(3)地弹跳(Gound Bounce):所谓地弹跳,是指在某一集成电路开关时,由于PCB的地线以及集成电路的接地引线具有一定的电感,相应会引起器件内部地电位短暂的冲击或下降。而来自其它器件的输入驱动信号,或者由此器件输出信号所驱动的其他器件,都是以外部系统地为参考的。这种参考地电位的不一致,可能会导致器件的输入门槛或输出电平的改变,从而给高速PCB的设计带来问题。对于电源来说,也存在类似的问题。

(4)串音:通常可分为两部分,即公共阻抗耦合和电磁场耦合。公共阻抗耦合是因为不同信号共用公共返回路径引起的,这种耦合通常在低频时起决定作用。电磁场耦合又可分为电感耦合与电容耦合。串音属于近场问题,在PCB0上,串音与线的长度、线的间距、线中传输信号的方向以及参考地平面的状况有关。例如地平面上的裂缝(Split)会使跨越裂缝的邻近线路的串音增加,引起信号波形畸变。

2 减小传导发射和辐射发射

电磁干扰问题主要包括传导发射和辐射发射问题。电磁兼容中所谓的发射,是指“从源向外发出电磁能的现象”,与一般通信领域中人为的向外发射电磁波不同,PCB中的发射常常是无意的。辐射发射标准通常覆盖30MHz~1GHz的范围,在不久的将来将扩展至5~40GHz。对于传导发射,FC

C将范围限

制在0.45~30MHz,而CISPR将下限延伸0.15MHz。滤波是抑制传导发射的一种重要方法。对离开PCB板的信号线进行滤波,可以抑制传导发射的传播。

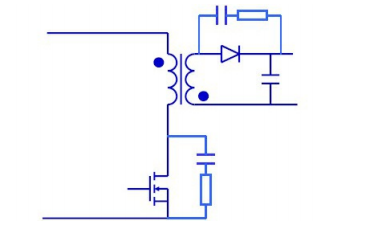

高频时,PCB上的印制线就像一个单极天线(mono-pole Antennas)或环形天线(Loop Antennas),向外辐射能量。辐射发射可以分为两种基本类型:差模辐射和共模辐射。

差模辐射是由于闭合环路中的电流?即所谓的差模电流?引起的。辐射的强度与环的面积、电流的大小及频率的平方成正比。通过减小上述因素,尤其是频率,可以减小辐射的强度。另外,环的辐射具有方向性,一个小电流环的电场辐射值在环所处的平面上最大,而在环的轴向上最小。

共模辐射是由寄生效应,例如地线层、电源层或电缆上的感应电流?所谓的共模电流?引起的。共模辐射与一个单极天线类似,辐射的强度与单位线长中的电流及频率有关,但对方向不敏感。

由于差模电流产生的辐射是相减的,而共模电流产生的辐射是相加的,所以即使共模电流比差模电流小的多,也会产生程度相当的辐射场。例如,长为lm的电缆,其中间距为1.27mm的两导线中流有30MHz、20mA的差模电流,会在3m外产生100μV/m辐射电场,而对共模电流来说,只需要8μA的电流就能产生同样程度的辐射。在进行远场分析时,必须考虑共模辐射。

3 加强防护

防护的强度,随产品的用途而定。对于无关紧要的电子产品,就不需要专门的

防护。而对于军用的电子产品及用于电厂与电网控制的电子设备,就需要加以最高等级的防护,因为即使是在极端情况下,也要保证这些设备能正常工作。

4 结论

在设计印制电路板时,必须考虑电磁兼容问题,以确保设计功能的实现。在高频时,简单的电路模拟可能不再适用,而需要用传输线理论或微波理论来分析遇到的问题。

编辑:hfy

-

pcb

+关注

关注

4324文章

23153浏览量

399088 -

电磁兼容

+关注

关注

54文章

1889浏览量

97938 -

信号完整性

+关注

关注

68文章

1415浏览量

95570 -

华秋DFM

+关注

关注

20文章

3494浏览量

4676

发布评论请先 登录

相关推荐

图文结合让你明白EMI电磁干扰传播过程

了解EMI电磁干扰的传播过程,才能轻松搞懂EMI

看懂EMI电磁干扰的传播过程

抑制传导和辐射电磁干扰 (EMI) 的实用指南和示例

五张图看懂EMI电磁干扰的传播过程

PCB如何抑制电磁干扰EMI的传播

PCB如何抑制电磁干扰EMI的传播

评论