从台积电到阿斯麦尔(ASML),一段时间以来美国频频借助各种手段,将商业问题政治化,打压中国的半导体行业。但《日本经济新闻》在10月21日的一篇评论里指出,随着半导体技术的革新,以及中国科技的发展,未来半导体技术的大趋势,其实有利于中国。

《日经》:半导体科技发展趋势,有利于中国 原日本半导体巨头尔必达社长,现中国芯片制造商紫光集团的高级副总裁坂本幸雄,在文中对中国半导体行业的前景尤为乐观:“当今世界,后来者拥有更好的机会,赶上现在的领导者。” 他还在文中援引一名中国商界人士的话说:“中国科技行业的领袖们现在感谢特朗普,因为他帮助他们下定决心,自主开发技术。” 文章指出,历史上技术范式的改变,常常能为行业的新参与者创造机会。如今,坂本幸雄也从当今半导体行业的技术趋势中,看出了这种趋势。

晶体管小型化遇瓶颈,3D技术崛起长期以来,半导体行业都受制于“摩尔定律”,即集成电路芯片上可以容纳的晶体管数目,大约每24个月便会增加一倍。但实际上,大约2005年前后,芯片表面晶体管和电路尺寸的缩小化之路遇到了瓶颈。当时,晶体管的尺寸已缩小至30纳米左右,而这一尺寸,是由一种叫做“栅极”(gate)的中央电极来衡量的。 随后,晶体管的小型化之路趋向缓慢。《日经》称,从32纳米到近期的10纳米,虽然芯片制造商一直在标榜芯片制程的缩小。但从2005年前后,这些数字不再是栅极的实际尺寸了。如今,所谓的“10纳米”或“7纳米”,只是芯片制造商的一种品牌标签。 例如,东京大学的平本俊郎教授就向《日经》表示,去年台积电制造的7纳米芯片,实际的栅极尺寸为18纳米左右。而这,已经与过去栅极尺寸也为32纳米的32纳米芯片,有了明显的偏差。

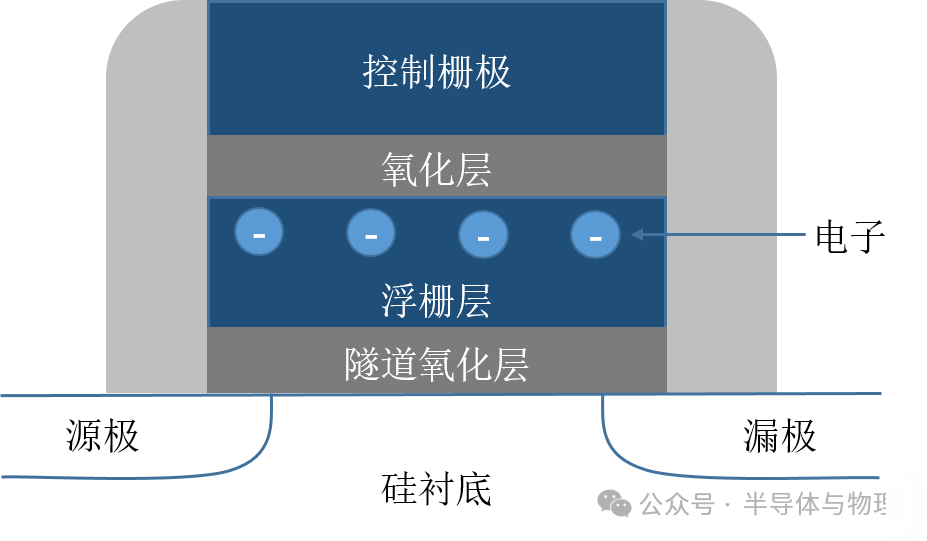

台积电生产的芯片 官方图 由于晶体管小型化的难度,以及成本都在不断上升,因此各大芯片制造商目前已转向一种三维技术,即利用传统晶圆表面上方的空间,将更多晶体管装载到芯片上。如今最先进的NAND闪存芯片,即在最底层的晶圆裸片上,堆叠了96至128层的集成电路。 随着层数的增加和芯片的增厚,晶体管的小型化过程在闪存领域发生了逆转。业内专家介绍称,如今闪存芯片的典型晶体管尺寸大约在22至 32纳米范围内,比几年前闪存芯片中使用的14纳米晶体管要大。 而这种芯片制造技术从晶体管小型化到三维技术的重要转变,可能会影响业界对芯片制造过程中最困难的部分——光刻技术的态度。 光蚀刻法是一种工艺,在硅晶圆的光敏表面上,通过一个称为光掩膜的玻璃板将光投射到硅晶圆上,在玻璃掩膜上可以画出电路计划的图像。这就像传统的照片显影过程,在透明胶片上捕捉到的图像,通过投射光线穿过负片,对准感光纸,将其印在纸上。 随着电路进一步小型化,这一过程需要短波光,来获得更好的分辨率。最先进的微型化技术需要超紫外或极紫外(EUV)光谱范围的不可见光。

从光刻机中“解放”《日经》称,如今阿斯麦尔是光刻机产业内的垄断企业,一台EUV光刻机的售价大约在1.2亿至1.7亿美元之间。然而,芯片制造商购买的阿斯麦尔光刻机,实际上只能应用于整个芯片制造过程的极小部分,也只能带来适度的微型化效果。

阿斯麦尔光刻机 阿斯麦尔官方图 如今,EUV光刻机只能用于制造逻辑芯片,如电脑的微型处理器,智能手机的系统芯片,以及游戏和人工智能领域的图形处理器等。由于由于电路组成的复杂性,逻辑芯片尚不能完全使用三维技术。 对芯片制造商来说,只为制造这些芯片就使用EUV光刻机,成本和难度可能并不那么合理。 实际上,如果一家芯片制造商要使用EUV光刻机,它还需要使用许多其他工艺,来优化EUV光刻技术,这就意味着厂商要投入大量资金,来购买各种先进设备。而装备越先进,供应商就越少,美国的禁令也就越有效。 但是,如今闪存芯片的制造过程已经可以跳过EUV光刻机。 并且,如果能跳过EUV光刻机的限制,那么芯片制造商的选择就更多了。《日经》称,日本佳能和尼康,如今也能生产非EUV光刻机。迄今为止,美国并未禁止这两家厂商对中国芯片制造商出货。 另一方面,包括华为在内,一些中国公司也一直在努力开发自己的光刻机。紫光集团旗下的长江存储也在今年宣布成功研发128层QLC3DNAND闪存(型号:X2-6070),并已在多家控制器厂商SSD等终端存储产品上通过验证。 《日经》认为,当前美国方面似乎将限制中国的重点放在EUV光刻机上,但中国正在积累三维芯片制造技术,这最终将应用于先进的逻辑芯片,帮助中国避免依赖基于EUV光刻机的芯片微型化。 并且,从长远来看中国有能力提高芯片所有相关领域的技术,如材料、光学、化学、晶圆制造过程控制、表面检测和功能测试等。 不少专业人士,也看好中国在芯片制造领域的潜能。曾在中芯国际担任首席技术官的生驹俊明表示,基于他在中国的经验,他认为中国有足够数量的有能力的科学家和工程师来开发自己的芯片制造设备和芯片设计软件。 东京科学大学教授若林秀树表示,开发芯片制造设备和材料的整个供应链不是一朝一夕就能完成的。但他表示,“中国有可能在10至20年内成为这一领域的主导国家,因为它在所有科学和工程领域都拥有大量人才。” 对中国这样的追赶者而言,技术趋势也是一个优势。信息技术分析机构高德纳公司(Gatner)研究副总裁萨缪尔·王(Samuel Wang)表示:“新技术,如新材料、3D、人工智能辅助芯片设计和基于云技术的制造协作,都将为新兴企业创造新的机会。”

责任编辑:lq

-

半导体

+关注

关注

334文章

26939浏览量

215283 -

晶体管

+关注

关注

77文章

9615浏览量

137728 -

人工智能

+关注

关注

1791文章

46736浏览量

237293

原文标题:日媒:半导体科技发展趋势有利于中国

文章出处:【微信号:guanchacaijing,微信公众号:科工力量】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

小型化晶振的影响有哪些

麻省理工学院研发全新纳米级3D晶体管,突破性能极限

3D-NAND浮栅晶体管的结构解析

NMOS晶体管和PMOS晶体管的区别

CMOS晶体管和MOSFET晶体管的区别

PNP晶体管符号和结构 晶体管测试仪电路图

三星2025年后将首家进入3D DRAM内存时代

YXC晶振 32.768KHz石英振荡器,封装3225,应用于3D打印机

M3芯片有多少晶体管

什么是达林顿晶体管?达林顿晶体管的基本电路

英特尔展示下一代晶体管微缩技术突破,将用于未来制程节点

什么是摩尔定律,“摩尔定律2.0”从2D微型化到3D堆叠

使用晶体管作为开关

晶体管小型化遇瓶颈,3D技术崛起

晶体管小型化遇瓶颈,3D技术崛起

评论