很多情况下,拍摄的视频会有不尽人意的地方,这就需要对视频进行视频处理(即帧图像处理)以达到所期望的效果。视频处理是一个庞大繁琐又耗时的工程,寻常视频处理都是在PC机上采用CPU+GPU的异构计算来进行;FPGA的出现及其高效的并行运算性能,使得CPU+FPGA的异构计算更加适合进行高强度的批处理运算,zynq系列兼具处理系统和可编程逻辑的SoC片上系统也使得使用FPGA进行视频处理这类运算需求量大的工程时更加得心应手。

进行帧图像处理设计随着客户需求的提高变得越来越复杂,复杂的设计变得越来越难以调试:在何处设置探针,重复进行编译,放置和布线,查看,重置探针,一遍又一遍。调试中重复过程花费时间过多,很少有时间调试根本原因。

虹科FPGA调试工具--VSTAR

此处我们展示虹科FPGA调试工具在视频处理设计中进行调试并大幅缩短调试周期的案例。 我们对视频的帧图像处理采用复杂程度中等的图像旋转算法,期望达到视频某片段旋转缩小至消失并链接下一视频片段的效果。 图像旋转算法映射到具有300 MHz AXI流和200 MHz AXI总线的Xilinx Kintex-7 FPGA K705开发板上。

视频处理流程框图

在设计中向图像旋转算法人为的注入会造成工程出现预期之外的逻辑错误,但可以正确通过编译、布局布线、综合和仿真。在VSTAR GUI 中打开该设计,注入VSTAR的验证IP并选定clk时间信号。

根据设计以及调试需要,选择了三组总线探针进行监测,VSTAR会根据选定的探针自动生成设计规则,当然如果发现自动设计的规则不太合适也可以自己手动进行设计规则的设定。

下载好bit流文件并运行后,VSTAR开始自动检测所选探针的错误情况,如果监测到设计规则之外的,并显示故障,通过GTKWave上的VCD向用户显示。

VSTAR用于图像旋转器有效信号的探针设置

VSTAR为图像旋转器的有效信号自动生成的规则之一

由下图监测结果可以看出,正常运转时,所监测的探针信号符合设计规则,但当达到人为设计的错误触发条件以后,图像旋转器出现信号跳转错误,违背了设计规则,由于设定错误缓存区为1次,所以此次出现错误后会直接结束监测,并展示VSTAR IP Status状态窗口,显示具体错误描述。

可根据出现错误的信号以及错误发生的时间去专向分析产生错误的原因,从而大幅缩短调试周期。

监测结果

责任编辑:xj

原文标题:虹科VSTAR缩短FPGA视频处理调试周期

文章出处:【微信公众号:FPGA技术支持】欢迎添加关注!文章转载请注明出处。

-

视频处理

+关注

关注

2文章

98浏览量

18802 -

FGPA

+关注

关注

1文章

24浏览量

15998 -

虹科电子

+关注

关注

0文章

593浏览量

14263

原文标题:虹科VSTAR缩短FPGA视频处理调试周期

文章出处:【微信号:HK-FPGA_Dep,微信公众号:FPGA技术支持】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

虹科方案 领航智能交通革新:虹科PEAK智行定位车控系统Demo版亮相

更强的无线(双)串口数据记录 调试工具

这个调试工具咋卖39.9?分析了原理后,我悟了

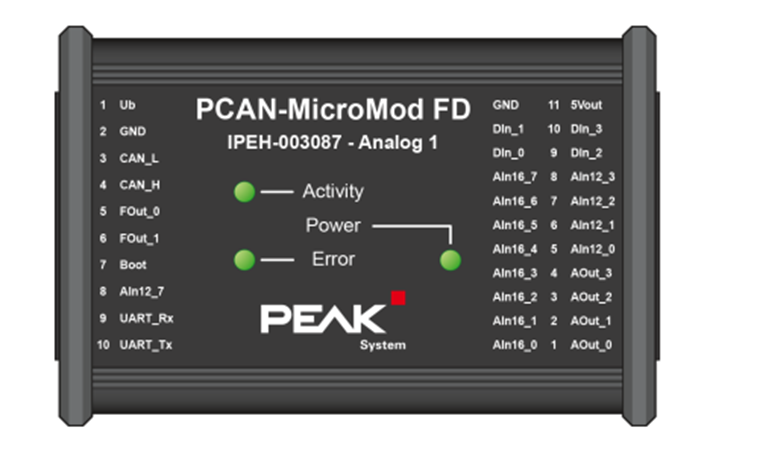

虹科案例|为什么PCAN MicroMod FD是数模信号转换的首选方案?

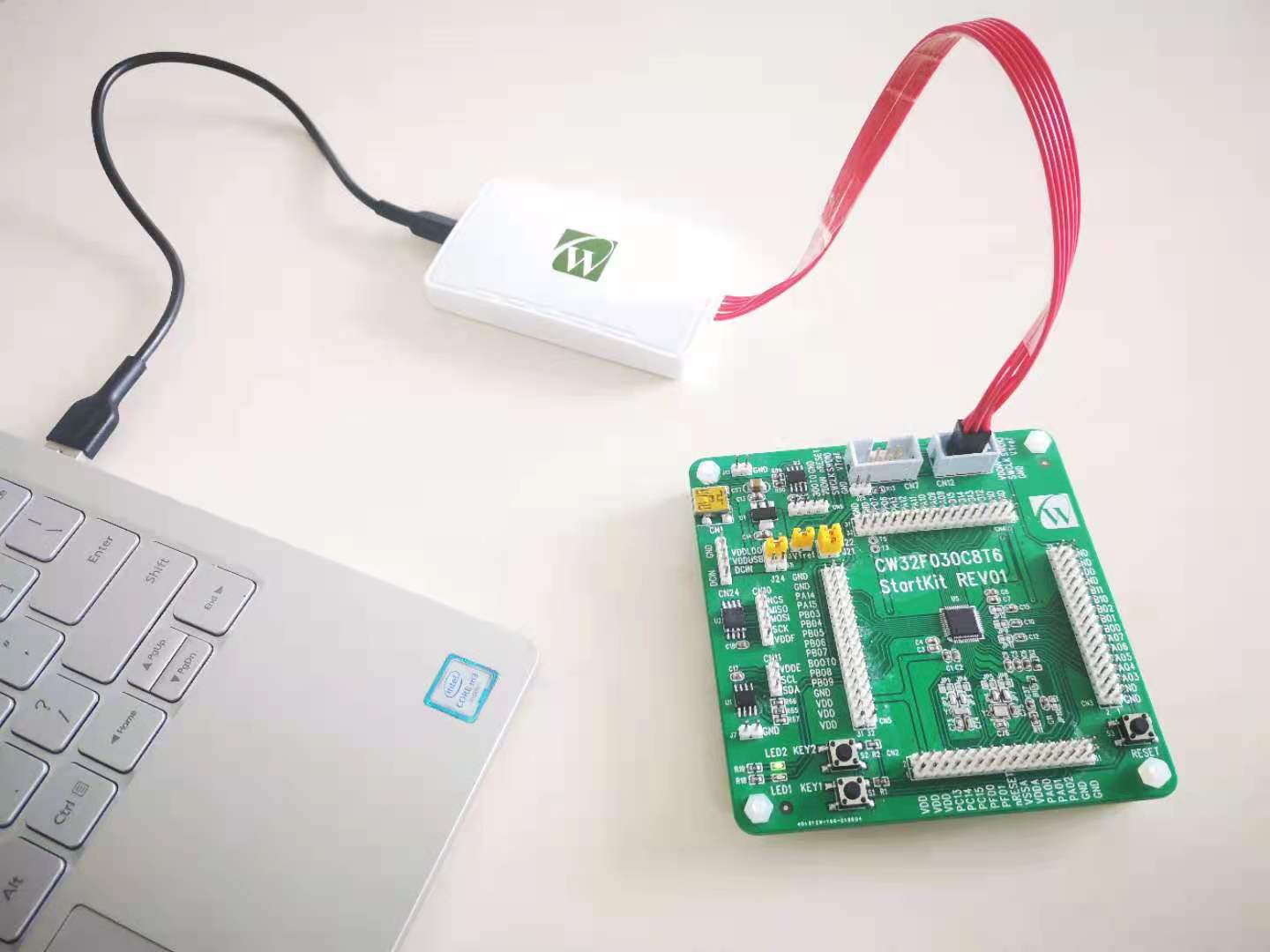

CW-DAPLINK调试工具

虹科FPGA调试工具:VSTAR

虹科FPGA调试工具:VSTAR

评论