在开始描述Non-project模式之前,我们要先确定执行的操作,通常包括如下操作:

设置芯片型号,设置源文件位置,设置生成文件位置,添加设计源文件,流程命令,生成网表文件,设计分析,生成bitstream文件。其中,流程命令是指综合、优化、布局、物理优化和布线。

设置芯片型号、源文件位置和生成文件位置如下图所示(文件名run_v1.tcl)。代码第5行设置了顶层模块的名字,第6行设置了源文件的位置,第7行设置了综合阶段生成文件的位置,第8行设置了实现阶段生成文件的位置。第10行至第14行则是实现阶段的每个子步骤的Directive。

责任编辑:lq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

459文章

51555浏览量

429739 -

TCL

+关注

关注

10文章

1759浏览量

89142 -

Vivado

+关注

关注

19文章

819浏览量

67255

原文标题:用Tcl实现Vivado设计全流程(2)

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Vivado FIR IP核实现

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件来破解。如果是个人学习,现在网络上流传的license破解文件在破解Vivado的同时也破解

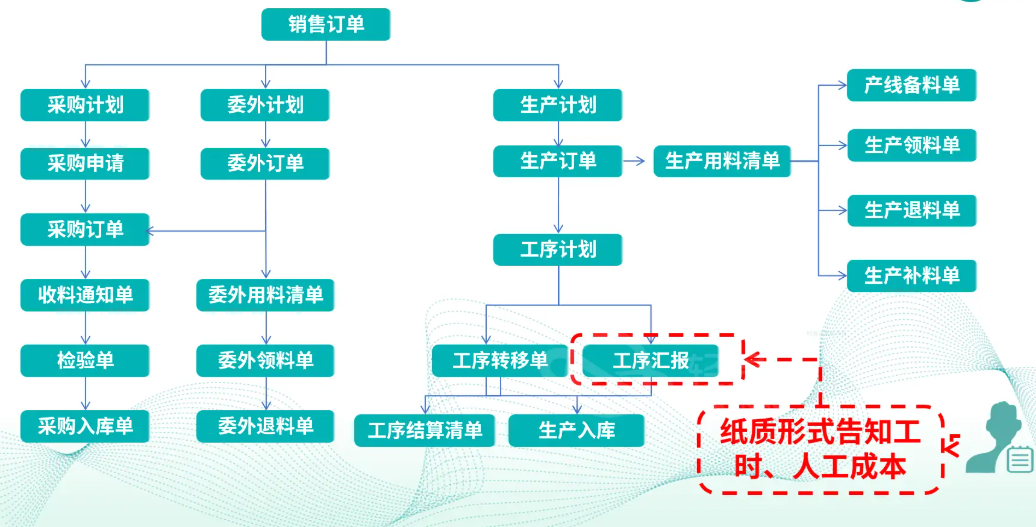

MES系统打通采购、生产、库存全流程

利用MES系统生产管理系统,实现了生产车间、仓库、采购等独立的生产主体的一体化管理,提高生产管理的效率。将MES系统和ERP系统结合在一起,形成一个企业的全流程的生产计划。

多个TCL5615通过菊花链实现级联时,DIN、CS、SCLK信号如何控制?

多个TCL5615通过菊花链实现级联时,DIN、CS、SCLK信号如何控制?或者说,如何编程实现级联(硬件已经完成)?级联控制的时序是怎样的?有参考示例代码吗?谢谢!

发表于 02-11 07:33

Vivado之实现布局布线流程介绍

一、前言 本文将介绍Vivado进行综合,以及布局布线的内部流程,熟悉该流程后结合Settings中对应的配置选项,对于时序收敛调试将更具有针对性。 二、Implementation(实现

每次Vivado编译的结果都一样吗

tool inputs? 对大多数情况来说,Vivado编译的结果是一样的,但要保证下面的输入是一样的: Design sources Constraints Tcl scripts and command

使用Vivado通过AXI Quad SPI实现XIP功能

本博客提供了基于2023.2 Vivado的参考工程,展示如何使用Microblaze 地执行(XIP)程序,并提供一个简单的bootloader。

Vivado使用小技巧

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整

Vivado编辑器乱码问题

,但是在Vivado里面打开用sublime写的代码之后,经常出现中文乱码,让人很不舒服。究其原因就是一般来说第三方的编辑器是采用utf8的编码方式,而vivado的text editor不是这种方式。

万界星空科技电线电缆MES系统实现线缆全流程追溯

万界星空科技电线电缆行业的MES系统通过高度集成的数据平台和强大的追溯功能,实现了线缆从原材料入库到成品出库的全流程追溯。

PCBA加工全流程解析:电子制造的关键环节

一站式PCBA智造厂家今天为大家讲讲PCBA加工流程的关键环节有那些?PCBA加工电子制造的关键环节全流程解析。在电子制造行业中,PCBA加工作为核心环节之一,承担着将电子元器件焊接到电路板上并组装

如何在AMD Vivado™ Design Tool中用工程模式使用DFX流程?

本文介绍了在 AMD Vivado™ Design Tool 中用工程模式使用 DFX 流程以及需要注意的地方。在使用 DFX 工程模式的过程中要把具体步骤映射到相应的 DFX 非工程模式的步骤,这样才能更好地理解整个流程的运行

深入探索Vivado非工程模式FPGA设计流程

在设计过程的每个阶段,设计者均可以打开Vivado集成开发环境,对存储器中保存的当前设计进行分析和操作。

发表于 04-03 09:36

•1226次阅读

用Tcl实现Vivado设计全流程

用Tcl实现Vivado设计全流程

评论