本周,Cerebras Systems证实其CS-1计算系统已达到新的性能里程碑,其速度远远超过现有CPU和GPU所能达到的速度。

CS-1基于Cerebras的WSE处理器(世界上最大的计算机芯片),现在可以称其是最快的AI计算机。

Cerebras的WSE拥有1.2万亿个晶体管,40万个核心,面积为46225平方毫米,片上内存18GB。

根据Cerebras和美国能源部国家能源技术实验室(NETL)的数据,CS-1比领先的GPU竞争对手快10,000倍,比在最新一期TOP500超算排名中排名第82位的Joule超级计算机快200倍。

“我们非常自豪与NETL合作,并在科学计算的一项基本工作上取得了非凡成果。” Cerebras Systems的联合创始人兼首席执行官Andrew Feldman解释说,

“这项工作为科学计算性能的突破打开了大门。CS-1及WSE克服了传统无法实现高性能、实时性以及拓展性的障碍。这是因为,晶圆级集成拥有了巨大的内存和通信加速,远远超出了独立单芯片处理器(无论是CPU还是GPU)所能提供的能力。”

交付新的CS-1有大量工作,涉及稀疏、结构化的线性方程组,这个系统可以用于许多实际场景进行建模,包括流体动力学和能源效率。

尽管CS-1的数据令人印象深刻,但使用这个芯片可以运行哪些应用仍然存在疑问,高速计算机建模似乎是可行的,而超级计算和人工智能未来的潜在交汇点也令人兴奋。

台积电已与Cerebras Systems达成合作,InFO(集成式扇出封装技术)衍生的工艺开始量产意味着台积电可能在两年内开始商业化生产专用于超级计算机的AI芯片。

这款从去年推出就备受瞩目的超级AI芯片若进入商业化,机器学习或将迈入新台阶。

责编AJX

-

芯片

+关注

关注

454文章

50460浏览量

421952 -

AI

+关注

关注

87文章

30238浏览量

268469 -

机器学习

+关注

关注

66文章

8382浏览量

132435

发布评论请先 登录

相关推荐

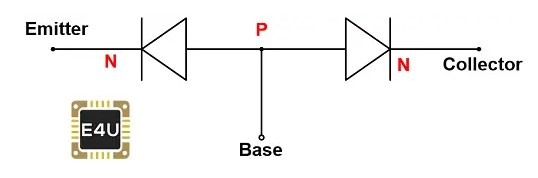

NMOS晶体管和PMOS晶体管的区别

芯片晶体管的深度和宽度有关系吗

世界第一AI芯片发布!世界纪录直接翻倍 晶体管达4万亿个

M3芯片有多少晶体管

什么是达林顿晶体管?达林顿晶体管的基本电路

晶体管Ⅴbe扩散现象是什么?

英特尔3D封装工艺进入量产,集成万亿晶体管

如何走向万亿级晶体管之路?

全球最大AI芯片竟有1.2万亿个晶体管

全球最大AI芯片竟有1.2万亿个晶体管

评论