据媒体报道,台积电将于2022年下半年开始量产3纳米芯片,单月产能5.5万片起,在2023年月产量将达到10.5万片。

据悉,台积电 N3 将继续使用 FinFET 鳍式场效晶体管,而不是过渡到 GAA 环绕式结构场效晶体管。这与三星不同,三星已经表示要在 3 纳米节点使用 GAA。台积电预计 N3 将在 2022 年成为最新、最先进的节点。与 N5 相比,收益同样不大,性能仅提升 1.1-1.15 倍,功耗提升 1.25-1.3 倍。与 7 纳米相比,N3 在同样的功率下,性能应该提高 1.25 倍 - 1.35 倍,或者在同样的性能下功耗降低 1.55 倍 - 1.6 倍。

责任编辑:pj

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

455文章

50714浏览量

423139 -

台积电

+关注

关注

44文章

5632浏览量

166408 -

晶体管

+关注

关注

77文章

9682浏览量

138080

发布评论请先 登录

相关推荐

台积电2纳米制程技术细节公布:性能功耗双提升

显著提升,提升幅度高达15%。同时,在功耗控制方面,N2制程也展现出了卓越的能力,功耗降低了30%,能效得到了大幅提升。 N2制程技术的卓越表现得益于多项创新技术的应用。其中,环绕式栅极(GAA)纳米片晶体管技术的引入,使得

台积电2nm制成细节公布:性能提升15%,功耗降低35%

的显著进步。 台积电在会上重点介绍了其2纳米“纳米片(nanosheets)”技术。据介绍,相较于前代制程,N2制程在性能上提升了15%,功耗降低了高达30%,能效显著提升。此外,得益

台积电2纳米制程技术细节公布

15%的显著提升,同时在功耗上降低了高达30%,能效表现尤为出色。这一进步主要得益于环绕式栅极(GAA)纳米片晶体管以及N2 NanoFlex技术的创新应用。 其中,N2 NanoFlex技术为制程带来了显著的

IBM与Rapidus在多阈值电压GAA晶体管技术的新突破

Rapidus 的 2nm 制程生产流程之中。 IBM 宣称,当制程推进到 2nm 阶段时,晶体管的结构会从长久以来所采用的 FinFET(鳍式场效应

高频晶体管在无线电中的应用

无线电技术是现代通信的基石,它依赖于无线电波的传输来实现信息的远距离传递。在这一领域中,高频晶体管扮演着至关重要的角色。 高频晶体管的工作原理 高频晶体管,通常指的是能够在较高频率下工

NMOS晶体管和PMOS晶体管的区别

NMOS晶体管和PMOS晶体管是两种常见的金属氧化物半导体场效应晶体管(MOSFET)类型,它们在多个方面存在显著的差异。以下将从结构、工作原理、性能特点、应用场景等方面详细阐述NMOS晶体管

英特尔竞购High-NA EUV设备,台积电决定回避

另一方面,台积电的年度技术论坛正在美国和欧洲如火如荼地进行,备受世人瞩目的是该公司计划在2026年量产A16技术,该技术将结合纳米片晶体管

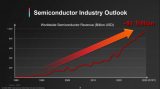

AMD与台积电联手推动先进工艺发展

展望未来,台积电正通过多个方向推动半导体行业持续发展:包括硅光子学的研发、与DRAM厂商在HBM领域的深度合作以及探索将3D堆叠技术应用于晶体管

如何提高晶体管的开关速度,让晶体管快如闪电

咱们今天讲讲电子世界的跑步选手——晶体管。这小东西在电子产品里就像是继电赛跑的选手,开关的速度决定了电子设备的快慢。那么,如何才能提高晶体管的开关速度呢?来一探究竟。如果把晶体管比作一

晶体管放大时,各级电位状态是什么

级。 在晶体管放大电路中,输入级负责接收输入信号,并将其放大输出给中间级。中间级继续放大信号并将其输出给输出级,最后输出级将信号放大到所需的幅值,并输出给负载。 在每个级别的晶体管中,

晶体管Ⅴbe扩散现象是什么?

晶体管并联时,当需要非常大的电流时,可以将几个晶体管并联使用。因为存在VBE扩散现象,有必要在每一个晶体管的发射极上串联一个小电阻。电阻R用以保证流过每个

发表于 01-26 23:07

如何走向万亿级晶体管之路?

台积电预计封装技术(CoWoS、InFO、SoIC 等)将取得进步,使其能够在 2030 年左右构建封装超过一万亿个晶体管的大规模多芯片解决

发表于 12-29 10:35

•346次阅读

台积电:规划1万亿晶体管芯片封装策略

为达成此目标,公司正加紧推进N2和N2P级别的2nm制造节点研究,并同步发展A14和A10级别的1.4nm加工工艺,预计到2030年可以实现。此外,台积电预计封装技术,如CoWoS、InFO、SoIC等会不断优化升级,使他们有望

台积电将继续使用 FinFET 鳍式场效晶体管?

台积电将继续使用 FinFET 鳍式场效晶体管?

评论