机载飞行参数系统和相关处理设备在地勤维护、飞行事故处理和飞行质量评估等方面发挥重要的作用。现在随着飞参设备使用频率增加,飞参数据卸载设备型号多、体积大、故障率高已经开始影响飞参的正常使用。

嵌入式技术的出现给开发和设计具有小型化、通用化、快速化和可靠性高的新型飞参卸载设备创造有利的技术条件。利用嵌入式技术可以提高飞参使用效率;通过简化操作步骤,采用与飞参地面处理相结合,飞参卸载变得更加便捷,设备可靠性大大增强。

1 嵌入式系统

嵌入式系统把计算机直接嵌入到应用系统中,融合了计算机软件、硬件、通信和半导体技术,是信息技术的终端产品。嵌入式系统是由嵌入式处理器、操作系统和应用软件组成。形象地说,嵌入式系统采用“量体裁衣”的方法把所需的功能嵌入到各种应用系统中,其硬件和软件都可以根据需要定制和集成。随着应用形式的不同,可有IP(International Property)级、芯片级和模块级三种体系结构。

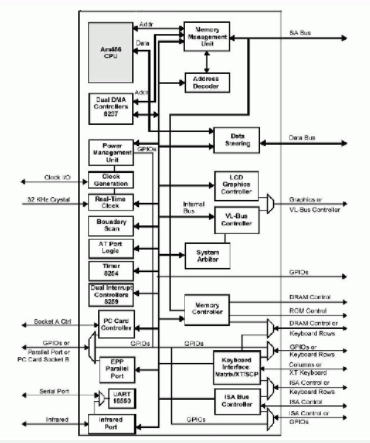

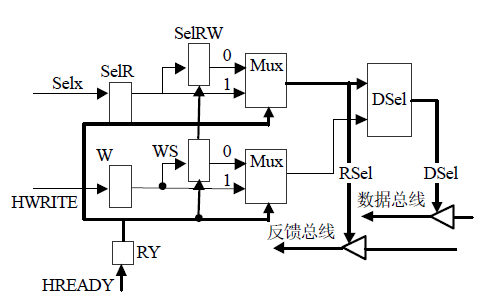

IP 级把不同单元进行集成,各种嵌入式软件也以IP的方式集成在芯片中;芯片级是根据各种IT产品的要求,选用相应的处理器芯片(含MCU、DSP、RISC和MPU)、RAM、ROM/ EPROM/ EEPROM/Flash和I/O接口芯片组成操作系统,系统软件也以固件形式固化在磁盘中;模块级以X86为处理器构成系统模块。Smart Core 是以Am486为内核的嵌入式CPU,完全兼容X86的指令集,具有32位、低功耗等特点,又称为E86体系。Smart Core功能框图如图1所示。

2 总体设计

手持式通用飞参快速卸载器是依托飞机装备的飞行参数系统,采用目前先进的嵌入式技术进行开发,重点实现飞参卸载设备的小型化、通用化、和性能高的特点。根据不同型号飞参的数据卸载协议、接口电路、通讯方式和数据记录方式的不同,采用了Smart Core嵌入式技术,根据一线使用的实际情况,在原有设备的基础上增加了数据预处理、数据备份、数据纠错等功能。

图1 Smart core功能框图

2.1 系统组成

软件部分是在DOS 操作平台下开发的应用程序,包括数据卸载软件、用户交互软件、LE屏显示和控制程序、硬件驱动程序以及其它辅助程序,采用DOS平台考虑到采用I/O口读取12位并行码,由于Windows系统采用多任务、多线程机制,实际输出的脉冲几乎无法捕捉到,不能实时检测到12位并行码。而操作系统采用DOS,则可以实时检测到12位并行码,以P -300微机为例,用C语言中的inportb函数反复读取就可以满足要求。

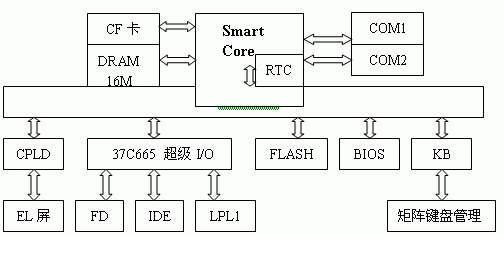

硬件由Smart Core小系统、矩阵键盘管理系统、扩展电路和外设组成。Smart Core小系统是硬件核心部分,是手持式飞参数据卸载设备的CPU,它以DL公司的Smart Core模块为主,配合相应的扩展电路组成。在该系统中扩展了数据存储卡、16M SDRAM、2个标准串口和ISA总线接口。在ISA总线基础上又扩展了2M Flash、键盘接口、并行口、显示屏和符合SDLC协议的串口。矩阵键盘管理系统由89C51单片机、外围电路和程序组成,用于管理矩阵键盘、将矩阵键盘转换为PC机标准PS2格式。该设备的外设为薄膜式按键和图形点阵式液晶显示器。

系统采用大规模可编程逻辑器件、自编字库、信息编排等技术,扩展了ISA用户总线结构,通过该总线连接键盘、显示屏、CF卡驱动器和卸载接口等外部设备。

2.2 系统原理框图

系统原理框图如图2所示。

图2 系统原理框图

2.3软件主要功能

卸载器软件具有数据卸载、通道校验、履历设置、飞参自检、本机自检等基础功能。

2.3.1具备飞参地面站预处理软件的功能,包括:数据格式转换、履历信息提炼、数据解压缩等,实现了数据卸载、预处理一体化,简化了地面数据卸载和预处理操作,解决了数据转录的瓶颈问题。

2.3.2增加了数据备份功能,在卸载数据的同时可将其备份到数据存储卡中,实现了飞参数据的双重备份。

2.3.3提供了“数据导出”功能,保证卸载器在离位状态下,可根据现场需要,将指定数据导出。

3 技术难点及解决特殊技术

3.1 嵌入式开发平台的底层驱动

系统采用先进的Smart core作为开发平台,Smart core开发出的手持式设备具有体积小、重量轻、功能强、功耗低、温度范围宽和稳定性高的优点[4]。与其他嵌入式开发平台相比,Smart core更为突出的优点是扩展CF卡和DOC比较方便。但以Smart core为核心的嵌入式技术是一项全新的技术,开发技术难度较大。在系统设计过程中,首先要从Smart core扩展出符合ISA规范的用户扩展总线,这条用户扩展总线是连接Smart core及SDLC通讯协议接口、显示接口、键盘接口和DOC接口的纽带。系统采用大规模可编程逻辑器件CPLD,扩展出了符合ISA规范的用户扩展总线。

3.2 产品的通用化设计

现役国产飞参系列和型号多,每个型号飞参的记录方式、数据记录格式、卸载模式各不相同,卸载器彼此不通用。通过对各型机载飞参设备进行测试、研究,设计出可自动识别飞参型号的软件自适应接口和可进行一体化卸载数据的通用转换电路,解决了同一卸载器不能卸载不同型号飞参数据的难题。

3.3 数据卸载及处理的快速化设计

原飞参卸载器是将机载飞参数据直接拷贝下来,不具备数据预处理功能,飞参数据必须由专业人员带回飞参处理室,利用专用软件进行解压、还原后,才能进行分析。根据有关规定,飞行日当天必须卸载飞参数据后进行处理,如果按照日出动15架飞机,每架飞机飞行5个起落计算,数据从卸载到处理结束,需要14个小时。

该卸载器采用数据同步预处理技术,按照地面处理软件接口的要求,在数据卸载的同时,完成数据格式转换、履历信息提炼和数据解压缩等预处理工作,保证录入到地面处理系统的数据可直接分析,利用该设备,从数据卸载开始至处理结束,仅用1小时。

3.4 手持设备的抗干扰技术

系统硬件组成复杂,结构紧凑。系统集成和电路交叉连接产生的空间辐射干扰、外接电源干扰等问题比较突出,为了保证系统的稳定性和可靠性,本系统采用了以下抗干扰技术:

3.4.1采用一点接地技术,选择壳体的接地点作为系统的参考“地点”与飞机壳体相连,其它电路的接地点都与该点相连。

3.4.2采用综合屏蔽技术,减小电磁波的辐射干扰。壳体在设计加工时,采用进口铝材作为原材料,并进行了表面导电阳极化处理,搭铁电阻小,减小了元器件间的辐射干扰。

3.4.3使用软件抗干扰技术,采取数字滤波、指令冗余、标志判断等措施提高系统的稳定性,消除程序可能发生的弹飞、进入死循环或死机状态。

4 结束语

目前,该设备已在多个单位得到成功推广。按现在飞机与卸载器配置比例计算,使用该设备后,可节约经费上千万元,每年还可节约维修费用近百万元。一线使用证明,该设备设计新颖,技术独特,携带方便,操作简单,为飞参专业发展开辟了一条崭新的途径,提高快速保障能力,具有明显的军事和经济效益。

责任编辑:gt

-

嵌入式

+关注

关注

5102文章

19261浏览量

309728 -

cpu

+关注

关注

68文章

10942浏览量

213784 -

计算机

+关注

关注

19文章

7572浏览量

89035 -

嵌入式CPU

+关注

关注

0文章

68浏览量

3752

发布评论请先 登录

相关推荐

基于嵌入式无线CPU短信通信终端系统的设计

嵌入式CPU指令Cache的设计与实现

Qtopia Core在嵌入式Linux上的移植及应用

基于ARM的嵌入式系统及SNMP的设计与实现

基于FPGA的嵌入式CPU的VHDL建模和设计

一种带Cache的嵌入式CPU的设计与实现

使用ARM核设计实现嵌入式CPU的AHB接口说明

基于嵌入式CPU Smart Core实现机载飞行参数系统的设计

基于嵌入式CPU Smart Core实现机载飞行参数系统的设计

评论