IC Compiler II作为新思科技Fusion Platform的一部分,凭借其行业领先的容量和吞吐量,加速了超大规模Colossus IPU的实现,该IPU拥有超过590亿个晶体管

RTL-to-GDS流程为AI硬件设计所需的创新优化技术提供了最佳性能、功耗和面积(PPA)

集成式黄金签核技术通过零裕度流程提供了可预测且可收敛的融合设计

新思科技(Synopsys)近日宣布,其行业领先的IC CompilerII布局布线解决方案成功协助Graphcore实现第二代Colossus MK2 GC200智能处理单元(IPU)芯片的一次性流片成功。该IPU采用了业界先进的7nm工艺技术,集成594亿个晶体管。新思科技IC Compiler II拥有针对AI硬件设计的超高容量架构和创新技术,其RTL-to-GDS流程与最先进的功耗优化能力,以及PrimeTime延迟计算器等嵌入式黄金签核技术,为Graphcore设计团队提供了优越的PPA和最快的设计收敛时间,从而加快了Graphcore大规模AI处理器设计的实现。

“新思科技的数字全流程解决方案(包括Design Compiler和IC Compiler II在内的业界一流RTL-to-GDS工具)提供了单一供应商所能提供的最全面设计平台,这对我们最新的Colossus IPU按时流片至关重要。与新思科技的长期合作使我们能够利用IC Compiler II的最前沿技术,实现先进AI处理器的性能与功率目标。我们相信,基于与新思科技在IC Compiler II和Fusion Compiler上的持续合作,我们将不断拓展机器智能计算的极限。”

——Graphcore

硅业务副总裁

Phil Horsfield

Graphcore推出的第二代Colossus GC200 IPU是一款精密芯片,集成了1472个独立处理器核和超过900兆字节的片上存储,为数据中心规模的AI应用提供卓越的并行处理能力。新思科技的IC Compiler II拥有适配AI设计的多项功能,其顶级互连规划、逻辑重构、拥塞驱动的mux优化、全流程并发时钟以及数据优化,为复合AI加速芯片中典型的高度重复、基于MAC的拓扑,提供了同类设计的最佳PPA。

此外,它还具有自适应抽象化和分布式实现的原生高容量数据模型,可以在快速周转时间内高效处理数十亿个实例设计。IC Compiler II具有独特的最终签发引擎主干,可提供最高的相关性和超高度收敛的设计,从而进一步加快设计周转时间。

“AI计算的设计复杂性极限正在不断被突破,比如Graphcore最新推出的Colossus IPU,它成功利用了IC CompilerII中最新的AI优化技术,同时满足了最复杂芯片的多个设计目标,这进一步巩固了作为下一代AI设计首选布局布线工具的领先地位。”

——Neeraj Kaul

工程设计事业部副总裁

新思科技

责任编辑:lq

-

处理器

+关注

关注

68文章

19299浏览量

230007 -

晶体管

+关注

关注

77文章

9698浏览量

138294 -

AI芯片

+关注

关注

17文章

1887浏览量

35058

原文标题:594亿颗晶体管的7nm工艺AI芯片,一次性流片成功的王牌武器—ICCII

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

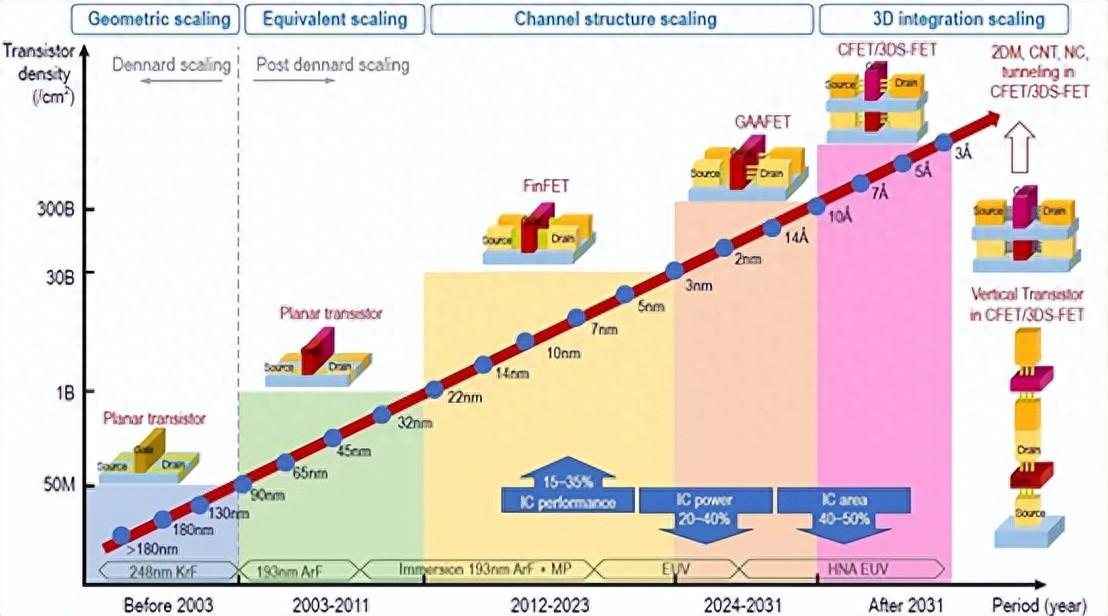

7纳米工艺面临的各种挑战与解决方案

MOSFET晶体管的工艺制造流程

所谓的7nm芯片上没有一个图形是7nm的

CMOS晶体管的尺寸规则

NMOS晶体管和PMOS晶体管的区别

GaN晶体管和SiC晶体管有什么不同

芯片晶体管的深度和宽度有关系吗

微电子所在《中国科学:国家科学评论》发表关于先进CMOS集成电路新结构晶体管的综述论文

晶体管的分类与作用

2024年全球与中国7nm智能座舱芯片行业总体规模、主要企业国内外市场占有率及排名

苹果M3芯片有多少晶体管组成

晶体管和集成电路是什么关系?

什么是达林顿晶体管?达林顿晶体管的基本电路

业界先进的7nm工艺技术,集成594亿个晶体管

业界先进的7nm工艺技术,集成594亿个晶体管

评论