今天来说说高端处理器的基本知识,开发32位单片机首先要了解基本芯片的硬件基础,所以今天就讲讲基于STM32的硬件资源。

STM32基础硬件知识

STM32与单片机的硬件接口基本一致,都是调用硬件接口控制I/O,完成相应的功能。另外,STM32在软件方面具有ST官方的源代码开放的库文件,开发速度相对轻松方便,而且BUG较少。

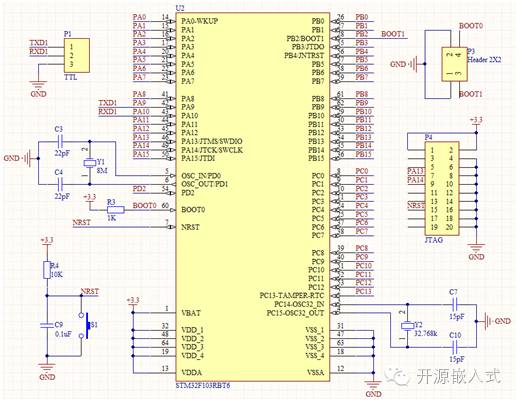

本文以STM32F103为例对STM32的硬件资源进行介绍。

1、STM32最小系统

72 MHz -40~105°C ,有内置的ARM核心,因此它与所有的ARM工具和软件兼容, 128k 闪存。

NVIC 嵌套的向量式中断控制器---可处理43个可屏蔽中断通道(不含16个中断线)和16个优先级。

EXTI 外部中断/事件控制器,含19个边沿检测器,用于产生中断/事件请求。

时钟和启动复位时内部8MHz的RC振荡器被选为默认的CPU时钟,有多个预分频器用于配置AHB的频率、高速APB(APB2)和低速APB(APB1)区域。AHB和高速APB 的最高频率是72MHz,低速APB的最高频率为36MHz。

低功耗模式:睡眠,停机,待机

DMA可以用于主要的外设:SPI、I2C、USART、通用和高级定时器TIMx和ADC。

通用同步/异步接受发送器(USART)

ADC(模拟/数字转换器)::内嵌2个12位的模拟/数字转换器(ADC),每个ADC有多达16个外部通道。

VDD:器件内部的工作电压,芯片的工作电压(Vcc>Vdd)

VCC:电路的供电电压。

VSS:电路公共接地端电压——接地端——接地点

图1-STM32F103最小系统

2、启动选择

图1中上部的BOOT0和BOOT1用于设置STM32的启动方式,其对应启动模式如下表所示:

表1- BOOT0、BOOT1启动模式表

| BOOT0 | BOOT1 | 启动模式 | 说明 |

| 0 | X | 用户闪存存储器 | 用户闪存存储器,也就是FLASH启动 |

| 1 | 0 | 系统存储器 | 系统存储器启动,用于串口下载 |

| 1 | 1 | SRAM启动 | SRAM启动,用于在SRAM中调试代码 |

用串口下载代码时,则配置BOOT0为1,BOOT1为0即可,如果想让STM32一按复位键就开始跑代码,则需要配置BOOT0为0,BOOT1随便设置都可以。

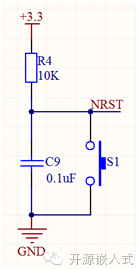

3、复位

图2-按键复位电路

STM32支持三种复位方式,分别是系统复位、上电复位和备份区域复位

系统复位:除了时钟控制器的RCC_CSR寄存器中的复位标志和备份区域中的寄存器以外,系统复位将复位所有寄存器的至它们的复位状态。当发生以下任一事件是产生系统复位:

(1)NRST引脚上的低电平(外部复位);

(2)窗口看门狗计数终止(WWDG复位);

(3)独立看门狗计数终止(IWDG复位);

(4)软件复位(SW复位);

(5)低功耗管理复位。

可以通过查看RC_CSR控制状态寄存器中的复位状态标志位识别复位时间来源。

当以下事件中之一发生时,产生电源复位:

(1)上电/掉电复位(POR/PDR复位);

(2)从待机模式中返回。

备份域复位:

当以下事件中之一发生时,产生备份区域复位:

(1)软件复位,备份区域复位可由设置备份域控制寄存器(RCC_BDCR)中的BDRST位产生;

(2)在VDD和VBAT两者掉电的前提下,VDD或VBAT上电将引发备份区域复位。

4、 IO口

图1中STM32的PORTA、PORTB以及PORTC的IO口全部引出,以便于与外部设备连接。

STM32每个GPIO 端口有两个32 位配置寄存器(GPIOx_CRL,GPIOx_CRH),两个32位数据寄存器(GPIOx_IDR,GPIOx_ODR),一个32 位置位/复位寄存器(GPIOx_BSRR),一个16 位复位寄存器(GPIOx_BRR)和一个32 位锁定寄存器(GPIOx_LCKR)。

GPIO 端口的每个位可以由软件分别配置成多种模式,如下所述。每个I/O 端口位可以自由编程,然而I/O端口寄存器必须按32 位字被访问(不允许半字或字节访问)。GPIOx_BSRR 和GPIOx_BRR 寄存器允许对任何GPIO 寄存器的读/更改的独立访问;这样,在读和更改访问之间产生IRQ 时不会发生危险。端口位配置 CNFx[1:0]=xxb,MODEx[1:0]=xxb

对于STM32的IO口可以根据需要由软件配置成八种模式(模电中有相关电路的具体分析):

(1)GPIO_Mode_AIN 模拟输入;

(2)GPIO_Mode_IN_FLOATING 浮空输入;

(3)GPIO_Mode_IPD 下拉输入;

(4)GPIO_Mode_IPU 上拉输入;

(5)GPIO_Mode_Out_OD 开漏输出;

(6)GPIO_Mode_Out_PP 推挽输出;

(7)GPIO_Mode_AF_OD 复用开漏输出;

(8)GPIO_Mode_AF_PP 复用推挽输出。

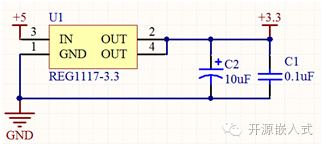

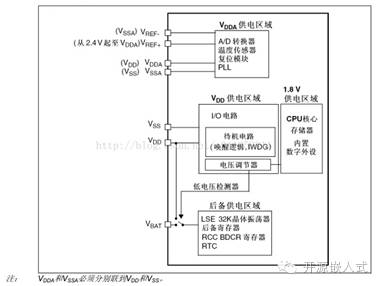

5、电源

图3-电源电路

这里STM32的供电采用的是REG1117-3.3的方式,将DC5V电源转换成为DC3.3V电源,电容作用都是一样滤出电路中寄生的杂波,不同电容的容值通过的频率不一样所以电路中用了不同容值的电容把所有的杂波对地短路。可以在DC5V端增加两个滤波电容(滤波电容通常是一大一小配合使用),基本形式是:电容滤波—三端稳压—电容滤波。

图4-STM32电源框图

Vdda是为模拟部分供电的,如果不接Vdda,芯片应该无法运行。

STM32的工作电压(VDD)为2.0~3.6V。通过内置的电压调节器提供所需的1.8V电源。当主电源VDD掉电后,通过Vbat脚为实时时钟(RTC)和备份寄存器提供电源。如果应用中没有使用外部电池,VBAT必须连接到VDD引脚上面。

供电方案:

VDD=2.0~3.6V:VDD管脚提供IO管脚和内部调压器的供电;

VSSA,VDDA=2.0~3.6V:为ADC、复位模块、RC振荡器和PLL的模拟部分供电。使用ADC时,VDD不得小于2.4V;

VBAT=1.8~3.6V:当(通过电源开关)关闭VDD时,为RTC、外部32KHz振荡器和后备寄存器供电。

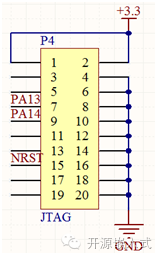

6、烧写接口

图5-JTAG接口电路

如果要减小插座的数量,就用SWD模式的仿真,在这个模式下,如果用JLINK只要四根线就可以了,这四根线分别是:3.3V、GND、SWDIO(PA13)、SWCLK(PA14)。

其中:

STM32的JTMS/SWDIO接JTAG口的TMS;

STM32的JTCK/SWCLK接JTAG口的TCK。

如果要用ULINK2,则再加多一条“NRST”,即5条。

STM32的SWD接口与JTAG是共用的,只要接上JTAG,就可以使用SWD模式了(其实并不需要JTAG这么多线),JLINKV8和ULINK2都支持SWD。

这个接口可自行定义,在使用时用杜邦线跳接或做块转换接口板联接仿真器与目标板即可。

7、时钟与晶振

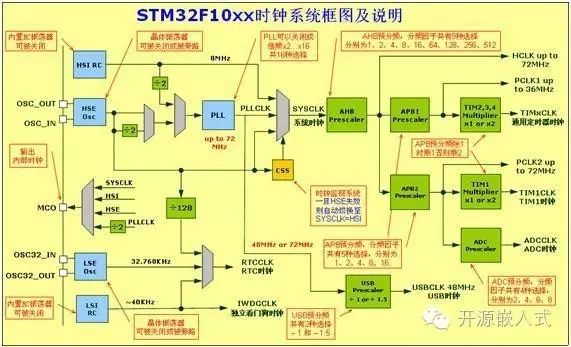

在STM32中,有五个时钟源,分别为HSI、HSE、LSI、LSE、PLL。其实是四个时钟源,如图6所示(灰蓝色),PLL是由锁相环电路倍频得到PLL时钟。

(1)HSI是高速内部时钟,RC振荡器,频率为8MHz。

(2)HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

(3)LSI是低速内部时钟,RC振荡器,频率为40kHz。

(4)LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

(5) PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

图6-STM32时钟系统框图

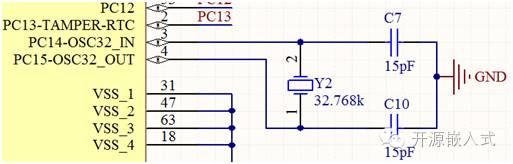

对于单片机系统来说,CPU和总线以及外设的时钟设置是非常重要的,因为没有时钟就没有时序。由于时钟是一个由内而外的东西,具体设置要从寄存器开始。一般板子上只有8Mhz的晶振,而增强型最高工作频率为72Mhz,显然需要用PLL倍频9倍,这些设置都需要在初始化阶段完成。一般性的时钟设置需要先考虑系统时钟的来源,是内部RC还是外部晶振还是外部的振荡器,是否需要PLL。STM需要2个晶振,1个是HSE,常用外部高频,PLL倍频用,常8MHz;另一个为外部低频晶振,系统待机或低功耗时用,为32.6KHz。外接的那个用于 RTC 的32768 晶振,需要专用的负载晶振。

图7-STM32外部晶振电路图

然后考虑内部总线和外部总线,最后考虑外设的时钟信号。遵从先倍频作为CPU时钟,然后在由内向外分频,下级迁就上级的原则有点儿类似PCB制图的规范化要求,在这里也一样。

本文对STM32 的硬件部分做大致介绍,设计时用到其它的具体知识后期会陆续进行补充介绍,并附实例程序。

责任编辑:lq

-

ARM

+关注

关注

134文章

9100浏览量

367762 -

STM32

+关注

关注

2270文章

10903浏览量

356297 -

硬件设计

+关注

关注

18文章

397浏览量

44578

原文标题:【值得学习的好文章】经典的STM32硬件设计学习笔记

文章出处:【微信号:KY_QRS,微信公众号:开源嵌入式】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

讲讲基于STM32的硬件资源

讲讲基于STM32的硬件资源

评论