对于金融分析来说,洞察时间是预测风险、为客户做出明智商业决策和提供差异化金融服务的关键,这些金融服务有助于您在竞争中脱颖而出。Xilinx 平台提供高适应性、高灵活性以及急需的计算能力,可显著缩短您的洞察时间。

Vitis 定量金融库提供优化功能,为金融工作负载(如期权定价、建模、交易、评估和风险管理等)构建加速计算解决方案。

该库旨在为应用、软件及硬件开发人员提供 3 个层次的抽象和灵活性。库 API 是预先编译的加速器,可直接在主机应用中调用。库内核和原语可作为独立的加速器编译,也可结合其它 Vitis 加速库(如数学、统计学、线性代数)及 Xilinx 合作伙伴库,加速您的自定义端到端处理流水线。

Vitis 定量金融 API (L3) 可在您的 C、C++ 或 Python 主机应用中直接调用,非常适合针对 Xilinx 能够为定量金融工作负载带来的性能优势快速进行原型设计和评估。使用这些预先构建的加速器,不需要预先具备硬件设计经验,也不需要学习曲线。应用实例包括定价模型,如赫斯顿有限差分和蒙特卡洛布莱克斯科尔斯欧美模型等,而且该列表还在不断扩增。

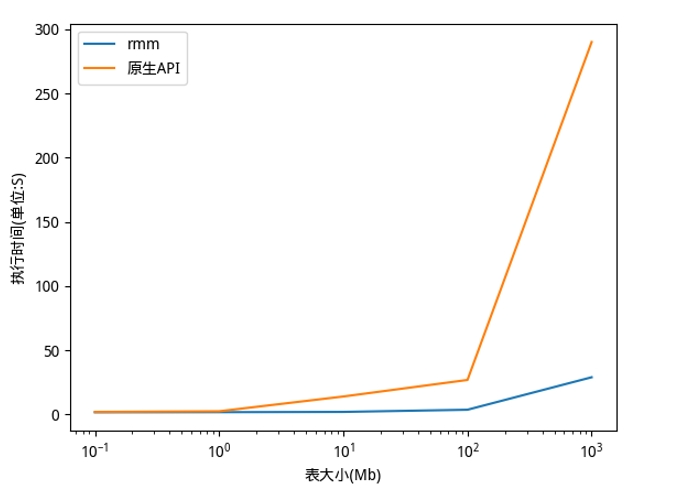

性能基准

CPU: 2 Intel Xeon CPU E5-2690 v4 @3.20GHz,每个处理器 8 个内核,每个内核 2 个线程。

Xilinx:Vitis 定量金融库 v1.0 在 1 Alveo U250 运行

冷运行:定价引擎在响应请求时启动。

热运行:定价引擎已经运行,分配了足够的内存来处理请求

责任编辑:xj

原文标题:Vitis 定量金融库解决方案

文章出处:【微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

-

Xilinx

+关注

关注

72文章

2174浏览量

123201 -

API

+关注

关注

2文章

1535浏览量

62958 -

Vitis

+关注

关注

0文章

147浏览量

7638

原文标题:Vitis 定量金融库解决方案

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

优化800G数据中心:高速线缆、有源光缆和光纤跳线解决方案

使用AMD Vitis进行嵌入式设计开发用户指南

鸿蒙原生页面高性能解决方案上线OpenHarmony社区 助力打造高性能原生应用

利用NVIDIA RAPIDS加速DolphinDB Shark平台提升计算性能

忆联SSD存储解决方案亮相2024中国国际金融展

润和软件金融搜一搜解决方案认证成功

曙光与合作伙伴携手为金融AI的发展提供新动力

在Windows 10上创建并运行AMD Vitis™视觉库示例

AI快讯:华为助力金融行业加速拥抱AI 马斯克xAI 展示首个多模态模型

中科驭数超低时延网络解决方案入选2023年度金融信创优秀解决方案

Vitis定量金融库提供优化功能,加速计算解决方案

Vitis定量金融库提供优化功能,加速计算解决方案

评论