一块四层板PCB的层压和阻抗计算调整建议

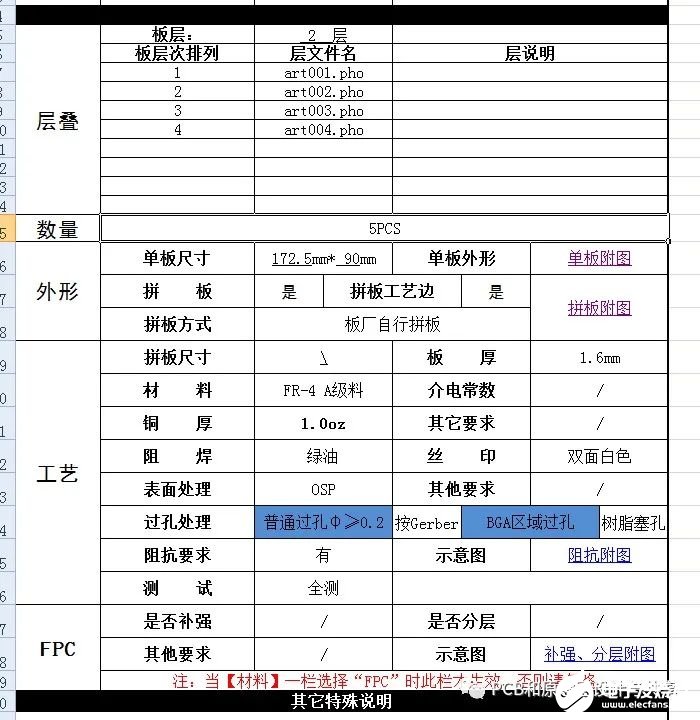

最近设计了一块四层板PCB,因为是高速电路,有阻抗匹配的要求,所以在发给pcb板厂打样时,特定指定了哪些线要做阻抗线。我自己给出的做板要求是这样的。

有阻抗匹配要求的线有单端的50欧姆射频线,有90欧姆的USB差分线,也有100欧姆的DDR差分线,如下图所示,

50欧姆射频线阻抗要求:

90欧姆usb差分线和100欧姆DDR差分线阻抗要求:

我自己简单计算了上述阻抗线的阻抗,半固化片用2116,参考平面的高度按4.5mil来算,介电系数用4.2,铜厚1zo。单端射频线线宽走6mil,间距10mil,算出单端走线的阻抗是50.47欧姆。

usb差分线线宽走了5mil,间距是5mil,线到地的间距是6mil,算出来的结果是88.96欧姆。

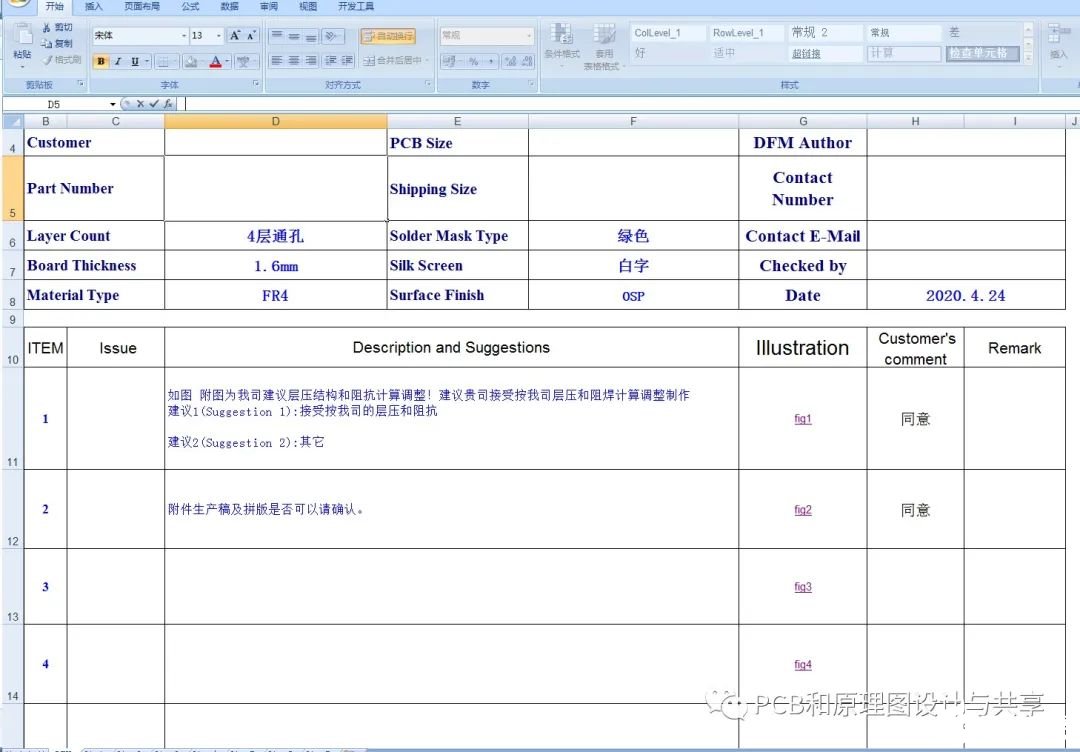

之后板厂评估后反馈回来的层压和阻抗计算调整建议是这样的,

从板厂反馈回来的信息可以知道,板厂用的板芯厚是1.3mm,半固化片用的是

3313PP,厚度是0.1mm,换算成mil应该是大概是4mil。

50欧姆单端射频线不需要调整,按照板厂的层压方式算出的阻抗是51.77欧姆,可以满足阻抗要求

90欧姆usb差分线需要由原稿的5mil线宽,5mil间距调整到5.5mil线宽,4.5mil间距,计算出来的阻抗是89.89欧姆,才能满足要求。

100欧姆的DDR差分线不需要调整,按照板厂的层压方式算出的阻抗是99.42欧姆,满足要求。

编辑:hfy

-

pcb

+关注

关注

4319文章

23107浏览量

398162 -

阻抗

+关注

关注

17文章

958浏览量

46001 -

DDR

+关注

关注

11文章

712浏览量

65367 -

高速电路

+关注

关注

8文章

158浏览量

24246

发布评论请先 登录

相关推荐

如何解决PCB设计中的阻抗匹配问题

高速PCB设计中的阻抗匹配

10层板PCB,内层信号层(5,6)阻抗匹配如何选择参考层?

高频高速PCB设计中的阻抗匹配,你了解多少?

PCB阻抗匹配计算工具(附教程)

高速PCB中的阻抗匹配

怎样理解阻抗匹配_pcb阻抗匹配如何计算

关于四层板PCB设计阻抗匹配的要求和建议

关于四层板PCB设计阻抗匹配的要求和建议

评论