1 引言

本课题来源于一个无纸记录仪的项目。在该项目中要求无纸记录仪中有一路通道将工业现场采集到的频率信号测量并显示出来。传统的测频系统大多采用单片机加逻辑器件构成,而这类测频系统存在测频速度慢、准确度低、可靠性差的缺点,故而使测量仪表达不到工业现场的要求。鉴于此,本文设计了一种基于嵌入式微处理器SEP3203和FPGA的测频系统。将嵌入式微处理器灵活的控制功能与FPGA的设计灵活、高速和高可靠性的特点有机结合,从而达到工业现场的实时测量要求,而且该测频系统具有可重构性。

2 测频原理

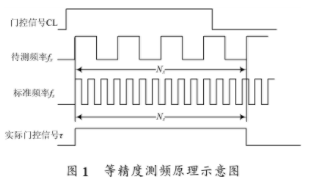

常用的直接测频方法主要有测频法和测周期法2种。测频法就是在确定的闸门时间tw内,记录被测信号的变化周期数(或脉冲个数)Nχ,被测信号的频率为fχ=Nχ/tw。测周期法需要有标准信号的频率fs,在待测信号的一个周期内tχ,记录标准频率的周期数Ns,被测信号的频率为fχ=fs/Ns。这2种方法的计数值会产生±1个字的误差,并且测试精度与计数器中记录的数值Nχ或Ns有关。为了保证测试精度,一般对于低频信号采用测周期法,对于高频信号采用测频法,这样测试时很不方便,所以人们提出了等精度测频的方法。

等精度测频方法是在直接测频方法的基础上发展起来的,他的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,消除了对被测信号计数所产生±1个字的误差,达到了在整个测试频段内保持等精度测量。

在测量过程中,有2个计数器分别对标准信号和被测信号同时计数。首先给出闸门开启信号(预置闸门上升沿),此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。然后预置闸门关闭信号(下降沿)到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成1次测量过程。从而实现了实际门控信号与被测信号的同步,进而消除对被测信号计数产生的一个脉冲的误差。

设在1次实际闸门时间τ中计数器对被测信号的计数值为Nχ,对标准信号的计数值为Ns。标准信号的频率为fs,则被测信号的频率为:

fχ=(Nχ/Ns)×fs (1)

3 误差分析

由式(1)可知,若忽略标频的误差,则等精度测频可能产生的相对误差为:

δ=(fχ-fe/fe)×100% (2)

其中,fe为被测信号频率的准确值。在测量中,由于fχ计数的起停时间都是由该信号的上升沿触发的,在闸门时间τ内对fχ的计数Nχ无误差(τ=Nχtχ);对fs的计数Ns最多相差1个数的误差,即│△Ns│≤1,其测量频率为:

fe=[Nχ/(Ns+△Ns)]/fs (3)

将式(1)和式(3)代入式(2),并整理得:

δ=│△Ns│/Ns≤1/Ns-1/(τ×fs) (4)

由上式可以看出:测量频率的相对误差与被测信号频率的大小无关,仅与闸门时间和标准信号频率有关,即实现了整个测试频段的等精度测量。闸门时间越长,标准频率越高,测频的相对误差就越小。标准频率可由稳定度好、精度高的高频晶体振荡器产生,在保证测量精度不变的前提下,提高标准信号频率,可使闸门时间缩短,即提高测试速度。

4 设计实现

(1)前级电路

即首先对待测信号进行处理使其达到与后级电路相兼容的脉冲信号。

第一级电路是由开关三极管组成的零偏置放大电路,以保证放大电路具有良好的高频响应,当输入信号为零或负电压时,三极管工作在截止状态,输出为高电平,当输入为正电压时,三极管工作在饱和状态(导通),输出电压随输入电压上升而下降。零偏置放大电路把如正弦波样的正负交替波形变换成单向脉冲,这使得该电路可以测量任意方波信号、正弦波信号、锯齿波信号、三角波信号等频率。

第二级采用的是施密特非门触发器CC74HC14,是对放大器输出的信号进行整形,使其输出的信号成为与后级电路相兼容的脉冲信号。

(2)后级电路

各模块用硬件描述语言Verilog HDL描述,通过EDA工具(ModelSim,Synplify,QuartusⅡ)进行编译、仿真、延时分析、管脚调整、综合等步骤,最后烧录到FPGA芯片中。将芯片与被测信号的放大整形模块等外围电路相连接,通过调试便完成了整个设计。

工作过程表示如下:

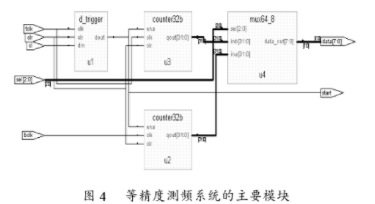

d_trigger实体实现门控信号和被测信号TCLK同步控制功能,内部有一个受被测信号TCLK上升沿同步的D触发器和预置门控信号CL共同作用产生实际的门控信号。counter32b1和counter32b2分别对标准频率BCLK和被测频率TCLK计数,内部为带异步复位的32位二进制计数器的时序进程。mux64_8是数据选择器,根据地址信号se1不同取值,64位数据依次从data_out[7:0]端输出。

即当CLR为1,D触发器及两个计数器清零。当预置门控信号CL为1时,及经放大整形后的被测信号TCLK上升沿到来时,同步电路输出dout=1,带使能端的2个计数器开始计数;当预置门控信号CL为0时,被测信号TCLK下一个上升沿到来时,同步电路输出dout=0,即ena1=ena2=0,2个计数器停止计数。然后根据地址信号se1不同取值,64位数据依次从data_out[7:0]端输出送入后端的乘法器和除法器模块,按公式计算出被测频率的值。

(3)嵌入式微处理器读取测频结果

本系统采用东南大学国家集成电路工程中心自主研发的嵌入式微处理器SEP 3203,并通过JTAG仿真器连接到PC机上的集成调试环境(IDE)软件平台,在IDE中统一完成C语言的编辑、编译、连接。IDE选择了ARM公司的开发软件ADS 1.2,利用处理机的Embedded-ICE性能,通过JTAG接口实现实时的仿真调试。整个系统具有高性能、低功耗、低成本的特点。

FPGA与嵌入式微处理器SEP 3203之间采用总线的方式进行数据交换,也就是将FPGA看作总线上的一个并行外部设备。FPGA通过一个SRAM接口与嵌入式微处理器SEP 3203相通信。即从嵌入式微处理器SEF‘3203的角度来看,FPGA与嵌入式微处理器SEP3203之间的通信就相当于SEP 3203与一个SRAM之间的通信。在程序中读写指定区域的地址,可以实现对FPGA的读写操作。

处理器SEP 3203的外部存储器接口(EMI)提供了6个可配置的片选信号:CSA,CSB,CSC,CSD,CSE,CSF,用来实现对ROM,SRAM,NOR FLASH的片选。其中CSE,CSF、可以配置成SDRAM片选信号。FPGA模块使用的是CSB片选信号。CSB片选的默认地址范围为0x24000000~0x27FFFFFF,即FPGA组成的外设映射在SEP3203的地址空间为0x24000000~0x27FFFFFF,所以SEP3203在访问FPGA时只需读写该地址空间中的任何一个地址,SEP3203能自动产生相应的总线操作,从而读取到FPGA的测频结果。

5 仿真及验证

例1:标准频率Fs为1 MHz;待测频率Fχ为1 kHz。

看出Ns=0x7DOH=2 000;Nχ=0x2H=2,故测得频率Fχ=(N=/Ns)*Fχ=1 kHz。

例2:标准频率Fs为1 MHz;待测频率Fχ为7.288 kHz。

看出Ns=0x80AH=2 058;Nχ=0xFH=15,故测得频率Fχ=(Nχ/Ns)*Fs=7 288.630 Hz。

采用等精度频率测量方法测量精度保持恒定,不随所测信号的变化而变化,再结合FPGA集成度高、高速和高可靠性的特点,使频率的测频范围可达到0.1~1×10 8Hz,测频全域的相对误差恒定。

6 结语

本测频系统将嵌入式微处理器灵活的控制功能与FPGA器件的结合,突破了传统电子系统的设计模式,使系统开发速度快、成本低、系统性能大幅度提高。因此,在目前的电子设计中,充分利用嵌入式微处理器+FPGA结构将起到事半功倍的效果。

责任编辑:gt

-

FPGA

+关注

关注

1625文章

21639浏览量

601355 -

嵌入式

+关注

关注

5060文章

18983浏览量

302297 -

微处理器

+关注

关注

11文章

2246浏览量

82275

发布评论请先 登录

相关推荐

SEP3203处理器的FPGA数据通信接口设计

SEP3203与伪彩LCD驱动SSD1770的接口设计

SEP3203处理器与FPGA数据通信接口设计

基于嵌入式Linux的无纸记录仪通信设计

基于SEP3203拉力试验机嵌入式测控系统设计

基于SEP3203和FPGA实现无纸记录仪测频系统的设计

基于SEP3203和FPGA实现无纸记录仪测频系统的设计

评论