12月10日,中国集成电路设计业2020年会在重庆隆重举行,台积电(中国)副总经理陈平指出,5G和AI是新时期的核心技术,对性能和功耗都有极高的要求,因此必须有先进工艺的支持。而5G和AI产生的大量数据需要落地,与万物互联,这些需要各种特殊工艺来实现,8英寸传统工艺比12英寸工艺需求不遑多让。因此,5G和AI会带动整个晶圆代工行业。

陈平表示,新冠疫情是2020年突发的大灾难,但由于防疫的需要,新冠疫情还产生了一些良性的副作用,其中之一就是对数字化进程的推进,例如线上办公、线上学习、测温安防等领域实现了飞跃式发展。

“现在是数据大量提升的时代,这些数据的处理都需要晶体管,因此晶体管数量也在随着数据而开始以惊人的速度增长。”陈平说。

陈平指出,晶体管数量的增长通过工艺来实现主要有两个路径,第一个路径就是沿着摩尔定律在单片上延伸,第二个路径就是通过3D集成。目前,世界上最大的GPU已经拥有了500亿个晶体管,而用3D集成的最大芯片拥有2000亿个晶体管。但随着工艺的日新月异发展,这些记录很快也会被打破。

陈平强调,大数据的爆炸式增长对工艺的进步提出了极高的要求,因此工艺的进步一定要追赶上市场需求。

目前,很多的应用都有高能效和集成度两大要求。陈平表示,为了实现这两点,先进工艺是不二选择。以智能终端、5G网络、边缘计算和云计算为例,大多数芯片都需要先进工艺来支持。

全产业都在关注先进工艺能否继续沿着摩尔定律下探,以支持应用的要求。陈平指出,台积电的先进工艺在全行业的支持下,依然能保持以往的发展速度。台积电的5nm工艺已经经过了3个季度的量产,无论在产出还是良率上都表现优异。另外,3nm研发也非常顺利,预计明年完成验证,并于后年实现大批量生产,更先进的2nm研发也在如火如荼的进行当中。

陈平还指出,晶体管的微缩有几大要素,其中最主要的就是光刻技术。从以往光波长为一百多纳米的DUV来处理十几二十纳米的器件,到现在用13.5nm光波长的EUV来处理5nm和7nm,晶体管微缩已经实现了跨越。从光刻技术角度来看,EUV可以保证先进工艺下探到2nm以下。

除了光刻,器件结构和器件材料也是晶体管微缩的两大要素。陈平表示,FinFET结构可以支持到3nm工艺,3nm以后目前也出现了器件结构的新选择,包括nanowire和nanosheet。材料方面,纯粹的硅材料在3nm以后迁移率会快速降低,好在科技人员创造出了新的2D材料,提供更佳的迁移率。

“摩尔定律什么时候终结,我个人认为没有答案,我们永远不能低估人类的创造力。当我们遇到困难的时候,总有科学家会找到新的答案。”陈平如是说。

责任编辑:tzh

-

台积电

+关注

关注

44文章

5639浏览量

166541 -

晶圆

+关注

关注

52文章

4914浏览量

128007 -

晶体管

+关注

关注

77文章

9694浏览量

138229

发布评论请先 登录

相关推荐

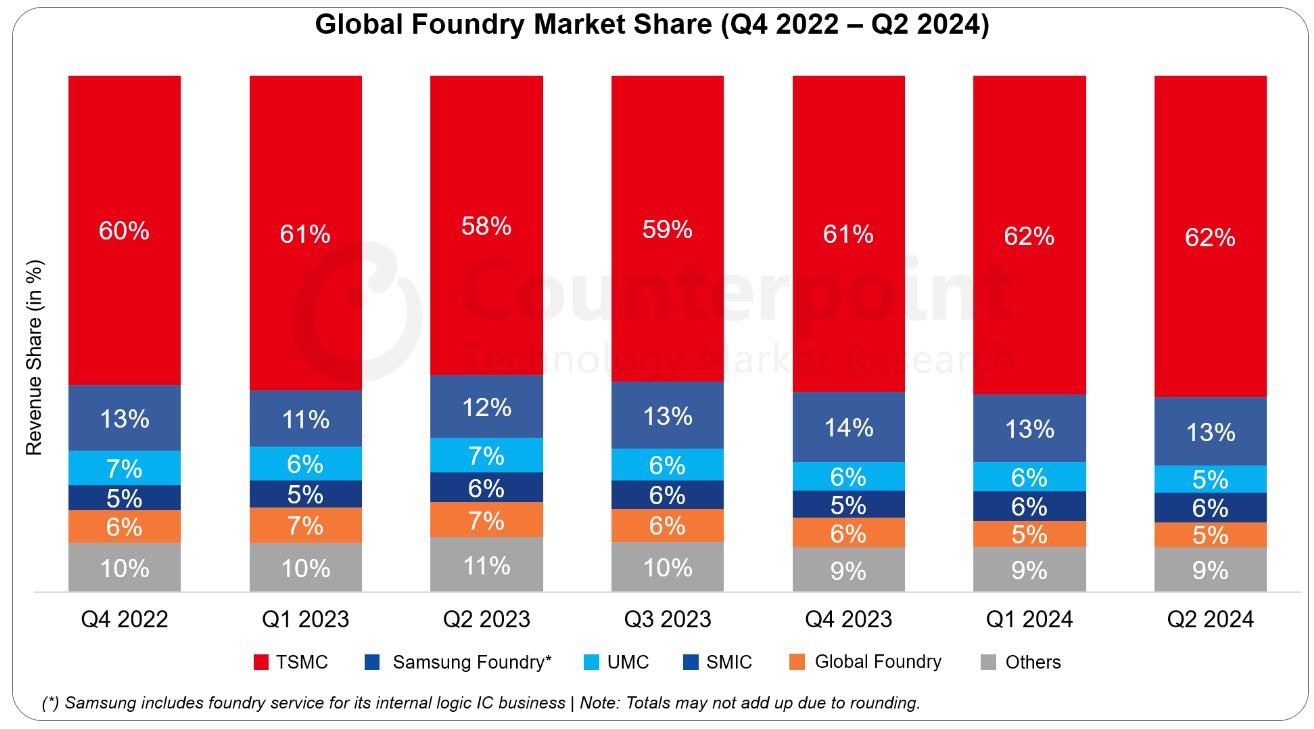

台积电引领全球晶圆代工热潮,明年产值料增逾二成

人工智能需求持续爆发,全球晶圆代工行业势头强劲

三星晶圆代工发力,挑战台积电地位

晶圆代工迎来复苏,各大厂商展现出回升势头

5G智能防爆手持终端在石油化工行业中扮演着什么角色?

中国大陆晶圆代工市场复苏,特定制程或迎涨价潮

中芯国际跻身全球第三大晶圆代工厂,季收入首次超越联电、格芯

全球晶圆代工行业2024年Q1营收下降,AI需求驱动增长

晶圆代工厂密集降价抢单,原因究竟为何?

5G和AI将带动整个晶圆代工行业发展

5G和AI将带动整个晶圆代工行业发展

评论