学习电子工程的过程中离不开大量的实验和动手练习,就如同开车一样,学习理论数载,如果从来没有打几把方向盘,踩几脚油门然后再被教练紧急刹车几次,仍然不会开车。正所谓,看别人做一百次,不如自己练一次。

1

门电路原理

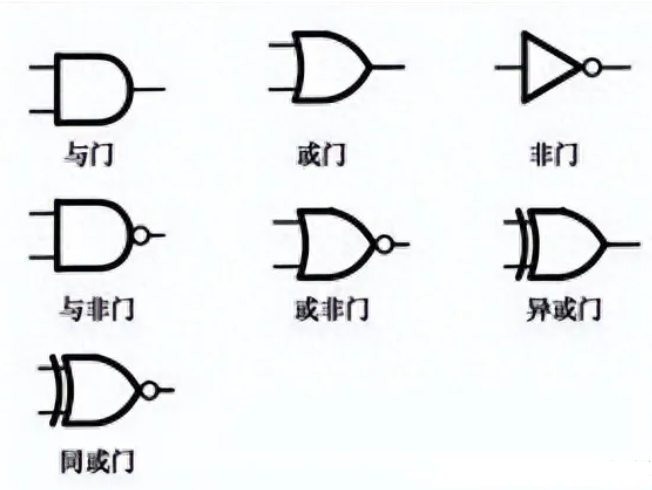

在数字电路中,门电路是最基本的构成单位,可以说,任何复杂的数字电路系统都可以通过我们耳熟能详的与门,非门,或门,与非门,异或门等等组合实现。

对于各种门电路的逻辑特征,想必大家都掌握得炉火纯青,脑海里可以毫无压力地随时浮现着各种0和1的组合。

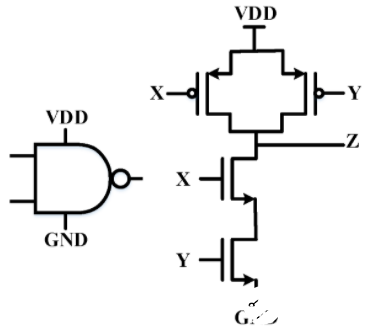

然而,搭建一个门电路实验却并不容易!我们以下面的与非门电路为例。

图1 与非门电路

表1 与非门真值表

传说中,如果想做一个与非门的数字电路实验,可以通过以下两种方法:

热爱模电的朋友们可以通过MOS管+面包板+电源+跳线以及若干小时的反复调试。

土豪朋友们对此不屑一顾,直接拍几千块买一台数字电路实验仪。

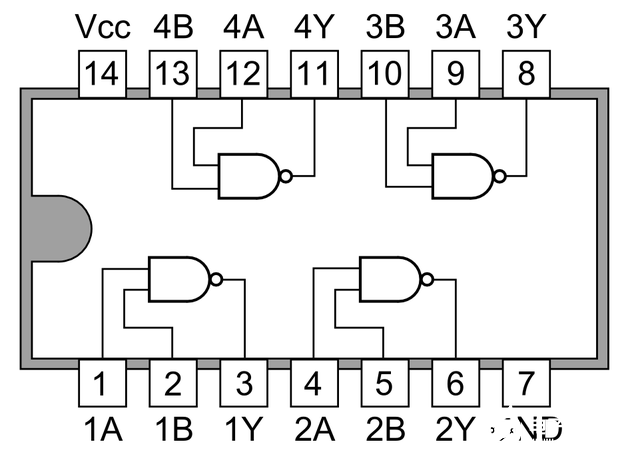

当然,既没有那么热爱模电,也没有那么多软妹纸的朋友门仍然有更合适的办法,那就是通过逻辑芯片。比如大家熟悉的7400系列的逻辑芯片,只需要接上电源,再配上开关,LED等器件,就可以通过实验方式对与非门的逻辑和电气特性进行直观地学习,比如采用7400 Quad2的与非门逻辑芯片。

图2 与非门逻辑芯片

因为我们要观察实验现象,因此需要配上开关和LED灯,使得实验可以可视化。当然,作为习惯了课上学习1+1=2,考试见到

的后浪,肯定不能满足于这个简单的实验。现在,在上一个练习的基础上,我们来尝试构建以下门电路组合。

图3 组合门电路

嵌入式专栏

2

门电路实现

以下是某位同学独特的实现方式:

图4

虽然我们还通过软件仿真的方式构建上述电路并观察波形,然而和电路上进行实打实的操作相比终究是有质的差别。毕竟靠着模拟飞车驾龄20年资历上路还是要被警察叔叔带走的。

不难看出,画门电路容易,对门电路进行实验很难,对各式各样奇葩组合的门电路进行实验更是难上加难。然而这一切在FPGA面前都只是谈笑风生。

FPGA,英文全称Field Programmable Gate Array,是一种可以通过某百科或搜索引擎查找到并且看了之后不明觉厉的东西。在此,我们主要介绍一下FPGA的部分特点,以及如何使其与数字电路实验进行结合。

首先问大家一个问题:我们在计算3x7=21或者5x8=40的时候,有谁是通过最原始的乘法原理推导并计算出来的,如果有,请在底部留言并获得所有人的膜拜。相信大部分人都可以在半秒内给出准确答案,为什么?因为我们都背过九九乘法表,只要是在这个范围内的任意乘法我们的大脑都可以瞬间对应出计算结果。相信大家对当年的11²=121,12²=144,13²=169…等等还历历在目。

之所以我们可以在一定范围内进行准确和快速的计算,是因为我们的大脑里储存了一个拥有大量数据的查找表,在一定范围内的输入数据我们都可以迅速在表中找到对应答案。其实,FPGA的运算处理方式就类似于我们的大脑。它拥有一个可以储存大量数据的查找表,只要我们通过程序定义出输入与输出之间的逻辑关系,FPGA就可以按照该逻辑关系自行对其内部结构进行重新定义,直白地说,就是我们可以随时给FPGA进行洗脑,而后者可以永远不计回报,心甘情愿地被洗脑。

接下来我们就快速展示一下如何通过FPGA展示图3所示的门电路。既然要对FPGA进行洗脑,肯定需要语言。在这里我们采用简单通俗的Verilog语言,通过描述门电路的方式,以16行代码轻松在FPGA上搭建上述门电路。

module custblock ( input wire A, //定义输入A input wire B, //定义输入B input wire C, //定义输入C input wire D, //定义输入D output wire Y1, //定义输出Y1 output wire Y2 //定义输出Y2 ); wire s1,s2,s3; //定义中间变量 nand (s1,A,B); //(输出,输入,输入) or (s2,C,D); // 调用基本门电路 xnor (Y1,s1,C); and (s3,C,s2); xor (Y2,C,s3); endmodule

将上述代码导入FPGA之后,就等于在FPGA上构建出了一个模块,输入端分别是A,B,C,D,输出端分别是Y2,Y1,且内部结构和图3中所示的功能完全一样。

图5

不过,对于实验来说,仅仅在FPGA上搭建出该门电路模块还是不够的,我们还需要允许实验者对该电路进行调试并观察现象,因此还需要有相应的可操作/观察元件与FPGA配合使用。接下来就是我们备受欢迎的小脚丫FPGA登场的时候了。

图6 小脚丫FPGA核心板

从示意图中可以看出,小脚丫FPGA带有多个板载外设,如开关,LED和数码管等,可以对绝大部分数字电路进行生动的实验操作。小脚丫配有USB下载器,可以通过一根USB线实现供电和程序下载。板上的36个多功能I/O接口可以进行项目扩展,且封装采用DIP40尺寸,因此可以与面包板完美结合。

以下是通过我们小脚丫FPGA对该电路进行的实验。我们采用板载的4个拨码开关和2个LED(低电平亮)分别作为模块的4路输入和2路输出,并且通过调节输入来观察输出结果。上下两图分别所对应的输入分别为:0001和0101,我们也观察到了在两种情况下的LED状态。

责任编辑:haq

-

FPGA

+关注

关注

1630文章

21796浏览量

605652 -

电路

+关注

关注

172文章

5962浏览量

172844 -

核心板

+关注

关注

5文章

1029浏览量

29917

发布评论请先 登录

相关推荐

基于FPGA数字门电路的实现

基于FPGA数字门电路的实现

评论