简介

在超声及成像等各类系统中,模拟信号的电压有时可能突然达到极限值。而诸如ADC驱动器之类的多种下游电路可以对模拟输入信号电平进行限制,以维持其性能。在过驱条件下,这类器件可能过度吸取电流,也可能被驱动至饱和状态,从而延长恢复时间。

在这类系统中,可以利用多种箝位放大器来对输出端的信号偏移进行限制,以保护下游器件。目前,多数箝位放大器都依赖于一种称为输出箝位放大器(OCA)的输出箝位架构。一种被称为输入箝位放大器(ICA)的新型架构可提供更高的箝位精度和更低的失真。

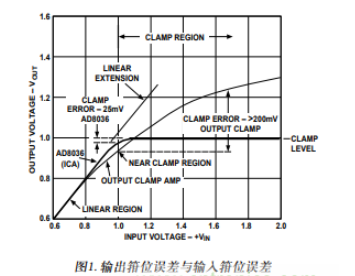

图1显示了两种器件的相对性能。可以看出,在线性区,ICA更接近直线,进入箝位区后有所弯曲。另一方面,OCA在接近箝位电压时,偏离直线的时间更早。当然,响应更接近直线的程度显示了放大器在该区的线性度。

目标最大偏移稍宽,以最大限度降低失真。因此,用ICA取代OCA时,箝位区可以较窄而不增加额外的失真。这样做可以降低下游电路在过驱过程中的电压。在多数设计中,进行这样的调节只需要对产生箝位电压的电路略作修改即可。

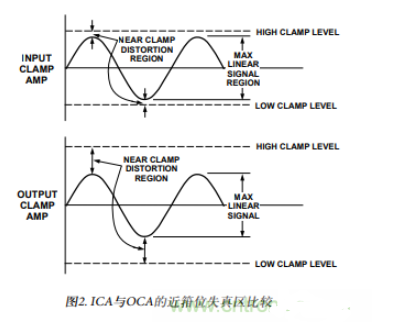

图2即显示了这种概念。各类放大器的线性信号幅度都是相同的。但是,由于近箝位失真区较大,必须将OCA的箝位电平上下限设得稍宽一些,以保持信号的线性度。因而,在过驱条件下,下游电路在由OCA驱动时,信号将大于ICA驱动的情况。

另外,由于ICA具有更出色的过驱特性,结果将进一步改善过驱响应。对于低增益箝位级,ICA输出偏移箝位设定电平的值不会超过10 mV。另一方面,OCA的过冲将达几百毫伏,具体取决于过驱信号的大小。同样,图1显示了这种概念。显然,ICA在箝位区的性能相对平坦,不受过

驱幅度的影响,而OCA输出则随过驱幅度加大而增加。

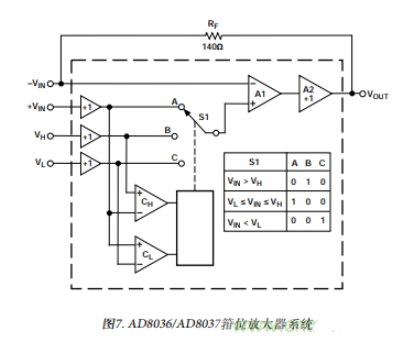

ADI推出的前两款输入箝位放大器AD8036和AD8037采用ICA结构。但是,由于它们在工作原理方面存在差异,除了工作增益为+1的电路,在设计中以ICA取代OCA并不是“直接”替代即可,尽管两种器件的引脚排列都是相同的。但是,由于二者的引脚排列相同,一般而言,不需要对电路进行太多修改。不过,对于每种状况都必须对每种配置单独处理。下面将详细讨论进行这种替换时需要考虑的因素。

反相工作

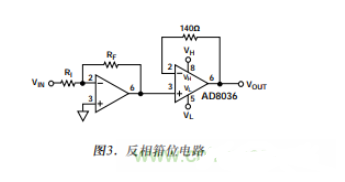

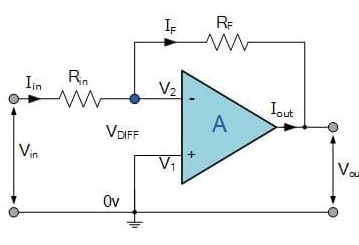

需要考虑的第一个因素是运算放大器的工作极性。AD8036和AD8037的输入箝位运算放大器架构不是反相工作模式。因此,不能直接用适用于反相配置的ICA取代OCA。为了在反相应中发挥出ICA的出色箝位特性,必须采用一个独立的反相级。

图3所示电路中,反相级之后为ICA,即同相配置的AD8036,用于提供反相箝位放大器的整体功能。图中所示电路的增益为–RF/RI,箝位电压为VH和VL。有关箝位级的工作原理,将在下节进一步讨论。在所有箝位电路中,VH必须大于VL,但二者可以为器件输出范围内的任何值。

对于要求增益大于(-)1的电路,设计人员可以选择如何在反相级与箝位级之间分配增益。为获得最高精度,应降低ICA的工作增益,因为箝位精度是增益的函数,对此下一节将详述。需要的额外增益可以在反相级中提供。

同相工作

单位增益

对于取代同相OCA的情况,最重要的考虑因素是箝位放大器的工作增益,因为ICA的输出箝位电平是放大器闭环增益的函数。

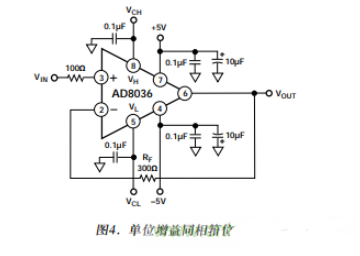

首先需要考虑的是同相单位增益。对于OCA,箝位电平等于施加于VH (引脚8)和VL(引脚5)的电压。对于ICA,将这些电压值乘以闭环增益可以算出箝位电平。但是,由于增益为+1,因而ICA和OCA的箝位电平将相等。因此,可以直接进行替换。图4为单位增益箝位电路示例。

由于这里讨论的是同相单位增益,因此,所选的放大器也必须在单位增益下具有稳定的工作性能。在前面提到的两种ICA中,AD8036针对单位增益进行过补偿。因此,可以用AD8036直接取代同相单位增益应用中的OCA。该器件将在相同电平下提供与OCA相同的增益和箝位。

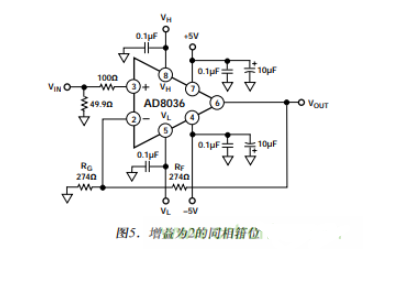

增益为2或大于2

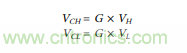

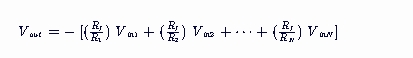

当箝位放大器的同相增益等于或大于2时,可以使用带宽较宽的AD8037,因为该器件针对等于或大于2的噪声增益进行过补偿。然而,要保持箝位电平不变,必须改变施加于箝位引脚的电压,因为箝位电平是放大器闭环增益的函数。利用以下等式即可算出正确的箝位电压:

其中: VCH 为输出箝位电平上限

VCL 为输出箝位电平下限

G 为放大器配置的增益

VH 为施加于VH (引脚8)的电压

VL 为施加于VL

(引脚5)的电压

一般地,为了使箝位电平维持于采用OCA时的水平,施加于任一箝位引脚的电压应设为箝位电平除以放大器闭环增益之商。例如,如果放大器的工作增益为2,且其箝位电平上限为1V,则施加于VH(引脚8)的电压应为1V/2,即0.5V。类似地,如果需要将箝位电平下限设为–1V,则施加于VL(引脚5)的电压应为–1 V/2,即–0.5 V。图5所示为增益为2的AD8037的箝位级。

由此可以推断出,箝位电路中的输入失调将随运算放大器级的增益倍数倍增。为了获得最佳箝位精度,箝位放大器应设为低增益,需要的任何额外增益则于箝位级之前的另一个增益级提供。现实情况下,对于增益不超过10的箝位级,利用ICA都可以实现优于OCA的精度。

有关近箝位区失真的讨论仍然适用。箝位窗口必须稍大于最大信号偏移,以尽量减少失真。ADC将在待转换最大信号电平与最大过驱信号电平之间形成一个区间,在该区间中其指标不会受到影响。箝位电平即应设在这一区域之内。

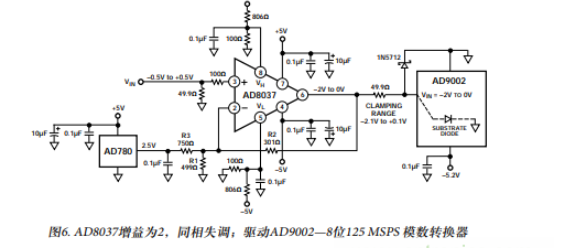

失调箝位

有些运算放大器应用需要在输出端提供直流失调电压。这些一般配置为反相模式,其失调可能由直流电压产生,该电压通过求和电阻相加而得,并作为放大器的额外输入。由于ICA不支持反相模式箝位,因而这种配置不能箝位。可以设计同相电路,同时提供增益和失调。然而,由于用来改变增益和失调的电阻之间存在相互作用,其设计不如反相配置简单。

图6显示了AD8037的一种同相配置,同时提供箝位和失调。电路所示为AD9002的驱动器,这是一种8位125 MSPS模数转换器,图中展示了采用具有失调和箝位功能的AD8037时需要考虑的因素。AD9002的模拟输入范围为地电压至–2V之间。输入偏移该范围的值不能太大,以避免吸收过多电流。在地电压附近,输入具有对称性,其幅度为1 V p-p。

为使AD8037在增益为2的条件下正常工作,我们依据数据手册选用了一个301 Ω的反馈电阻。当增益为2时,R1和R3两个并联电阻必须等于反馈电阻R2。因此R1 × R3/(R1 + R3) = R2 = 301 Ω用于提供失调的基准器件为AD780,其输出为2.5V。为了算出R3的值,先假定同相输入端的输入为0V。这会强制反相输入同样为0V,该值为–1V(与输入中点对应的范围中点),因此,R2中的电流为1V/301Ω或3.32 mA。由于电流不会流入R1或运算放大器的反相输入端,因此,R3中的电流一定相同。因此

2.5 V = (3.32 mA) R3 或 R3 = 750 Ω.

利用以上等式,可计算出R1的值为499 Ω。

需要对信号进行箝位处理,使输出在任一方向上偏移ADC最大输入信号范围的值不超过100mV。因此,在输出端,高电平箝位应发生于+0.1V,低电平箝位应发生于–2.1V。

由于箝位发生在输入级,因此,输出端的箝位电平不但受电路增益的影响,同时也受失调的影响。因此,为了取得目标箝位电平,VH必须在+550mV时偏置,VL则须在–550mV时偏置。电源与地之间两个电阻806Ω和100Ω形成的分压器用于产生箝位电压。

一般地,输出端的箝位电平可用以下等式计算:

VCH = VOFF + G × VH

VCL = VOFF + G × VL

其中,VOFF为输出端的失调电压。

另外,设置箝位电平需要注意,箝位信号(VH和VL)是交替同相输入,在常规同相输入超出它们形成的“窗口”时选用。请参看图7。可以使箝位电压比输入信号的最大偏移高出和低出100mV,增益为2。因而,VH应比最大输入信号偏移+0.5 V高50 mV,即+550 mV。类似地,VL应比最小输入信号偏移-0.5 V低50mV,即-550 mV。两种情况下,多出的50 mV将乘以2,结果为100 mV,而相同的失调将同时应用于输入信号和箝位信号。

1N5712肖特基二极管用于保护AD9002中的基底二极管在加电瞬变期间不发生正向偏置。

其它的考虑一般地,用于产生VH和VL电压的电阻应保持在低于1k的水平,这样可以减少偏置电流导致的误差。另外,建议在接近运算放大器之处用0.1µF电容接地,以旁路VH和VL

。如果未使用两个箝位输入之一或者两者都未使用,则可将相应的引脚置于悬空,放大器的作用将与无箝位放大器相同。如果两个箝位引脚之一或两者同时动态驱动,则可以形成一种非箝位情形。此时,VH可针对正偏移无箝位在+V处偏置,VL可针对负偏移无箝位在–V处偏置。

结束语

输入箝位放大器(ICA)比输出箝位放大器(OCA)具有更好的箝位性能。对于多数应用,可用ICA取代OCA,但根据各种电路的细节,必须进行必要的修改,以成功完成更替。要成功应用ICA,必须根据具体情况处理各种电路。本文提到的技术描述了多数常见情况下需要的电路变更。

(来源:)

-

模拟信号

+关注

关注

8文章

1142浏览量

52560 -

箝位放大器

+关注

关注

0文章

4浏览量

6564 -

ADC驱动器

+关注

关注

0文章

35浏览量

13964

发布评论请先 登录

相关推荐

如何利用多种箝位放大器对输出端的信号偏移进行限制控制

如何利用多种箝位放大器对输出端的信号偏移进行限制控制

评论