MPC57xx 系列微控制器是 NXP 推出的一款采用 Power Architecture 技术构建,面向汽车和工业动力总成、发动机管理、电机控制、车身控制、网关、底盘和安全、仪表板和显示屏管理应用。

其特点如下:

MPC57xx 低端到高端产品的软件和硬件均兼容。采用高密度浮栅技术实现的嵌入式闪存。从单核到多核产品,运行频率从 32 MHz 到 300 MHz 以上,性能具有很高的扩展性。根据SafeAssure 功能安全保障计划设计,使系统制造商轻松达到功能安全标准,如 ISO 26262 ASIL-D 级安全完整性的要求。多种片上冗余和安全选项,例如延迟锁步内核、DMA 控制器、存储器保护单元、故障采集和控制单元,以及端到端 ECC。无以伦比的能效 – 并行处理加上一组精密的外设,以及Power Architecture 工具和软件生态合作体系的支持。

本期博文接之前的 MPC5744P 原理图设计指南,给大家介绍下 MPC5744P 在 PCB(Layout)上的一些注意事项,并结合我司自行设计的域控制器 - Lion 实例来讲解。

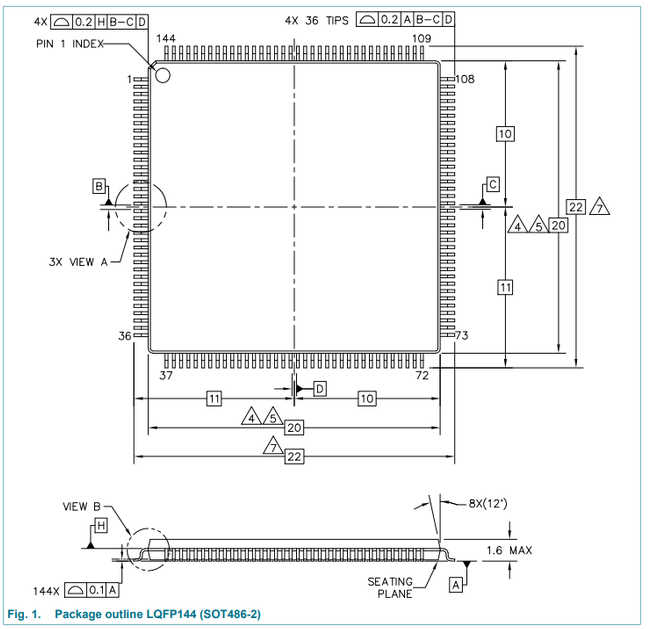

1. 封装介绍1.1 封装信息MPC5744P 封装包括两种:144 引脚 LQFP 封装、257 引脚 PBGA 封装。

两种封装在资源以及接口上的区别对比如下图所示:

1.2 封装尺寸

LQFP144 封装信息:

https://www.nxp.com/docs/en/package-information/SOT486-2.pdf

PBGA257 封装信息:

https://www.nxp.com/docs/en/package-information/SOT1547-1.pdf

2. PCB 设计建议

本设计指南 Layout 部分的示意图引用了我司自行设计的“ADAS 域控制器 - Lion”,设计选用了 MPC5744P – 257 MAPBGA 封装。大家如果对此方案的设计有想深入了解的,也可以转至我们大大通的微博专区搜索关键字:【ADAS 域控制器硬件设计】,或者方案专区搜索方案:“域控制器”关键字即可找到对应资源。

2.1 PCB 叠层结构

2.1.1 层的定义设计原则

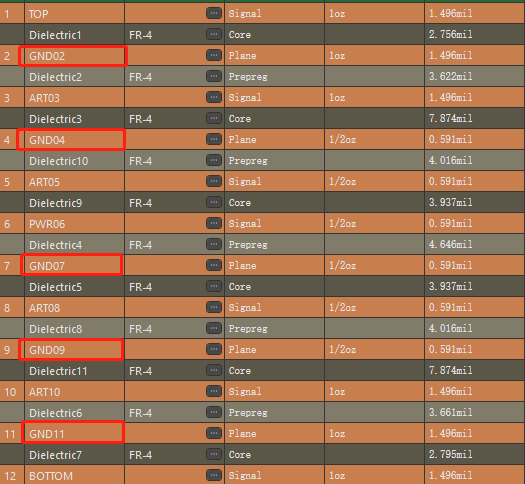

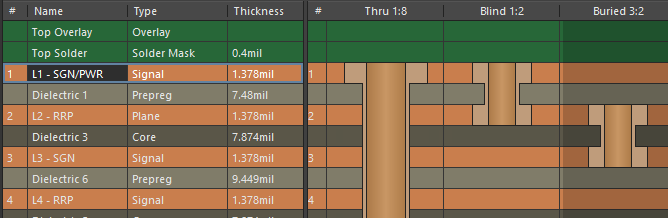

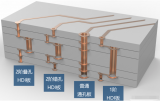

器件面下层(第二层)为地平面,为器件面布线提供参考平面;所有信号层尽可能与地平面相邻;主电源层尽可能与对应地层相邻;建议采用对称结构设计。针对于 MPC5744P 两种封装,推荐采用 4 层板设计,以保证参考平面的完整性(BGA 257 封装必须 4 层板,其中还有部分高速信号需要完整的参考平面例如 Zipwire)

下面的 PCB 设计参考建议基于 PBGA257 封装,并采用 6 层板的叠层结构设计。

2.1.2 地和电源层设计注意事项

注意电源与地层的完整性,避免出现导通孔密集区域,破坏平面层的完整性;

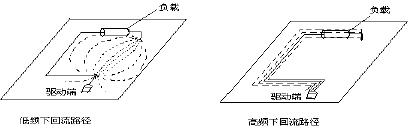

平面分隔要考虑高速信号回流路径的完整性;

高速信号、时钟等关键信号要有一个相邻地平面;

如高速信号在邻层的回流路径被分割,应在其它布线层做补偿;

20H 规则:为防止电源层向外辐射电磁干扰,应内缩 20H(电源层与地之间的介质厚度)。

2.2 高速信号走线建2.2.1 晶振走线指导

晶体尽量靠近主控放置,晶体的负载电容靠近管脚放置;晶体走线尽量短且走在表层,避免打孔换层;晶体电路建议包地处理,以隔离噪声;晶体走线的邻层保持完整地平面作参考,避免被任何走线分割

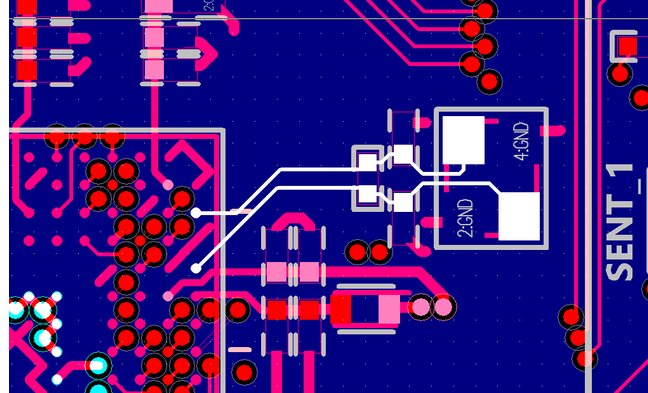

下图为 Crystal 部分信号走线 Layout 示意图:

2.2.2 Ethernet 走线指导① PHY 尽量靠近主控,EMI 效果越好,控制在 15cm 以内;② 下述信号如有串联匹配电阻,请靠近 PHY 放置,以改善 EMI

RXD[0:3],RX_CLK,RX_DV 走线尽量短并做等长处理,走线长度误差小于 100mil;

RX_CLK 包地处理;

③ 下述信号如有串联匹配电阻,请靠近 MPC5744P 放置,以改善 EMI

TXD[0:3],TX_CLK,TX_EN 走线尽量短并做等长处理,走线长度误差小于 100mil;

TX_CLK 包地处理;

④ MDI (Media-Dependent Interface) 线对间做等长处理,误差小于 10mil,总长度小于 12cm;⑤ 确保 PHY 的所有高速信号线有完整的参考面,与其它信号间距满足 3W 布线原则;

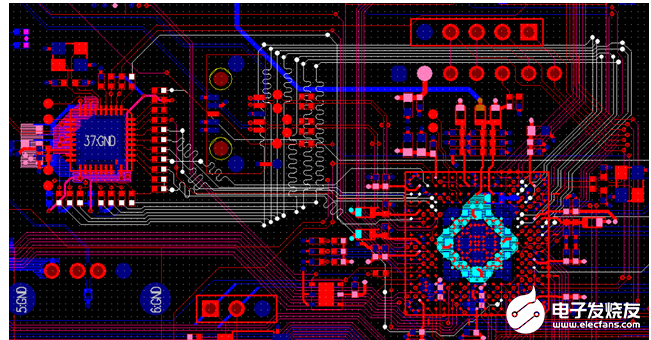

下图为 MII 部分信号走线 Layout 示意图:

2.2.3 Zipwire 走线指导

信号走线按差分规则处理,保证有连续完整的参考面,差分阻抗控制在 100ohm±10ohm;差分走线尽量短并注意等长处理,线对间误差小于 10mil;

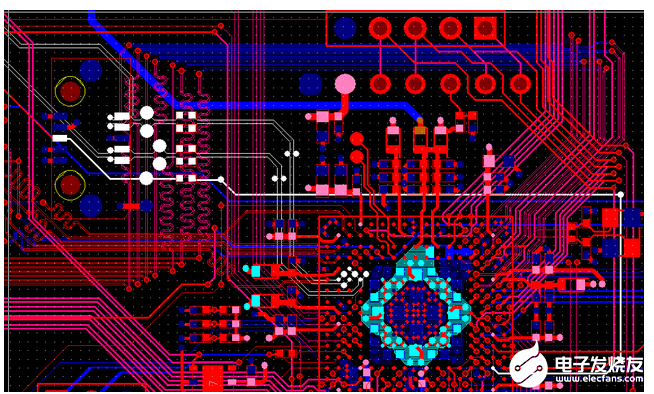

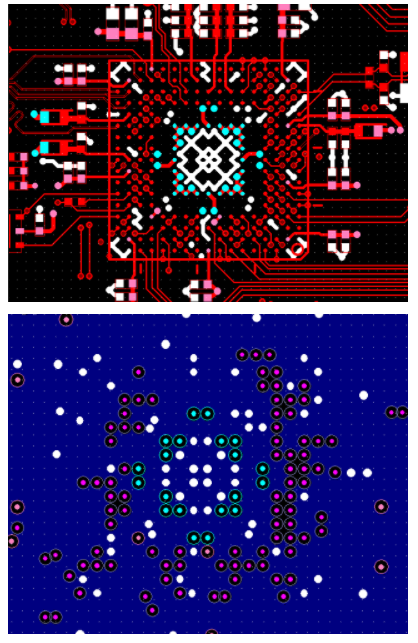

下图为 Zipwire 部分信号走线 Layout 示意图:

2.3 电源设计建议2.3.1 GND 设计

PCB 上必须有一层完整的 GND 层,用于散热和保证信号完整性;

保证芯片每一个 GND PAD 有对应的过孔,连接到主地上。

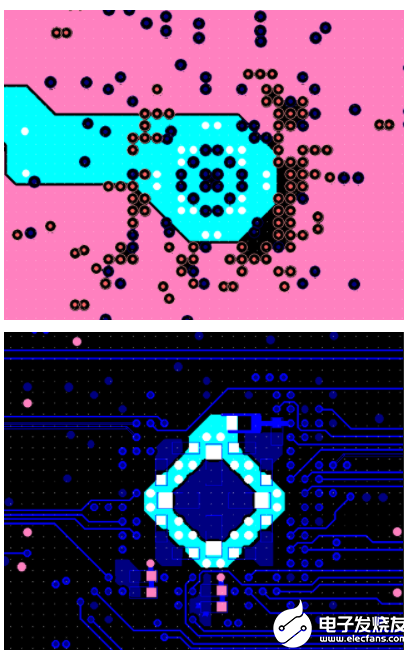

下图为 GND 部分信号走线(铺铜/L2) Layout 示意图:

2.3.2 电源设计

电源网络采用铺铜处理;

采用多层网络供电;

每个 VDD_LV_CORE PAD 有对应的一个过孔连到电源平面。

下图为 VDD_LV_CORE 部分信号走线(铺铜/L3) Layout 示意图:

3. 参考文档

① MPC5744P Datasheet:《MPC5744P microcontrollers - Data Sheet (REV 6.1)》② 大大通方案《基于 NXP S32V234+NXP MPC5744P ADAS 域控制器解决方案》:https://www.wpgdadatong.com/cn/solution/detail?PID=524

-

Layout

+关注

关注

15文章

424浏览量

75447 -

adas

+关注

关注

311文章

2346浏览量

212164 -

高速信号

+关注

关注

1文章

278浏览量

18529

发布评论请先 登录

PCB设计中的叠层原则

PCB设计建议 PCB叠层结构

PCB设计建议 PCB叠层结构

评论