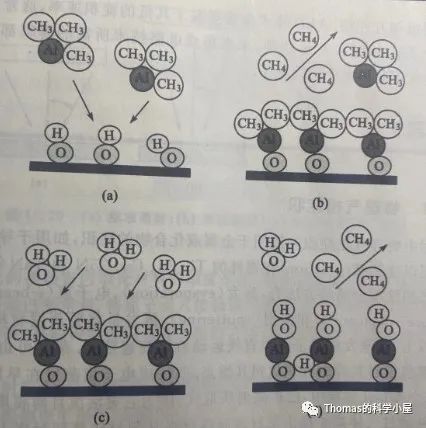

原子层沉积技术(Atomic layer deposition, ALD)近年在集成电路制程设备产业中受到相当大的瞩目,对比于其他在线镀膜系统,原子层沉积技术具有更优越的特点,如绝佳的镀膜批覆性以及精准的镀膜厚度控制。随着逻辑制程演进,原本二维的晶体管架构已经被三维的鳍鱼式晶体管(FinFET)取代,关键尺寸(Critical dimension, CD)也由深次微米进入到目前只有单一数字的纳米大小,对于镀膜的批覆性与厚度控制都有最严苛的要求,这让原子层沉积技术成为先进鳍鱼式晶体管与将来环绕式栅极(Gate-all-around, GAA,或其他类似结构)晶体管制程最重要的镀膜技术。

原子层沉积技术除了上述在集成电路制程上的应用外,还有一个尚未没被报导过的应用: 可以将原子层沉积技术应用在材料分析上,例如穿透式电子显微镜(Transmission electron microscope, TEM),用来制备一层在欲分析试片上的保护层。我们都知道,目前制备TEM试片(lamella)最常用的工具是聚焦离子束(Focused ion beam, FIB),FIB制备过程中,为了保护欲分析位置,一般的作法是在试片表面制备一层保护层,保护层常用的材料为碳系的胶类或是金属,其保护层厚度大约介于数十纳米到500纳米之间,主要可以利用旋转涂覆或是真空镀膜系统制备。既然是用来保护欲分析的试片,所以在制备保护层过程中是不能改变试片结构,造成事后材料分析上的困扰,依据不同的制备机制(尤其是真空镀膜),有两项主要会影响欲分析试片结构的因素需要被严肃看待,分别是温度与离子轰击效应。对于较旧制程的试片(大于28纳米),试片结构与材料都相当稳定与坚固,根据我们多年的经验,一般制备条件都不会改变或损伤欲分析试片的结构。

当分析的结构为先进制程的试片时(16纳米以下),情况则变得相当复杂,不但关键尺寸持续的微缩外,制程过程中也引进了不少新材料, 例如,已经开始应用在7纳米与未来环绕式栅极制程的深紫外光光阻(Extreme ultraviolet photoresist, EUV-PR)。根据国际期刊报导,深紫外光光阻相当脆弱,而且对于温度与离子轰击相当地敏感,如果使用运用在旧制程试片上的传统方式制备保护层,欲分析试片的结构很有可能因温度或离子轰击而损伤或变形,造成分析上的困难。另外,利用传统制备方式对于较小关键尺寸的结构,如贯孔(via)或沟(trench),保护层的批覆性也会是个难题,小尺寸结构开口处容易造成保护层材料堆积而缩口,产生孔洞或气泡,这些人为的结构都有可能会在FIB制备时产生不必要的刀痕,甚至在判读TEM影像上造成困难。

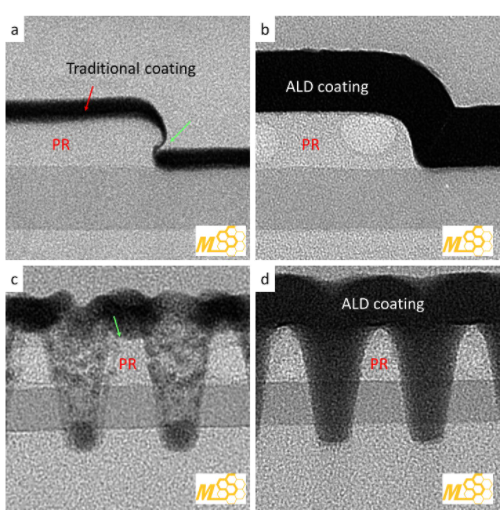

图 1. 两种光阻结构分别利用两种制备保护层方式的TEM照片。a与b为一组,c与d为另一组,其中a与c是使用传统镀膜方式制备保护层,b与d则是使用低温真空原子层沉积技术制备。绿色箭号标示处为光阻变形最明显的区域。

为了解决上述这些问题,泛铨科技跳脱旧有窠臼,提出一个革命性的想法,利用低温真空原子层沉积技术取代传统镀膜,制备欲分析试片的保护层。原子层沉积技术有绝佳的镀膜批覆性,即使是贯孔、沟、或甚至小关键尺寸的结构都能轻易制备保护层,不会形成人为孔洞,为了避免FIB制备时造成的刀痕与TEM观察时高能量电子束的轰击损伤,保护层都会制备厚于50纳米,这层保护层就像让欲分析的脆弱结构穿上无坚不摧的铠甲,有效抵御高能量离子束造成的损伤。针对试片表面的特性与分析目的,我们可以选用不同的保护层材料,但最重要的是,不管选用哪种材料,制备温度都只比室温高一些,远远比传统制备方式低很多,此低温制备对于最脆弱的深紫外光光阻尤其重要。有了上述这些利用低温真空原子层沉积技术保护试片的做法,我们才能获得精准的材料分析结果。

图1a与1c分别是利用传统镀膜方式制备保护层在两种光阻结构上的TEM照片,图1b与1d为与1a与1c试片有相同结构与材料但不同试片的对照组,,保护层制备是采用泛铨所提出的低温真空原子层沉积技术概念。由这些图可以清楚比较出,传统镀膜制备方式确实对光阻造成程度不一的损伤,尤其在绿色箭号标示处,光阻变形的相当严重。反观使用低温真空原子层沉积技术制备的试片(图1b & 1d),光阻结构并没有明显的变形。

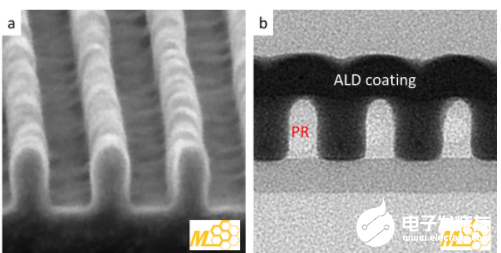

为了确认低温真空原子层沉积技术制备保护层确实不会造成光阻材料变形与损伤,我们利用高分辨率的扫描电子显微镜(Scanning tunneling microscope, SEM)来观察在没有任何制备下最原始的光阻试片状况(图2a),其对应相同结构与材料的TEM结果则呈现在图2b中,比较这两图,可以清楚地看到SEM影像中所观察到的结构细节也都有出现在TEM影像中,这证明泛铨科技所提出使用低温真空原子层沉积技术制备保护层的概念确实不会对脆弱材料造成损伤。

图 2. a 高分辨率SEM照片,该光阻试片没有经过任何镀膜处理,为原始表面照片。相同的试片再经过低温真空原子层沉积技术制备保护层后的TEM照片则呈现在b。比较两图可以清楚看到光阻结构并没有

低温真空原子层沉积技术概念不但可以应用在分析脆弱材料的保护层制备上,也可以将其应用扩展到故障分析与表面分析上,尤其如果试片的保护层需要在最严苛条件制备时,低温真空原子层沉积技术都能派上用场。泛铨科技所提出的这项革命性的概念也在2020年获得专利,相信将来会有越来越多的材料会需要用到该技术。

编辑:hfy

-

集成电路

+关注

关注

5388文章

11563浏览量

362083 -

电子显微镜

+关注

关注

1文章

96浏览量

9860

发布评论请先 登录

相关推荐

集成电路制程设备领域原子层沉积技术解析

集成电路制程设备领域原子层沉积技术解析

评论