2020年6月15日至18日(美国时间,第二天为日本时间)举行了“ 2020年技术与电路专题讨论会(VLSI 2020年专题讨论会)”,但实际上所有的讲座录了视频,并可付费观看至2020年8月底。

如果像过去那样在酒店场所召开会议,则您只能参加众多平行会议中的一个会议。但是以视频点播形式,您可以根据需要观看所用会议。这样做需要花很长时间,因此应许多与会者的要求,付费会议注册者的视频观看时间已经延长了大约两个月,直到8月底。

在这个VLSI研讨会中,共有86个工艺研讨会,110个电路研讨会,总共约200篇论文。本次技术研讨会上,与内存相关的会议是最多的,并且针对每种存储器类型(例如NAND / NOR / PCM,RRAM,RRAM,FeRAM,STT MRAM和下一代MRAM)均举行了会议,覆盖先进器件/工艺,先进Si CMOS,先进工艺,Ge/SiGe器件,用于量子计算的器件以及新器件领域。除此之外,与3D堆叠封装相关的还有3个会议。

接下来,我想在这大约200个演讲中,挑选并介绍一些受到高度赞扬的论文和演讲。首先,我要介绍是比利时IMEC的BPR工艺,其次是法国Leti和IBM关于先进CMOS技术领域的演讲。

IMEC针对5nm及以下尖端工艺的BPR技术

比利时独立研究机构imec的研究人员报告了在FinFET工艺中添加埋入式电源线(BPR)的实验成果。该项技术被定位为5纳米及以下制程的重要技术。他们采用钨作为该电源线的材料,并且已经证实该技术对晶体管性能没有影响。

此外,通过将钌(Ru)用于连接到埋入钨的布线的通孔,还证实了其在4 MA /cm2和330℃的条件下承受320小时以上的电迁移应力,以此说明钌是该技术最优选的候选材料。

图1,IMEC现场演示文稿截图

图2,BRP的TEM图,其中鳍节距为45 nm,鳍与BPR之间的最小距离约为6 nm

Leti宣布推出7层纳米片GAA晶体管

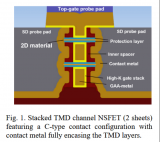

环绕栅(GAA)纳米片晶体管的有效沟道宽度大,因此其性能优于FinFET。法国国家电子技术研究所(CEA-LETI-MINATEC)的研究人员讨论了在增加每个有效通道宽度以改善器件性能和制造工艺复杂性之间进行权衡的问题。

他们首次制作了具有RMG工艺金属栅极,Inner spacer和自对准接触的七层GAA纳米片晶体管原型。所制造的晶体管具有出色的沟道电控制能力和极高的电流驱动能力,其饱和电流是两层堆叠纳米片GAA晶体管的三倍(在VDD = 1V时为3mA /μm)。

图3,7层纳米片GAA晶体管的TEM图

IBM报告了先进CMOS的Air Gap 栅极侧墙技术

业界早已认识到,将Air Gap用作晶体管的栅极侧墙上的绝缘膜间隔物的一部分,是减少寄生电容的有效方法。

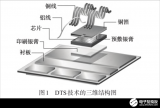

IBM研究人员报告了一种改进的Air gap 侧墙技术,该技术兼容具有自对准触点(SAC)技术和COAG技术的FinFET晶体管。在新的集成方法中,Air Gap是在形成MOL接触(SAC和COAG)之后形成的,并且无论晶体管结构如何,都可以形成Air Gap,这使得该技术应用空间非常广阔。

在假定该技术降低了15%的有效电容(Ceff)的情况下,演算得出采用该技术的7nm工艺在功率和性能上将优于5nm工艺。

图4,(a)是3D概念图,(b)SAC和COAG之后形成的具有Air gap 的FinFET TEM图。

图5,后Air Gap Spacer 工艺流程图,由编者摘自对应演示文稿

-

CMOS

+关注

关注

58文章

5750浏览量

236294 -

工艺

+关注

关注

4文章

615浏览量

28939

发布评论请先 登录

相关推荐

能源管理平台排名一览,哪家好用

IEDM 2024先进工艺探讨(三):2D材料技术的进展及所遇挑战

工业智能网关排名一览

评测 览邦(Lanbang) LairPods Pro+ 多模式真无线降噪耳机

请问DAC7731的数字部分是bipolar工艺还是cmos工艺?

LOTO示波器软件新增导览功能

什么是BCD工艺?BCD工艺与CMOS工艺对比

CMOS工艺技术的概念、发展历程、优点以及应用场景介绍

SiC功率器件先进互连工艺研究

2020 VLSI——先进CMOS工艺一览

2020 VLSI——先进CMOS工艺一览

评论