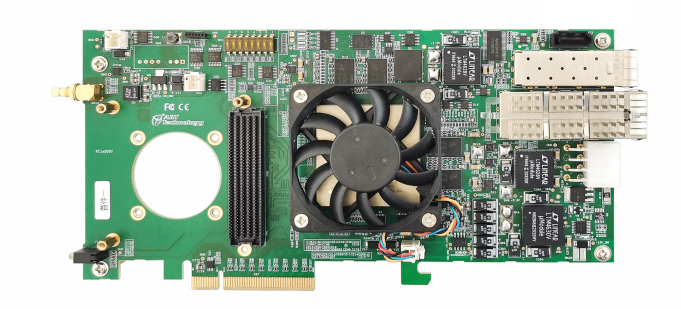

本文接续上一篇《FPGA杂记基础篇》,继续为大家分享IP例化和几个基于FPGA芯片实现的Demo工程。

IP例化

IP即是一个封装好的模块,集成在相应的开发环境里面,以安路的TD软件为例,不同系列的芯片集成了不同的IP模块,可以通过软件例化调用。

以下是安路TD4.6.5集成的EF3L40CG332B的相关IP。

1.1 PLL&RAM

以例化PLL和RAM为例,实现两个异步双口 RAM。

读写时钟都设置 100Mhz, 两个 RAM 为 RAMA 和RAMB, 深度为 1024,位宽为 8bit,写入数据为 8bit,100Mhz 持续数据流, 当 RAMA被写入 1024 字节数据后切换到写 RAMB, RAMB 被写入 1024 字节后切换 RAMA。以此循环类推。

当 RAMA 被写入 1024 字节时, 给读时序提供一个启动信号读取 RAMA 的数据, 读取完 RAMA 的 1024 字节数据时, 切换读 RAMB 以此类推。

这个工程的工程结构如下图:

首先EF3L40CG332B_DEV开发板提供了25Mhz的晶振时钟输入到EF3L40CG332B的时钟管脚。

想要得到100Mhz的读写速率,需要先用PLL得到倍频时钟。

在tools目录下点击IP Generator进入IP core页面,并选择PLL,输入时钟填入板子晶振25Mhz。

输出时钟填入所需要的100Mhz,并从C0输出。

设置完成后,生成的module声明如下(完整模块可参考代码)

再生成ram的IP模块。

在IP core中选择RAM。

-

FPGA

+关注

关注

1629文章

21736浏览量

603201 -

芯片

+关注

关注

455文章

50785浏览量

423457 -

电力电子

+关注

关注

29文章

564浏览量

48881

发布评论请先 登录

相关推荐

详解FPGA的基本结构

什么~FPGA可以自行二次开发了?

全新电池管理系统BMS (3串计量芯片) Demo

FPGA设计经验之图像处理

Xilinx FPGA编程技巧之常用时序约束详解

AMD FPGA中MicroBlaze的固化流程详解

Xilinx FPGA编程技巧之常用时序约束详解

FPGA杂记之基础篇二及Demo案例详解

FPGA杂记之基础篇二及Demo案例详解

评论