作者:邢万,俞珍传,贺磊,陆锋

1 引言

随着IC设计方法与工艺技术的不断进步,集成电路结构和功能日益复杂,测试问题成为必 须考虑的关键问题,测试成本作为整个IC产品成本的主要组成部分,也受到了极大的重视。由 于国内自动测试设备(Automatic testing EquIPMent)主要依赖进口,价格昂贵,测试图形产生, 特别是测试量产过程的花费(例如测试时间),就显得尤为重要。为了使测试成本保持在合理 的限度内,最有效的方法就是采用可测性设计(Design For Testibility)。可测性设计(DFT) 是适应集成电路的发展要求所出现的一种技术,主要任务是通过适当的设计重构或调整来提高电路整体性能的辅助设计方法,其核心是通过适当的前期代价来提高电路的可测性,即可控制 性和可观察性,降低产品的测试成本。本文设计的RISC_CPU是一个复杂的数字逻辑电路,采用DFT策略可以很好地解决测试问题。

2 CPU 结构

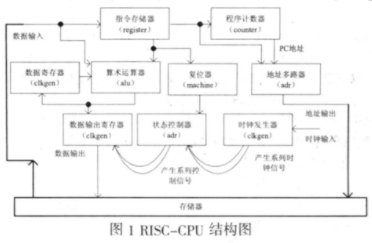

本文设计的RISC_CPU,主要分为几个模块,各个模块之间的互连关系如图1所示。

1. 时钟发生器(clkgen):产生一系列的时钟信号送往 CPU 其他部件;

2. 指令寄存器(register):存储指令;

3. 累加器(accum):存放算术逻辑运算单元当前的结果,它也是算术逻辑运算单元双目运算中的一个数据来源;

4. 算术逻辑运算单元(alu):根据输入的不同操作码分别实现相应的加、与、读、写、异或,跳转等指令;

5. 数据输出控制器(datactl):控制累加器的数据输出;

6. 状态控制器(control):CPU 的控制核心,用于产生一系列的控制信号,启动或停止某些部件;

7. 程序计数器(counter):提供指令地址,以便读取指令;

8. 地址多路器(adr):选择输出的地址是 PC(程序计数)地址还是跳转的目标地址;

9. 状态复位器(machine),状态控制器复位信号生成模块。

3 基本概念释义

3.1 扫描

扫描设计方法是通过将电路中的时序元件替换为相应的可扫描的时序元件(即扫描单元), 然后将它们串联起来,形成一个从测试输入到测试输出的串行移位寄存器。这样,测试数据由 测试输入,通过移位,到达要控制的单元;内部数据,再次通过移位,由测试输出的端口,观 察结果。

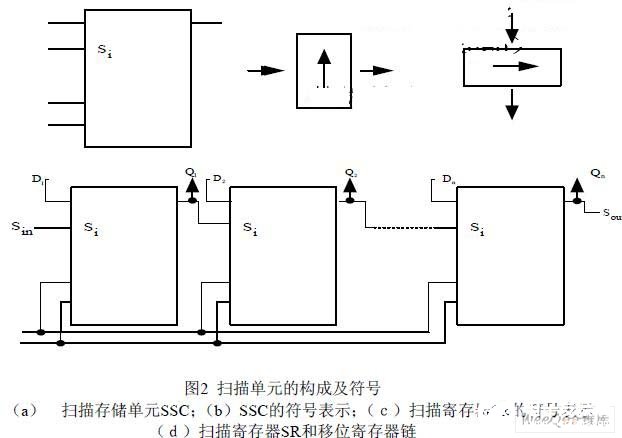

3.2 基于沿触发的扫描单元结构

图2是扫描单元构成,其工作原理是:在扫描模式控制下实现数据的扫描输出,即T/N =1 时,扫描数据从i s 输入,在时钟作用下从Q输出,输出的是扫描输入的数据。而当T/N = 0时, 扫描单元处于正常工作模式,也就是在时钟作用下从Q输出,但输出的是单元正常工作的数据。

4 扫描设计

4.1 自动扫描单元替换

RISC_CPU有近万个时序单元,为了获得较高的故障覆盖率,采用了全扫描的设计方案, 使用Synopsys公司Design Compiler自动完成测试插入功能,用最基本的扫描触发器来替换时序 单元,共设计了9条扫描连, 测试激励使用Synopsys公司的TetraMAX测试产生工具产生出来:共 产生组合测试向量1413个,其故障覆盖率达到95.06%;产生时序测试向量147个,覆盖率增加到 97.39%。在剩余2.61%未覆盖的故障中,1.4%的故障是电路设计中的冗余故障。

4.2 扫描移位测试

测试使能端test_se=1,将电路置为扫描模式,每条扫描链上的所有触发器数为n,从scan_in送 入一个长为n+4的输入序列:00110011…0011。这个序列将在每个扫描触发器中产生所有可能的 4种跳变信号情况:0→0,0→1,1→1,1→。从scan_out可以观测到信号跳变情况。这个测试覆 盖了触发器中大多数单故障型故障,从而确保扫描链的移位操作不出错。由于9条扫描链可以并 发测试,以最长扫描链的长度为准,完成移位测试的测试时间约为582=(289*2+4)个测试时钟 周期。

4.3 固定型故障的测试

单固定型故障是芯片测试的主要目标。由于我们采用全扫描设计,因此对大部分电路可以 使用组合电路的测试方式完成,即测试输入数据通过扫描链准备好后,只经过一个节拍就进行 输出响应的捕获。但是,由于RAM的存在,读写RAM的信号不可观测和控制,因此对于最靠近 RAM的一级触发器到RAM之间的组合逻辑,称为RAM的阴影逻辑(shadow logic),无法通过组 合电路的测试方式完成。解决这个问题一般有两种方式,一种方式是在RAM外部插入测试点来 提高阴影逻辑的可控制性和可观测性, 由于这会影响访存RAM的性能,这种方案在该 RISC_CPU中不可取。另一种方式被采用,即对RAM建立等价功能模型,这将导致需要用测试 时序电路的方式来测试阴影逻辑。

为了保证测试时钟的可控性,在芯片测试时需要将测试控制信号test 置为有效(test=1),使 芯片工作在测试方式。对一个芯片的测试过程如下:在扫描模式下,测试激励通过一条或几条 扫描的scan_in管脚,串行移位到响应的扫描触发器。当一个测试的所有输入激励准备好后,使 用系统时钟将测试激励送入被测逻辑。一个时钟周期(对组合测试)或几个时钟周期(对时序 测试)后从被测模块的输出端口所在的扫描链上,将输出信号依次串行移位到相应的scan_out 引 脚,将读出的数据与期待的输出比较,以判断被测逻辑中是否存在故障。

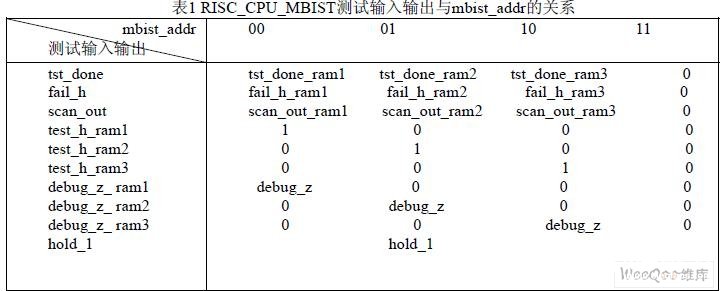

5 存储器测试

本文采用了Mentor 公司的MBIST 插入工具MBISTArchitect。MBISTArchitect 可以创建和 连接RTL 级BIST 逻辑到待测芯片中。RISC_CPU 的存储器由RAM1、RAM2、RAM3 三块大 小分别为20*128 字节、64*128 字节、64*48 字节的存储器构成面积约为45%,我们用三块带有 比较结构的MBIST 电路,这三块MBIST 是通过mbist_addr 和MBIST 模块来控制的,三块MBIST 电路共享测试控制信号hold_1 和诊断控制信号debug_z 以及三个测试输出tst_done、fail_h 和 scan_out(错误定位即诊断数据输出)。MBIST 测试使能信号由mbist_addr 解码得到,从而决定三块MBIST 电路的工作次序以及最终的芯片测试输出,他们之间的关系由表1 给出。

由表1可知:当mbist_addr为00时,ram1的MBIST电路的控制信号即为外部相应输入的控制 信号,其他两个ram模块的MBIST电路的控制信号输入置为0。异步复位置位有效,系统处于ram1 的测试状态,系统测试输出即为ram1的测试输出;当mbist_addr为01时,系统处于ram2的测试状 态,系统测试输出即为ram2的MBIST测试输出;当mbist_addr为10时,系统处于ram3的测试状 态,系统测试输出为ram3的MBIST测试输出。

为了得到每一块RAM的测试结果,我们将MBIST的测试结果通过第九条扫描链移出,在多 个分组测试中,测试时间最长的执行MBIST算法大约需要1044800个时钟周期,加上初始化和测 试完成后将测试结果扫描移出的时间,共需要的时钟周期数不超过10445900个,如果测试时钟 的频率为20MHZ,则测试时间约为0.52秒。借助于BIST,对嵌入式存储器的单固定型故障、开 路故障、地址译码故障均获得了100%的故障覆盖率,达到了预定的要求。

6 结束语

本文合理地选择了边界扫面和内建自测试方式,根据时钟域划分各个功能单元,修改设计, 消除了设计规则违反,选择了适当的综合流程,在对设计负面影响不大的情况下,仅增加了0.2% 的时序消耗和0.02%的面积消耗,取得了良好的可测性效果,达到了芯片逻辑的97.39%的单固 定型故障覆盖率,能够监测到RAM中100%的单固定型故障覆盖率,满足了芯片生产测试需求。

责任编辑:gt

-

控制器

+关注

关注

112文章

16400浏览量

178551 -

IC

+关注

关注

36文章

5965浏览量

175792 -

cpu

+关注

关注

68文章

10880浏览量

212209

发布评论请先 登录

相关推荐

DFT的优缺点比较 DFT在机器学习中的应用

DFT与离散时间傅里叶变换的关系 DFT在无线通信中的应用

DFT在图像处理中的作用 DFT在音频信号处理中的应用

DFT在信号处理中的应用 DFT与FFT的区别

SiFive 推出高性能 Risc-V CPU 开发板 HiFive Premier P550

Imagination CPU 系列研讨会 | RISC-V 平台的性能分析和调试

香蕉派 BPI-CanMV-K230D-Zero 采用嘉楠科技 K230D RISC-V芯片设计

晶心科技与Arteris携手加速RISC-V SoC的采用

RISC-V的MCU关于USB高速通信设计的难点

龙芯:自主研发CPU提升性能,单核通用性能提高20倍

Imagination 推出全新Catapult CPU,加速RISC-V 设备采用

采用DFT策略提高RISC_CPU的性能设计

采用DFT策略提高RISC_CPU的性能设计

评论