1 引言

几乎所有的信息系统(如电话、电视等)都在经历从模拟到数字的改变。数字硬件系统 有处理算法与硬件充分的独立;软件升级简单快速等优点。因此,数字接收机已经开始应用 于移动通信,民航空中管制系统,医学成像等方面。在教学中也开始接触到数字接收平台。

在无线通信系统和工业控制系统的教学试验平台设计中,提供接近真实的数据和接近真 实数据率的数据是检验算法的性能和效率所必须的。而与真实系统相连接是不必要和高成本 的。因此设计阶段提供一个近似的替代(数据模拟源)是最好方法。

本文针对数字接收机测试设计一个可靠而且通用的模拟测试数据源。该电路主要是为软 件产生的模拟数据提供一个到达数字接收处理机的通路,并提供一个pc机与处理机通信的平 台。该数据源采用了标准工业互联总线(PCI)和低压差分信号(LVDS)传输以保证系统的 高数据率。在软件设计上采用分层结构配合驱动程序提供了最大的系统灵活性。

2 系统结构与硬件设计

2.1 系统模型

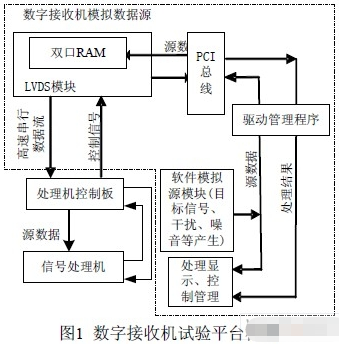

图1示出了数字接收机试验平台框图,主要是由处理机和模拟数据源模块组成。

1.软件模拟源及显示控制:根据模拟环境(数据率、信号干扰)产生模拟数据及回送结果的分析。

2.驱动程序:对(硬件端)它负责控制数据的发送接收,板卡ram在内存的映射,中断的管理等。

3.处理机:高速处理机由ADSP2116高速DSP组成,专注于高速数据流的算法。

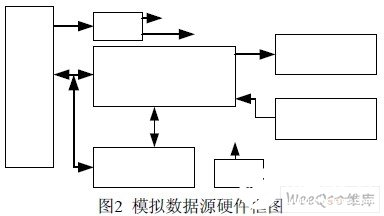

模拟数据源形态为标准PCI板卡,框图见图2。

模拟数据源包含pc机和处理机的高速通道和模拟射频前端数据流的应用程序。通用计算 机作为数据源产生和分析工具。这样提供了最大的灵活性。 数据模拟卡电路主要由7个部分组成:PCI桥负责本地总线和pc机pci总线的协议转换; 控制逻辑由FPGA和下载电缆组成,修改功能可以完成测试、接收、发生数据的控制逻辑。

双口RAM作为该板的数据缓存;LVDS串行器(SER)负责接收控制逻辑来的数据串行后送 到传输线上;LVDS接收解串器(DES)接收传输线上来的串行数据,解串后无误的送到控 制逻辑中由其处理(存储到RAM或转换状态);电源形成所需的电源电压;时钟电路为板卡 的逻辑器件提供稳定的本地时钟源。

2.2 PCI桥接电路

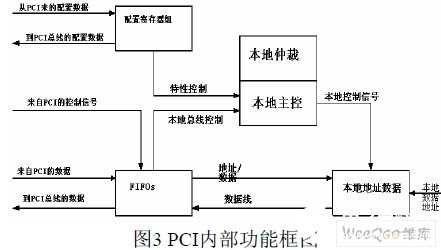

PCI是工业互联标准有32/64位宽度,33/66MHz频率,PCI总线电信号采用电波反射增强 原理,最高理论可达4224Mbps。支持突发传输。总线设备可高效配置,可保证设备并行处 理。设计中我们选用PLX tech公司的PCI9052芯片。内部功能见图3。

9052是一个协议转换电路,它将本地端的芯片连接到PCI总线,将pci指令(读写寄存器、 内存、io)翻译到本地端进行相应的操作。9052内部提供了两套配置寄存器:pci配置空间寄 存器和是本地配置寄存器,分别提供PCI和本地端的配置信息。硬件设计上对PCI端布线长 度有等长度限制外没有特别要求。

2.3 LVDS收发器电路

LVDS(Low Voltage Differential Signaling)是采用低摆幅差分信号(350mV)传输数据的技 术,可以达到百到千兆位每秒的速率。LVDS具有速度高、功耗低、辐射小、成本低、抑制 共模干扰强的优点。我们选用MAXIM生产的max9205/7(SER)串行器和max9206/8(DES)解串 器对实现LVDS。LVDS电平的传输没有特别要求,CAT3/CAT5能够达到10m的传输要求可以 满足我们的测试要求。因此我们采用RJ45插座,同时PCB背板注意了阻抗匹配及铝壳屏蔽抗 干扰的问题。

在SER/DES发送和接收数据前,必须对发送和接收链路进行初始化(把DES和SER的PLL 同步到各自的本地时钟)。当SER同步到本地时钟后,DES同步到串行器,最后完成初始化过 程。同步结束之后,SER和DES开始传输数据帧,由于每一帧含有开始比特1,10比特数据, 结束比特0,因此SER输出为12倍传输时钟。数据率非常高。

2.4 控制逻辑FPGA

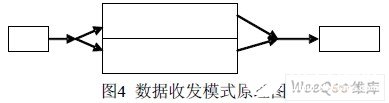

我们选用Altare的EPF6016设计控制逻辑。Altare的开发工具MaxplusII和器件非常优秀; 并且支持在线编程。为了保持设计的完善,我们将控制逻辑设定了两种工作模式,数据模式 (见图4)和测试模式。通过下载电缆修改逻辑设计就可以改变其工作模式。

数据模式中双口ram被分成0体和1体呈现乒乓结构,这样交叉使用可以在LVDS上形成高 速的数据流,以模拟大规模阵列或者通信天线的输出。测试摸索中LVDS收发器形成回路, 用于逻辑自检和板块测试。

2.5 存储和外围电路

我们采用双端口IDT7133/7134提供乒乓存储。一个端口与PCI9052无缝连接,作为PCI 直接操作的缓存。另一个端口与控制逻辑连接,供FPGA访问。PC机主板提供了5v电源,通 过LT1117-3.3直流转换器将5v转换成3.3v供LVDS。为了LVDS PLL能够有效锁定,因此使用 40M时钟模块通过FPGA编程分频后提供时钟。图5为模拟数据源板卡成品。

3 软件设计

模拟源软件包括驱动程序和应用程序设计。

本课题中,设备驱动程序的主要任务是在系统内存空间中守护一块内存,作为PCI板卡 上双口RAM的镜像,即完成双口RAM和内存的同步。当卡发送数据时,数据从内存中拷贝 到PCI板卡RAM中;接收数据时数据从PCI板卡RAM中拷贝到系统内存中。该功能通过在驱 动程序加载时调用内存分配函数完成。由于本设计中涉及到了系统中断,驱动程序还要在系 统中设置中断服务例程(ISR)。应用程序完成模拟数据产生,分析等算法相关的内容。应用 程序开发目的是提供一个于MatLab的良好连接,使其能够和MatLab环境协调工作,充分利 用MatLab的数学分析、计算能力(将另文论述)。

4 结论

本文针对数字接收机平台测试,实现了一种通用的测试数据源。该模拟数据测试源基于 PCI和LVDS。本文系统具有扩展性好,适应性广等优点。

本文创新点:针对数字接收机平台测试,基于PCI和LVDS设计了一种通用的测试数据源。 PCI和LVDS能适应高数据率,分层软件结构能够适应各种应用场景。对教学和工程实践都有 较好参考价值。

责任编辑:gt

-

控制系统

+关注

关注

41文章

6671浏览量

110969 -

接收机

+关注

关注

8文章

1186浏览量

53714 -

测试系统

+关注

关注

6文章

827浏览量

62284

发布评论请先 登录

相关推荐

差分信号在音频设备中的实现

测试接收机的技术原理和应用场景

探讨差分信号的优缺点

差分信号是什么意思?差分信号怎么产生?

DS90C402双通道低压差分信号(LVDS)接收器数据表

基于标准工业互联总线和低压差分信号实现数字接收机测试系统的设计

基于标准工业互联总线和低压差分信号实现数字接收机测试系统的设计

评论