新思科技(Synopsys)宣布推出业界首个支持Compute Express Link (CXL) 2.0的验证IP(VIP),以实现数据密集型片上系统(SoC)的性能突破。CXL是新一代开放标准的互联技术,可实现在CPU与加速器之间建立高速的互联生态系统(包括GPU、FPGA与特定加速器解决方案以及内存扩展设备之间的互联)。该技术基于成熟的PCI Express架构并使用了PCI Express 5.0的物理层和电气接口。

新思科技CXL验证IP基于新一代SystemVerilog的 Universal Verification Methodology(UVM)架构,使验证IP的集成变得简单,它在有效缩短第一个测试用例的调式时间的同时,可让用户们运行更多的测试用例。CXL验证IP包含了覆盖率分析和验证计划,可与Verdi的协议分析仪(Protocol Analyzer)和性能分析仪 (Performance Analyzer) 天然结合,在有效的提高debug效率的同时加速验证收敛。此外,经验证的DesignWare CXL IP可提供16 lane的连接,以实现高带宽和低延迟。DesignWare CXL IP可支持3种CXL协议(CXL.io、CXL.cache、CXL.mem)和设备类型,以满足不同的应用场景。

“新思科技内存一致性验证IP产品包括CXL 2.0、CXL 1.1和CCIX,可支持具有高数据吞吐量要求的新应用程序,我们将不断丰富行业领先的验证IP产品,并会持续与标准组织和闪存供应商紧密合作,让开发者可以快速采用和整合最新的连接技术。”——Vikas Gautam

“不断发展CXL作为开放标准的连接技术,来提升新一代数据中心的性能,是我们重大的努力方向,我们很感激新思科技对CXL联盟的支持以及对CXL 技术应用的推进。”——Jim Pappas

“将新一代重大的连接技术推向市场,来用于包括人工智能、内存扩展和云计算在内的数据密集型应用程序,需要一个成熟的生态系统。与新思科技这样的行业领导者合作推进CXL在行业的发展,可以满足我们客户对其片上系统性能和数据连接的要求。”——Debendra Das Sharma博士

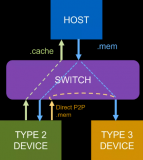

CXL 2.0协议在物理层和应用层都提升了扇出和池化系列特性。CXL 2.0支持的新性能包括:

●CXL Switch,支持多逻辑设备(MLD);

●支持CXL.io和CXL.CXL.cache/mem的IDE(安全性);

●可在APN阶段和热插拔期间协商CXL 2.0设备,支持CXL枚举,将CXL设备作为PCI Express的端点;

●通过QoS遥感技术对系统级可管理性进行更新,功能级复位、全局持续刷新、内存间插和一致性测试。

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

互联网

+关注

关注

54文章

11202浏览量

104352 -

人工智能

+关注

关注

1800文章

48083浏览量

242143 -

新思科技

+关注

关注

5文章

824浏览量

50550

原文标题:新思上新不断 - CXL 2.0验证IP,加速连接新一代互联技术

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

内存扩展CXL加速发展,繁荣AI存储

新思科技推出基于AMD芯片的新一代原型验证系统

澜起科技CXL®内存扩展控制器芯片通过CXL 2.0合规性测试

Cadence推出新一代验证系统

芯原发布新一代Vitality架构GPU IP系列

韩国无晶圆厂初创公司Panmnesia展示第一个支持CXL的AI集群

拓展AI数据中心内存,第二代AMD Versal Premium系列自适应SoC,首发支持CXL 3.1、 PCIe Gen6

研华科技推出SQRAM CXL 2.0 Type 3内存模块SQR-CX5N

思岚科技推出新一代圆形通用机器人底盘Apollo2.0

打造异构计算新标杆!国数集联发布首款CXL混合资源池参考设计

新思科技CXL 3.1验证解决方案

国数集联发布业界首款CXL多级网络交换机,IB时代的颠覆者

Wi-Fi 7射频IP验证系统发布!思尔芯EDA助力Sirius Wireless加速芯片设计

新思CXL2.0验证IP,加速连接新一代互联技术

新思CXL2.0验证IP,加速连接新一代互联技术

评论