EDA工具的出现,手动到自动的跨越

1958年诞生的芯片拉开了人类社会迈向信息社会的序幕,并逐渐形成了芯片产业。1965年,摩尔提出“由于工程师可以不断缩小晶体管的体积,芯片中的晶体管和电阻器的数量每年会翻番”,此后又修正为“每隔24个月,晶体管的数量将翻番”。彼时,芯片上的元件大约只有60种,设计人员依靠手工完成芯片的设计、布线等工作。 从20世纪60年代中期开始,业界先后出现包括通过几何软件生成单色曝光图像图形化工具,第一个自动化的电路布局和布线工具等,这些工具奏响了EDA发展的序曲。80年代开始,随着VHDL、Verilog、以及仿真器的出现,芯片设计仿真和可执行的设计有了其规范化的硬件描述语言和标准。

1986年新思科技创始人Aart de Geus博士发明了具有划时代意义的逻辑综合工具。逻辑综合工具的出现,使原本用单个门来手动设计芯片电路的工程师用电脑语言来“写”电路的功能,能够通过逻辑综合进行设计实现,极大提升了芯片设计的效率,从而让工程师将更多精力集中在创造性的设计上。这项发明无论当时还是现在,都具有划时代的意义,加速了芯片开发的进程,使大规模芯片开发变为可能,让人类有机会在今天设计出包含数百亿个晶体管的复杂芯片。

EDA工具推动芯片行业沿着摩尔预测的路径发展,从10µm逐步演进到如今的5nm,芯片规模逐渐扩大,电子系统变得越发复杂。从系统架构开始,落实到功能的定义和实现,最终实现整个芯片的版图设计与验证,是一项复杂的系统工程,汇聚了人类智慧的最高成果。以苹果2020年发布的新款A14芯片为例,这款芯片采用5nm工艺制造,将118亿颗晶体管集成在面积仅为88平方毫米的内核上,靠手工已经无法完成。

2

逻辑综合对于EDA设计领域来说是一个伟大的成就,能够把描述RTL级的HDL语言翻译成GTECH,然后再优化和映射成工艺相关的门级网表,作为输入给自动布局布线工具生成GDSII文件用于芯片制造。新思科技的Design Compiler自1986年推出以来,得到全球几乎所有的芯片供应商、IP供应商和库供应商的支持和应用,到90年代中期,Design Compiler已经成为RTL逻辑综合的事实标准,让设计人员的生产力提高至10倍。Design Compiler作为业界历史最悠久的设计实现工具,经过30年的不断发展和技术积累,提供最可靠设计实现优化和性能结果,是目前业界使用最为广泛的ASIC设计实现工具。

新思科技并未止步于一时的技术领先,而是前瞻性地预判到行业未来的发展趋势和市场需求,持续对Design Compiler系列产品进行研发投资,带来一次次突破性的创新综合技术。例如,新思科技将Design Compiler升级迭代为Design Compiler Graphical,加入物理综合,即在综合前加入版图的布局规划信息(floorplan),然后调用库信息和约束条件,生成带有布局信息的门级设计结果,进一步提高了综合与布局布线结果的相关一致性,不仅可以更精准地估算连线延时,还可以预测布线拥堵情况并进行相应优化。 Design Compiler系列产品已经引领市场超过30年,新思科技一次次以尖端的EDA技术,为当今极度复杂的前沿设计提供了有力支持。新版Design Compiler NXT集成了最新的综合创新技术,支持5nm以下工艺,能够大幅度缩短运行时间、实现具有绝对优势的QoR,同时满足了诸如人工智能(AI)、云计算、5G和自动驾驶等半导体市场对更小体积、更高性能、更低功耗的芯片需求,以及对研发周期越来越高的要求。

3

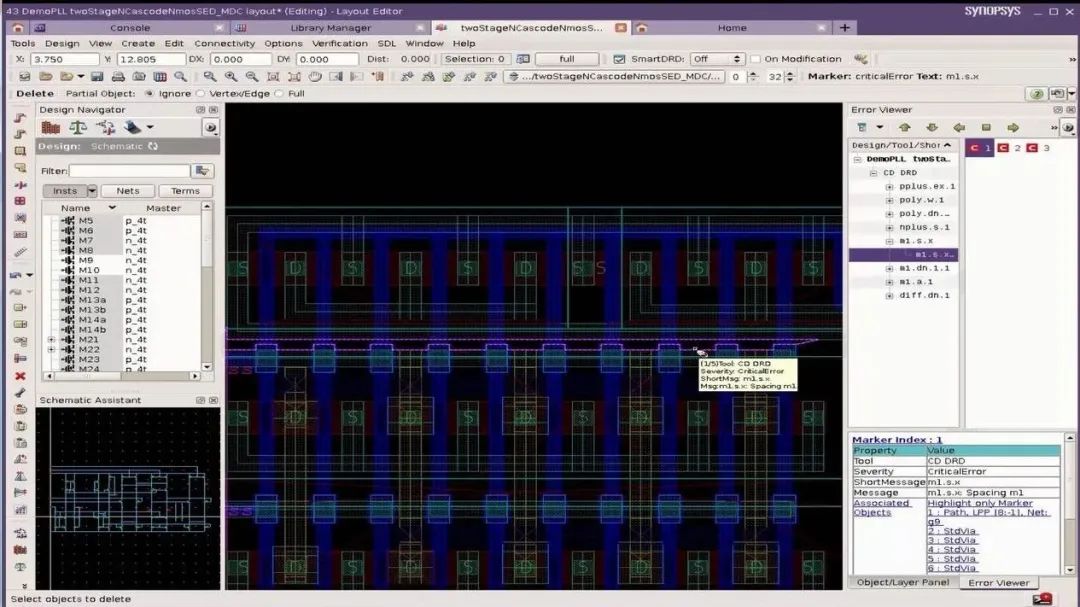

Fusion Compiler推动数字设计迈进新纪元

从2000年开始,由于复杂性日益增加,过程节点和设计时间持续缩减,使得在仍然能够提供更好的结果和更快交付的同时,管理设计成本变得十分关键。于是新思科技开始着手开发一个全面的、紧密集成的实现平台—— Galaxy Implementation Platform,能够将芯片物理实现所需的所有工具集成到一个协调的环境中,简化了工程师从一个工具变换到另一个工具的复杂度,有助于提高生产力并降低出错几率。IC Compiler是该平台的一个主要组件,为设计人员提供了一个单一、聚合、芯片级物理实现工具,该工具实现了卓越的设计结果质量(QoR)、交付时间更短、设计成本减少以及易用性等优点。 进入21世纪, EDA技术开始深入制造领域,并与晶圆厂建立紧密的合作,将EDA工具的使用从制造不断扩展到标准单元库、SRAM设计。而随着领先晶圆厂每两年开发一代工艺,不断推动摩尔定律向前,EDA工具需要在早期工艺研发中介入,以确保芯片的设计能够在新工艺上被精确应用、最终成功制造,EDA在产业链的作用更加凸显。新思科技作为目前全世界唯一一家覆盖了从硅的生产制造、芯片测试、到设计全流程的EDA公司,既能够在芯片制造的所有流程环节提供核心技术和软件,又能够为芯片设计的全流程提供核心技术软件的EDA和IP,有力推动了产业生态圈的良性合作。 工艺和设计的不断发展,要求前后端有更好的一致性,以便更快速的收敛。新思科技推出创新性的RTL-to-GDSII产品Fusion Compiler,通过把新型高容量综合技术、行业领先的布局布线技术、以及业界领先的golden signoff技术融合到统一可扩展的数据模型中,同时引入诸多机器学习技术,利用Fusion Compiler可以在最短的时间内提供同类最佳的设计实现质量,能够更好地预测QoR,以应对行业最先进设计对更高性能、更低功耗、可靠性、安全性的要求。

Fusion Compiler是业界唯一的从RTL到GDSII解决方案,能够实现前后端统一数据模型、统一的设计和优化引擎,让整个设计实现中保持良好的一致性,促进了设计实现性能提升,加快了工具实现的时间和设计收敛的速度。同时,引入机器学习技术,对设计的实现和优化进行加速,显著提高设计收敛的速度。这样的融合技术已被市场领先的半导体公司进行了充分验证,能够提供最高质量的设计,包括通过台积电5nm、3nm和三星5nm、3nm等最先进工艺的技术认证。

4

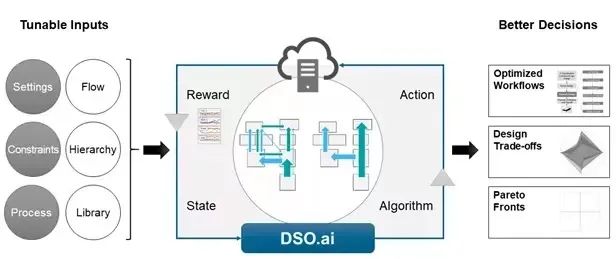

DSO.ai开启芯片智能设计

当前,芯片行业正在经历一个技术进步和创新浪潮的复兴时期。人工智能、5G、自动驾驶等新兴领域技术的不断发展对芯片设计带来全新的挑战,包括工艺要求提升、丰富的应用场景、整体设计规模以及成本等。EDA工具进入2.0时代,其未来的发展着重在两个大的方向,一是应用目前丰富的算力,提高并行和分布式处理能力,提升设计效率;二是更多的应用AI技术,促进设计的探索自动化,减少可替代的人工努力,解放工程师资源到更具创造性的工作。 新思科技于2020年初推出了业界首个用于芯片设计的智能化软件——DSO.ai(Design Space Optimization AI),这是电子设计技术上又一次突破性技术,能够在芯片设计的巨大求解空间里搜索优化目标。该解决方案大规模扩展了对芯片设计流程选项的探索,能够自主执行次要决策,帮助芯片设计团队以专家级水平进行操作,并大幅提高整体生产力,从而在芯片设计领域掀起新一轮革命。三星已经采用新思科技DSO.ai实现性能、功耗与面积优化上的进一步突破。原本需要多位设计专家耗时一个多月才可完成的设计,DSO.ai只要短短3天即可完成,提速近10倍。

在摩尔定律走向极限、电子领域急需转变突破的关键点、人工智能和量子等新兴技术及产业不断涌现的当下,新一代EDA(NG-EDA)的呼声越来越高。DSO.ai这种AI驱动的设计方法将引领EDA进入2.0时代——支持大规模并行运算、可部署在云端的EDA智能化设计系统。 EDA作为整个电子产业的根技术,从最初作为输入与仿真的工具确保芯片的正确设计、到通过优化与映射确保芯片设计的最佳性能、再到如今不断提升自主化和智能化来引领芯片设计,EDA通过自身的不断演进和迭代升级,将保障芯片的持续创新,为人类迈入数字经济时代提供源源不断的动力。

原文标题:从EDA技术演变看芯片创新之未来

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

454文章

50522浏览量

422424 -

IC

+关注

关注

36文章

5911浏览量

175341 -

eda

+关注

关注

71文章

2719浏览量

173025 -

新思科技

+关注

关注

5文章

791浏览量

50326

原文标题:从EDA技术演变看芯片创新之未来

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

从特斯拉看智能驾驶未来发展

兆易创新推出EtherCAT从站控制芯片

概伦电子荣获“中国芯”EDA技术创新奖

西门子EDA全面赋能芯片创新

从IC设计到系统创新,新思科技为AI创新提速

飞凌嵌入式技术创新日(深圳站)精彩回顾

思尔芯亮相CCF Chip 2024,展示创新EDA技术与产学研合作

AI+EDA加速双向赋能,引领万物智能时代的创新

芯片新战场,EDA如何拥抱新挑战?

从EDA技术演变里看芯片创新之未来

从EDA技术演变里看芯片创新之未来

评论