近几年,语音系统广泛应用于嵌入式数字音频产品,在MP3、手机等消费类电子产品中,人们对于这些个人终端的要求早已不限于单纯通话和简单的文字处理,高质量的音效是当前发展的重要趋势。随着嵌入式系统性能的提高,在ARM嵌入式系统中实现对各种音乐格式的解码和播放已有可能。在语音功能需求的驱动下,越来越多的厂商纷纷推出了具有各种功能和标准的语音处理接口协议。IIS(Integrate Interface of Sound)总线是Philips公司提出的串行数字音频总线协议。它是一种面向多媒体的音频总线,专用于音频设备之间的数据传输,为数字立体声提供序列的连接至标准编解码器。IIS总线处理声音数据。其他信号(如控制信号)必须单独传输。IIS总线一般具有4根信号线,包括串行数据输入(IISDI)、串行数据输出(IISD0)、左/右声道选择(IISLRCK)和串行数据时钟(IISCLK),产生IISL2RCK和IISCLK的是主设备。

整个音频系统的硬件部分主要是CPU和CODEC的连接与实现。Philips公司生产了一种支持IIS总线数据格式的音频编解码芯片UDA1341TS,采用位元流转换技术进行信号处理,完成声音信号的模数转换,具有可编程增益放大器和数字自动增益控制器,由于其功能强大、低功耗、低电压及具有DSP语音功能等特征,目前已广泛应用于各种嵌入式语音系统中。同时作者有关于触摸式语音菜单系统的实用新型专利授权正在审核当中。本文首先简单介绍了S3C2410X中的IIS总线接口,并在此基础上介绍了UDA1341TS语音芯片在触摸式语音电子菜单系统中的软硬件接口实现方法。

1 S3C2410X中的IIS总线接口

S3C2410X提供的IIS总线接口可以作为一个编码解码接口与外部8/16位的立体声音解频码IC相连从而实现一个微唱片和便携式应用。它支持IIS和MSBjustifled数据格式。IIS总线接口为FIFO队列的访问提供DMA传输模式来取代中断,它可以同时发送和接收数据,也可以只发送或接收数据。

1.1 IIS总线特征

(1)1通道基于DMA的IIS总线用于音频接口;

(2)每通道串行数据传输8/16位;

(3)128 B FIFO用于发送/接收;

(4)支持IIS格式和MSB验证数据格式。

1.2 数据传输模式

ARM芯片内置的IIS总线接口可以读取IIS总线上的数据,同时还可以为FIFO数据提供DMA传输,从而做到同时传输和接收数据。

S3C2410X的IIS接口有3种数据传输方式:

(1)正常传输模式:正常传输模式基于FIFO寄存器,该模式CPU通过轮询方式访问FIFO寄存器,通过IISCON寄存器的第7位控制FIFO。如果FIFO已满,IISCON的第7位被设置为“O”,表示不能继续传输数据;反之FIFO的第7位被设置为“1”,表示可以继续传输数据。

(2)DMA模式:这种模式是一种外部设备控制方式,通过设置IISFCON寄存器可以使IIS接口工作在该模式下。它使用窃取总线控制权的方式使外部设备和RAM交换数据,从而提高系统的吞吐能力。在S3C2410X芯片中有4个通道的DMA控制器用于控制各种外部设备,其中IIS与其他串行外设共用2个桥联DMA(BDMA)类型的通道。

(3)传输/接收模式:在这种模式下,IIS数据通过双通道DMA同时接收和发送音频数据。

1.3 信号线

信号线共5根:

(1)串行数据输入(IISDI);

(2)串行数据输出(IISDO);

(3)左/右声道选择(IISLRCK);

(4)串行数据时钟(IISCLK);

(5)音频系统主时钟CODECLK。

2 支持IIS的语音控制芯片UDA1341TS的介绍

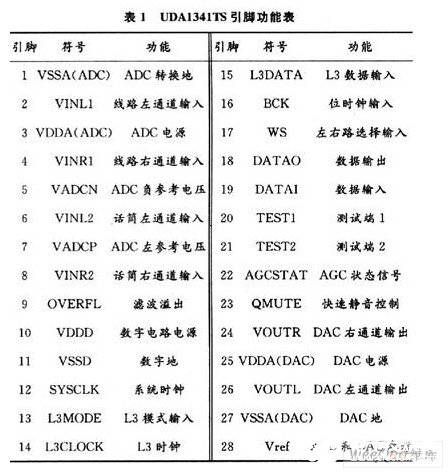

UDA1341TS是Philips公司的一款经济型音频CODEC,用于实现模拟音频信号的采集(音频AD)和数字音频信号的模拟输出(DA),并通过IIS数字音频接口,实现音频信号的数字化处理。具有3 V的低电压、低功耗、高保真,宽动态范围和低失真的高品质特性,大量应用于家庭袖珍多媒体立体声音响设备,笔记本电脑、数字摄像机及计算机音频信号处理设备中。其引脚图如图1所示,其引脚功能如表1所示。

2.1 UDA1341TS的主要特性

UDA1341TS主要特性如下:

(1)低功耗;

(2)3.0 V的电源电压;

(3)256,384,512倍采样频率的系统时钟;

(4)包含AGC的全部继承的模拟前端;

(5)ADC增加了集成的模拟前端;

(6)ADC支持2 V(RMS值)输入信号;

(7)具有为简单电压过载的检测器;

(8)独立的电源控制ADC和DAC;

(9)DAC不必须有后端滤波器;

(10)可通过L3总线管理其功能。

2.2 工作模式

双通道立体声模数转换控制器有4种工作模式:

(1)ADCl输入通道1工作方式(为线路输入),输入通道2关闭;

(2)ADC2输入通道2工作方式(麦克风输入),输入通道1关闭,具有PGA和AGC控制特性;

(3)ADCl+ADC2混合工作方式,具有PGA和AGC控制特性;

(4)ADC1-ADC2混合工作方式。

2.3 L3控制特性

由微处理器与UDA1341TS芯片L3接口,完成下列控制功能:电源控制;芯片复位;数模、模数转换的增益开关;数模、模数转换的极性控制;倍速录音控制;音量、高低音、静音控制;麦克风灵敏度控制;可编程增益放大器控制,数字AGC自动增益控制。

由UDA1341TS的通道2组成可编程增益放大前置双通道立体声模数转换控制电路,可编程的增益放大器(PGA),PGA通过L3接口进行设置,增益可设置为:-3 dB,0 dB,3 dB,9 dB,15 dB,21 dB或27 dB,通道2还具有数字自动增益控制AGC特性,数字式自动增益控制(AGC)范围为60.5 dB,控制步长为0.5 dB。输入通道1有0或6 dB放大增益选择,通过L3接口进行控制,用这种方法输入信号可达到1 V或2 V。

3 UDA1341TS在基于S3C2410X的触摸式语音菜单系统中的应用

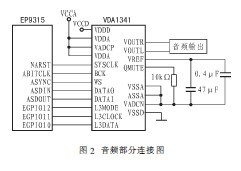

3.1 硬件连接方案

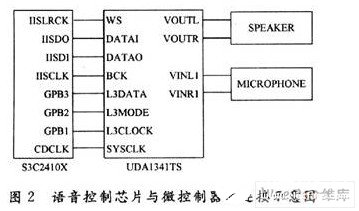

语音驱动芯片UDA1341TS和微控制器S3C2410X的连接如图2所示。

S3C2410X的IIS总线信号与UDA1341TS的IIS信号直接相连。L3接口的引脚L3CLOCK,L3MODE和L3DATA分别连接到S3C2410X的GPBl,GPB2和GPB3通用数据输出引脚。UDA1341TS对外提供两组音频信号输入接口,每组包括左右2个声道。

由于IIS总线只处理音频数据,因此UDA1341TS还内置了用于传输控制信号的L3总线接口。L3接口相当于混音器控制接口,可以控制输入/输出音频信号的低音及音量大小等。L3接口接在S3C2410X的3个通用GPIO输入/输出引脚上,利用这3个I/O口模拟L3总线的全部时序和协议。这里一定要注意L3总线的时钟不是连续时钟,它只在数据线上有数据时才发出8个周期的时钟信号,其他情况下时钟线始终保持高电平。

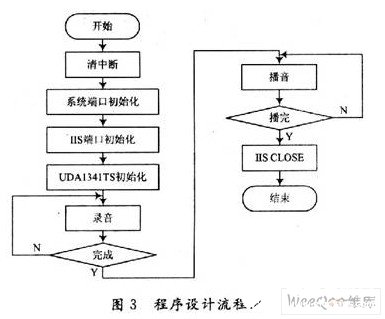

3.2 软件设计方案

该数字语音模块IIS经过正确的配置可以实现录音、放音及循环放音等功能。因为音频数据传输较简单,本文主要介绍软件设计的流程图,流程图如图3所示。

4 结语

介绍了UDA1341TS在基于Samsung公司S3C2410X型微处理器的触摸式语音电子菜单系统中的应用。该系统已经在基于S3C2410X的开发平台上得到了实现,可以顺利进行音频的采集和播放,并取得了良好的效果。

责任编辑:gt

-

芯片

+关注

关注

459文章

51665浏览量

430525 -

嵌入式

+关注

关注

5110文章

19314浏览量

310789 -

总线

+关注

关注

10文章

2917浏览量

88791

发布评论请先 登录

相关推荐

基于ARM7的嵌入式音频处理系统的设计

基于ARM9的UDA1341驱动在Linux下移植方法

音频编解码芯片 VS1005最集成的音频编解码芯片

求推荐音频芯片

采用FPGA实现音频编解码芯片接口

如何利用ARM9设计一种嵌入式音频系统?

UDA1341TS pdf datasheet

基于ARM9处理器的嵌人式音频系统设计

基于μC/OS-II的MP3文件播放系统设计

iis总线:基于IIS总线的嵌入式音频系统设计

基于ARM9的音频系统设计

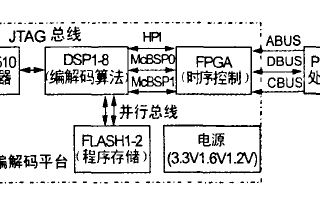

DSP芯片实现语音编解码技术的设计方案

基于音频编解码芯片UDA1341TS和IIS总线接口设计触摸式语音菜单系统

基于音频编解码芯片UDA1341TS和IIS总线接口设计触摸式语音菜单系统

评论