FinFET晶体管架构是当今半导体行业的主力军。但是,随着器件的持续微缩,短沟道效应迫使业界引入新的晶体管架构。在本文中,IMEC的3D混合微缩项目总监Julien Ryckaert勾勒出了向2nm及以下技术节点发展的演进之路。在这条令人振奋的道路上,他介绍了Nanosheet晶体管,Forksheet器件和CFET。其中一部分内容已在2019 IEEE国际电子器件会议(IEDM)上发表。

FinFET:今天最先进的晶体管 在每一代新技术上,芯片制造商都能够将晶体管规格微缩0.7倍,从而实现15%的性能提升,50%的面积减小,40%的功耗降低以及35%的成本降低。几年前,业界为了维持这种微缩路径,从“老式”平面MOSFET过渡到FinFET晶体管架构。在FinFET中,源极和漏极之间的沟道为fin的形式。栅极环绕该3D沟道,可从沟道的3个侧面进行控制。这种多栅极结构可以抑制在栅极长度降低时带来的短沟道效应。

出色的短沟道控制能力至关重要,因为它奠定了器件微缩的基础,允许更短的沟道长度和更低的工作电压。 2012年,首款商用22nm FinFET面世。从那时起,FinFET体系结构进行了持续的改进,以提高性能并减小面积。例如,FinFET的3D特性允许增加fin片高度,从而在相同的面积上获得更高的器件驱动电流。如今,业界正在加快生产的10nm / 7nm芯片也是基于FinFET。在最先进的节点的标准单元大多是6T单元高度,也就是是每个器件最多拥有2根fin。

Nanosheet:器件进化第一步 但是,随着工艺微缩至5nm节点,FinFET架构可能不再是主流。在沟道长度小到一定值时,FinFET结构又无法提供足够的静电控制。最重要的是,向低轨标准单元的演进需要向单fin器件过渡,即使fin高度进一步增加,单fin器件也无法提供足够的驱动电流。

随着技术节点的不断变化,半导体行业并不急于转向其他晶体管架构。一些公司甚至可能决定在某些节点停留更长的时间。但是,仍然存在需要最新的“通用” CMOS解决方案的应用,例如机器学习,大数据分析和数据中心服务器。通过这种通用CMOS解决方案,可以在相同技术节点中使用相同的晶体管架构来实现芯片上所有的功能。 在这里,Nanosheet可以来帮助解围。

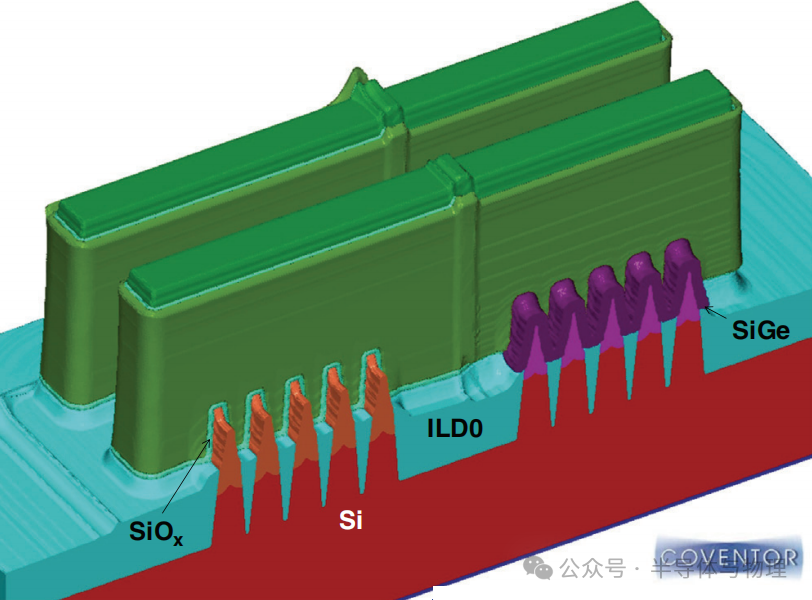

Nanosheet可以被视为FinFET器件的自然演变版本。想象一下将FinFET的沟道水平切割成多个单独Nanosheet沟道,栅极也会完全环绕沟道。与FinFET相比,Nanosheet的这种GAA特性提供了出色的沟道控制能力。同时,沟道在三维中的极佳分布使得单位面积的有效驱动电流得以优化。

从FinFET到Nanosheet的自然演变。

需要微缩助推器 在6T和5T的低单元高度下,向Nanosheet器件的迁移变得最佳,因为在这种情况下,fin的减少会降低传统基于FinFET的单元中的驱动电流。 但是,如果不引入结构化微缩助推器(如埋入式电源轨和环绕式接触),就无法将单元高度从6T减小到5T。

电源轨为芯片的不同组件提供电源,并且一般由BEOL中Mint和M1层提供。但是,它们在那里占据了很大的空间。在嵌入式电源轨结构中,电源轨埋在芯片的前段,以帮助释放互连的布线资源。此外,它们为采用节距微缩而增加BEOL电阻的技术提供了较低的电阻局部电流分布。BEOL没有电源轨后,可以将标准单元的高度从6T进一步降低到5T。

下一步:缩小p和n之间的间距 随着走向更小的轨道高度的旅程的继续,单元高度的进一步减小将要求标准单元内nFET和pFET器件之间的间距更小。但是,对于FinFET和Nanosheet而言,工艺限制了这些n和p器件之间的间距。例如,在FinFET架构中,通常在n和p之间需要2个dummy fin的间距,这最多消耗总可用空间的40-50%。

为了扩大这些器件的可微缩性,IMEC最近提出了一种创新的架构,称为Forksheet器件。Forksheet可以被认为是Nanosheet的自然延伸。 与Nanosheet相比,现在沟道由叉形栅极结构控制,这是通过在栅极图案化之前在p和nMOS器件之间引入“介电墙”来实现的。该墙将p栅沟槽与n栅沟槽物理隔离,从而允许更紧密的n到p间距。

从FinFET到Nanosheet再到Forksheet的自然演变。 用于制造Forksheet的工艺流程与用于制造Nanosheet的工艺流程相似,仅增加一些额外的工艺步骤。n和p之间的介电隔离还具有一些工艺优势,例如填充功函数金属的工艺更简化。在此基础上,由于大幅减少了n到p的间距,预计该Forksheet具有更佳的面积和性能的可微缩性。

Forksheet工艺流程中的关键步骤,即有源区形成后“介电墙”的形成步骤。

Forksheet:性能和面积的改进 IMEC的研究人员最近使用TCAD仿真来量化Forksheet架构的预期PPA潜力。所研究的器件针对IMEC的2nm技术节点,采用42nm的接触栅节距和16nm的金属间距的5T标准单元库。拟议的设计包括一些微缩助推器,例如埋入式电源轨和环绕接触。 与Nanosheet器件相比,已计算出10%的速度增益(恒定功率)和24%的功率减小(恒定速度)。

这种性能提升的部分原因是由于栅极-漏极重叠较小而导致的(寄生)Miller电容减小。可用空间还可以用于增加sheet宽度,从而提高驱动电流。最后,可以利用从n到p的间距减小将轨道高度从5T缩小到4.3T,从而使单元面积减小20%。在SRAM设计中,仿真结果表明,在8nm 的pn间距下,单元面积的微缩比例和性能提高了30%。

SRAM半单元的版图,用于a)FinFET,b)GAA Nanosheet和c)Forksheet。由于pn间距不受栅极扩展(GE),栅极切割(GC)或dummy fin gate tuck(DFGT)的影响,因此Forksheet可以提供高达30%的位单元高度微缩比例。 在从平面到FinFET以及垂直堆叠的Nanosheet的自然进化中,可以将Forksheet视为下一版本。以上特性证明了其作为2nm技术节点的最终逻辑“通用” CMOS器件的潜力。在进一步的研究中,需要解决将这些器件完全投入生产的工艺挑战。

CFET:通往3T逻辑标准单元的道路 小于5T时,单元高度的进一步降低主要受到可布线性问题的限制,而且这个问题应在逻辑区块级别进行评估。为了优化可布线性,我们将进入CFET时代,进一步推动了摩尔定律的发展。 CFET的概念在于将nFET“折叠”在pFET之上,这样就充分利用了器件3D微缩的潜力。 由于具有堆叠特性,CFET拥有2个局部互连层,这为内部单元布线和减小单元面积提供了更大的自由度。单元之间的可布线性也可以大大改善。

CFET架构具有2个局部互连层以及pn 堆叠CMOS基本结构。 初步评估表明,基于FinFET的4T CFET可以对标甚至超过5T“标准” FinFET器件的标准单元功率性能指标。它还可以提供面积缩小25%的标准单元和SRAM单元。基于Nanosheet的CFET可以提供额外的性能提升,并且对于缩小到3T逻辑标准单元来说是必需的。

结论 在本文中,IMEC提出了一条通往2nm及以下技术节点的最终规模化逻辑器件的演进路径。在今天的主流FinFET之后出现了Nanosheet器件,该器件提供了出色的沟道控制功能,同时又增加了有限的工艺复杂性。当配合定标助推器时,具有5T轨道高度的标准单元将触手可及。下一步,Forksheet可能会进场,由于减小了n到p的间距,因此提供了通往4.3T单元的可能性。相关工艺仿真证实了其在2nm技术节点上的潜力。CFET作为最紧凑的CMOS结构,为实现3T逻辑标准单元带来了希望。

责任编辑:xj

原文标题:技术 | 后FinFET时代的技术演进

文章出处:【微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

-

半导体

+关注

关注

335文章

27950浏览量

225005 -

晶体管

+关注

关注

77文章

9829浏览量

139357 -

FinFET

+关注

关注

12文章

253浏览量

90507

原文标题:技术 | 后FinFET时代的技术演进

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶体管故障诊断与维修技巧 晶体管在数字电路中的作用

晶体管与场效应管的区别 晶体管的封装类型及其特点

晶体管的输出特性是什么

NMOS晶体管和PMOS晶体管的区别

CMOS晶体管和MOSFET晶体管的区别

晶体管处于放大状态的条件是什么

芯片晶体管的深度和宽度有关系吗

什么是NPN晶体管?NPN晶体管的工作原理和结构

PNP晶体管符号和结构 晶体管测试仪电路图

如何提高晶体管的开关速度,让晶体管快如闪电

晶体管:后FinFET时代的技术演进

晶体管:后FinFET时代的技术演进

评论