“在依然能够获得良好 SNR 结果的情况下,最差情况的 ADC 时钟可怎样呢?”虽然从来没有客户直接向我提及这一问题,但我的确定期地被问到有关采用不适合高分辨率 ADC 的时钟源之问题。

通常,它需要一个可具有高达 1nsRMS 抖动的函数发生器。常常需要采用一个高质量的 RF 发生器或晶体振荡器以从 16 或 18 位 ADC 获得最佳的 SNR 值,即使在相对较低的输入频率下也不例外。本文我将使用安装了 LTC2389-18 2.5Msps 18 位 ADC 和 LTC PScope 软件的 DC1826A-A 演示板,来说明抖动对于 SNR 性能的影响以及怎样降低一个噪声时钟源的抖动。

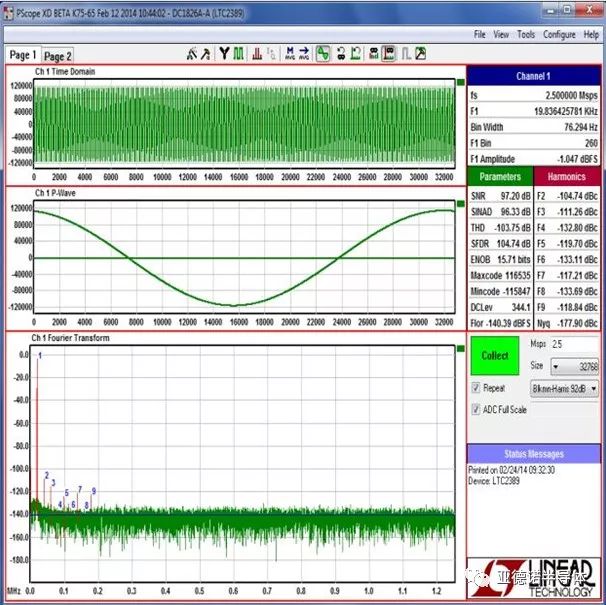

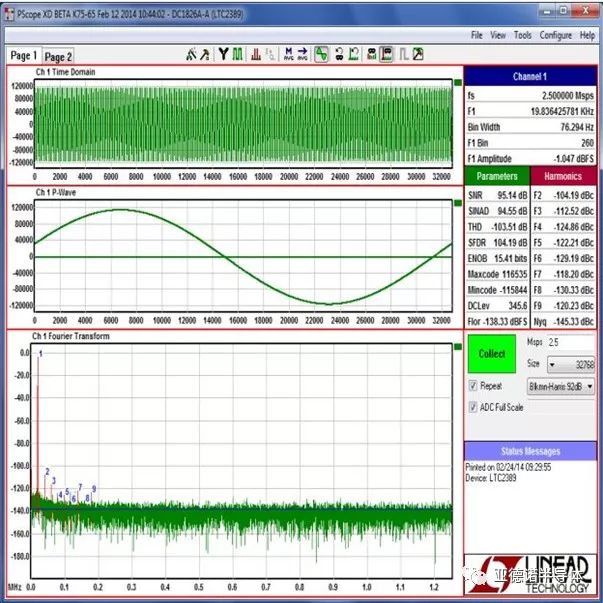

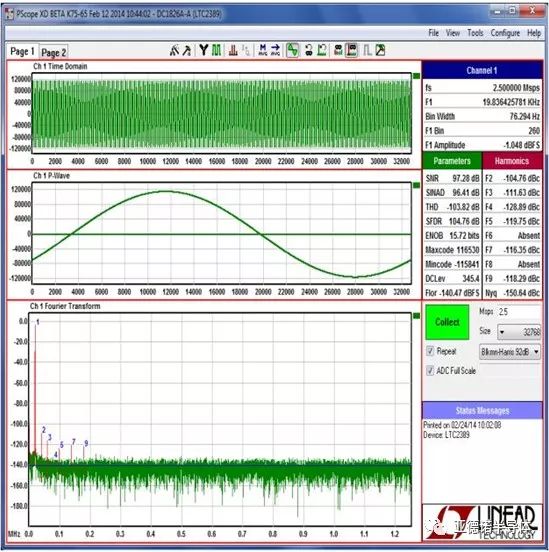

作为基线,DC1826A-A 的时钟输入采用一个罗德与施瓦茨 SMB100A RF 发生器来驱动,并由 Stanford Research SR1 提供模拟输入。结果是图 1 中的 PScope 数据,其产生一个 98.247dBFS SNR。

图 1:基线 FFT 显示:对于 LTC2389-18,SNR 为 98.247dBFS

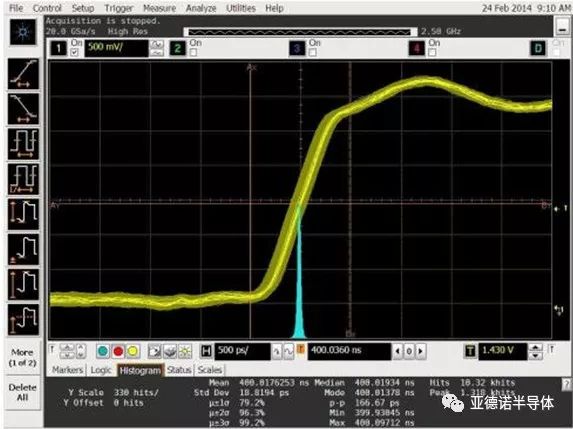

该 SNR 是通过将低于全标度的输入电平 (-1.047dBFS) 加至已测 SNR 获得的。ADC 之 CNV 输入端上的 18.8psRMS 抖动可采用一台 Agilent Infiniium 9000 系列示波器或同等档次的示波器进行测量。基于抖动和输入频率的 SNR 理论极限值为

20 * log (2 * π * fIN * tjitter)

其中:

tjitter 为 RMS 抖动

fIN 为输入频率

代入针对该例的数值得出的SNR 为

20 * log (2 * π * 20kHz * 18.8ps) = 112.5dB

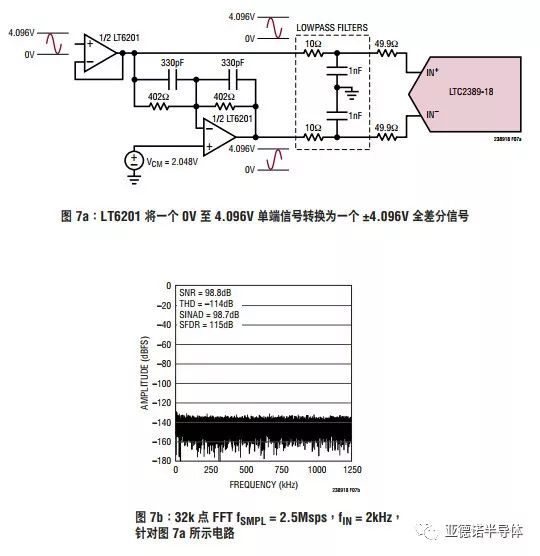

随后必须将该值与 ADC SNR 进行 RMS 求和运算以产生一个有效 SNR。查看 LTC2389 的产品手册,在 2kHz 频率下用于演示板电路 (图 7a 和 7b) 的典型 SNR 为 98.8dB。

LTC2389 的产品手册,图 7a 和 7b

产品手册中给出的“SNR 与输入频率的关系曲线”显示:在本实验所采用的 20kHz 输入频率下,SNR 产生大约 0.3dB 的滚降,因此 98.8dB 的数字将调节至 98.5dB。98.5dB 与 112.5dB 的 RMS 之和为 98.3dB,这近似于图 1 中获得的结果。

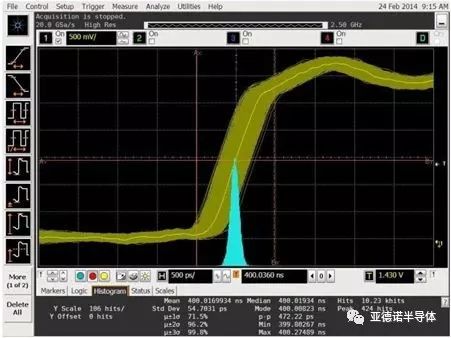

图 2:DC1826A-A 之 CNV 输入端上的 RMS 抖动 (采用 SMB100A 时钟源)

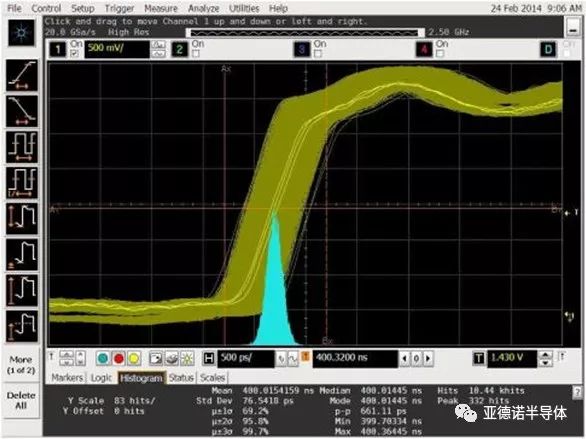

既然已经获得了一个基线 SNR 测量结果,那么假如使用一个具较高抖动的时钟源会发生什么呢? 如图 3 所示,当采用 XXXX-YYYYY (制造商及型号隐去) 发生器时,测得的抖动为 76.5psRMS。在该抖动水平下的SNR 理论极限值为 100.3dB,当其与 LTC2389-18 的 98.5dB 进行 RMS 求和运算时,得出的结果为 96.3dB。

图 3:噪声时钟源在 DC1826A-A 的 CNV 输入端上产生 76.5psRMS 抖动

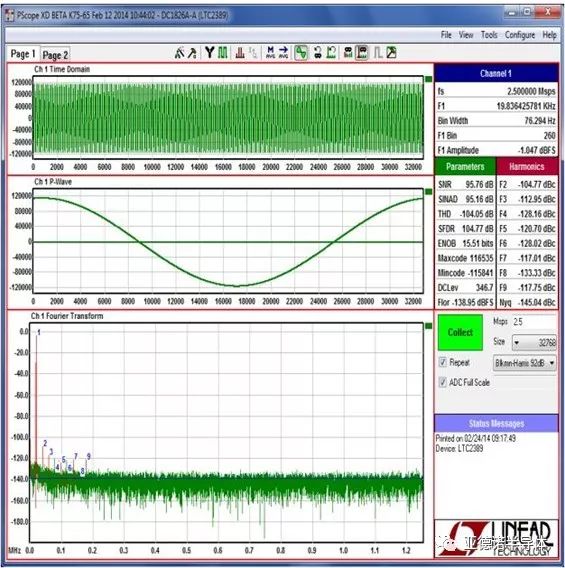

图 4 的 PScope 截屏中示出的 96.2dBFS 测量 SNR 基本吻合。在相对较低的 20kHz 输入频率下,SNR 指标降低了 2dB,且附加的时钟抖动小于 60ps。在 100kHz 输入频率下,SNR 将降至 86dB。

图 4:采用噪声时钟源时 LTC2389-18 的 SNR 指标降低至 96.2dBFS

问

噪声时钟源 (例如:刚刚检查的时钟源) 上的抖动可以减低吗?

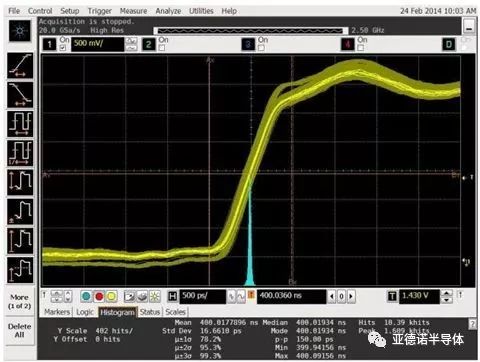

采用先前的时钟源,在时钟的输出和演示板的时钟输入之间插入一个 TTE 低通滤波器。测得的时钟抖动减小至 54.7psRMS (如图 5 所示),而最终的 SNR 则改善至 96.8dBFS (如图 6 给出的 PScope 截屏所示)。

图 5:噪声时钟源的低通滤波降低了 CNV 输入端上的抖动

图 6:噪声时钟源的低通滤波轻微改善了 SNR

虽然取得了小幅改善,但其仍然不如基线 SNR 测量结果那么好。接着,插入一个 TTE 带通滤波器以替代低通滤波器。现在,测得的时钟抖动为 16.7psRMS (如图 7 所示),而 SNR 的测量结果则显著地改善至 98.3dBFS (如图 8 给出的 PScope 截屏所示)。测得的 SNR 此时与基线 SNR 测量值相同。

图 7:TTE 带通滤波器极大地降低了抖动

图 8:TTE 带通滤波器显著地改善了 LTC2389-18 的 SNR 指标

现在可以很容易的了解在评估高分辨率 ADC 时采用低抖动时钟源的必要性。如果您现有可用的时钟源不具备足够低的抖动,那么通过利用一个优良的带通滤波器对时钟实施滤波仍然能够获得上佳的 SNR 测量结果。

责任编辑:lq

-

adc

+关注

关注

98文章

6496浏览量

544476 -

发生器

+关注

关注

4文章

1368浏览量

61678 -

晶体振荡器

+关注

关注

9文章

618浏览量

29106

原文标题:在评估高分辨率 ADC 时,这个步骤很重要!

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

抖动对于SNR性能的影响以及怎样降低一个噪声时钟源的抖动

抖动对于SNR性能的影响以及怎样降低一个噪声时钟源的抖动

评论