摘要: 针对当前无人机数据链日趋小型化,采用射频收发一体化设计,基于FPGA 对零中频射频收发器AD9361 进行配置,实现机载视频和遥控遥测的无线传输。测试结果表明,该设计可以实现无人机与地面站之间数据的可靠传输,同时满足小型无人机对数据链体积、重量、功耗和低成本的要求。

无人机数据链是实现无人机与地面站之间双向传输信息的无线通信系统,主要完成机载视频的实时下传、载荷控制及状态回报和遥控遥测信息的分发

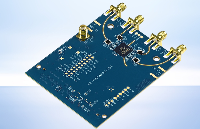

[1]。其中射频收发系统是无线传输的重要组成部分,针对小型无人机数据链体积小、重量轻、功耗低等特点,一般的集成式宽带收发器解决方案在性能、可调带宽方面受限,缺乏实现实用性; 而分立式软件定义无线电( SDR) 的设计成本高昂,缺乏有效的硬件和RF 信号链设计技术,从而导致开发周期过长,因此,需要一款高度集成式软件定义RF 收发器

[2]。集成式RF 收发器AD9361 的优势在于为多种无线电方案提供统一的可再编程软件无线电平台,具备出色的灵活性和可配置性以及支持现场升级

[3]。 姜浩等人提出采用PC + FPGA 配置AD9361 的方法,PC 机通过PCIe 接口将配置指令发送到FPGA,FPGA 通过SPI 接口发送配置指令到AD9361

[4]。Jorge Santos 等人提出采用FPGA + MicroBlaze的方案配置AD9361,并在Xilinx KC705 开发板上进行了实现和验证

[5]。方良提出利用FPGA+ ARM 的方式实现AD9361 的配置,基于Zedboard和AD9361子板建立软件无线电平台进行双向视频的传输

[6]。本文提出一种FPGA 独立实现AD9361配置的方案,该方案满足小型数据链对于功耗、体积和成本的严苛要求,同时不受FPGA 型号的限制,可方便移植于不同的FPGA 平台。 1 整体系统方案

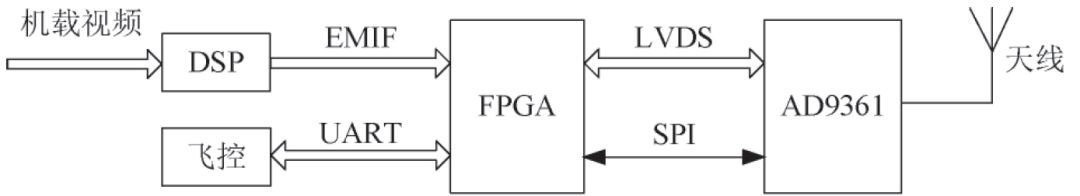

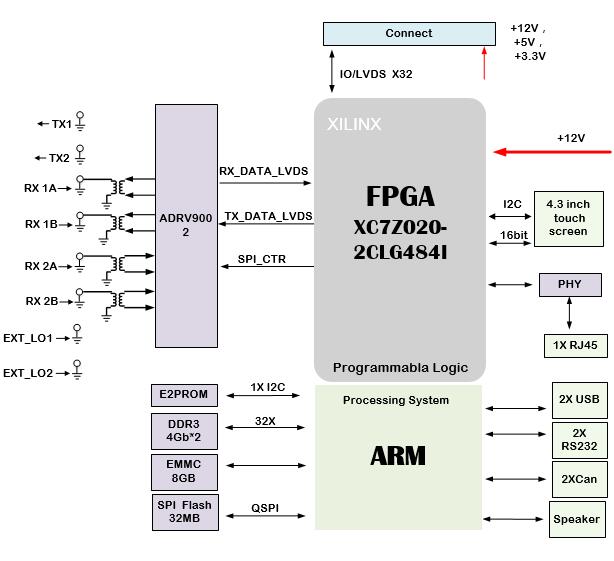

无人机机载数据链设备的系统架构如图1 所示。

首先,FPGA 通过EMIF 接收DSP 的高清压缩视频、通过UART 接收飞控计算机的遥测数据,压缩后的视频数据和遥测数据在FPGA 组帧编码调制后通过LVDS 发送到AD9361,AD9361 对数据进行上变频后经由天线发射出去; 同时,AD9361 对天线接收到的信号进行下变频后,通过LVDS 将地面的遥控数据发送到FPGA,数据在FPGA 中经过解调译码解帧后通过UART 发送到飞控计算机中。其中,AD9361 的配置是FPGA 通过SPI 读写寄存器完成的。

图1 无人机机载数据链设备的系统架构图

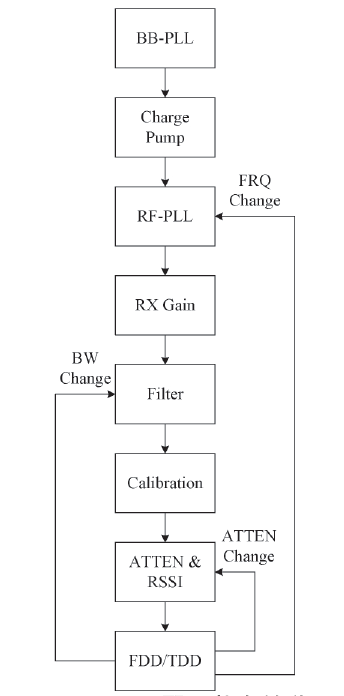

2 AD9361 配置流程AD9361 有0 - 0x3FF 共1 024 个寄存器,有些寄存器不需要配置,保持上电默认值即可,而有些寄存器需要进行多次写入,比如fir 滤波器、增益表等[7 - 8]。图2 给出了AD9361 配置的状态转移图。

图2 AD9361 配置状态转移图

BB - PLL: BB - PLL ( Base Band PLL,基带锁相环) 状态是AD9361 初始化配置的起始状态,该状态设置了晶振的输入类型、参考时钟频率、AD9361内部基带锁相环频率和环路滤波器参数、单双通道选择等。SPI 读0x5E 寄存器最高位为1 则说明基带锁相环成功锁定。

Charge Pump: Charge Pump ( 电荷泵) 状态是对AD9361 内部电荷泵的电流进行设置并校准,接收电荷泵设置0x23D 寄存器,发射电荷泵设置0x27D 寄存器。 RF - PLL: RF - PLL ( Radio Frequency PLL,射频锁相环) 状态对AD9361 的发射和接收频率进行设置,包括射频锁相环的频率、压控振荡器参数、环路滤波器参数、混频器增益表等。

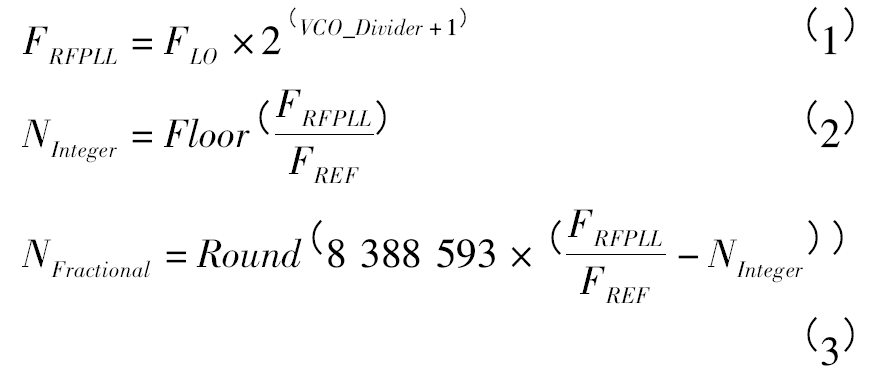

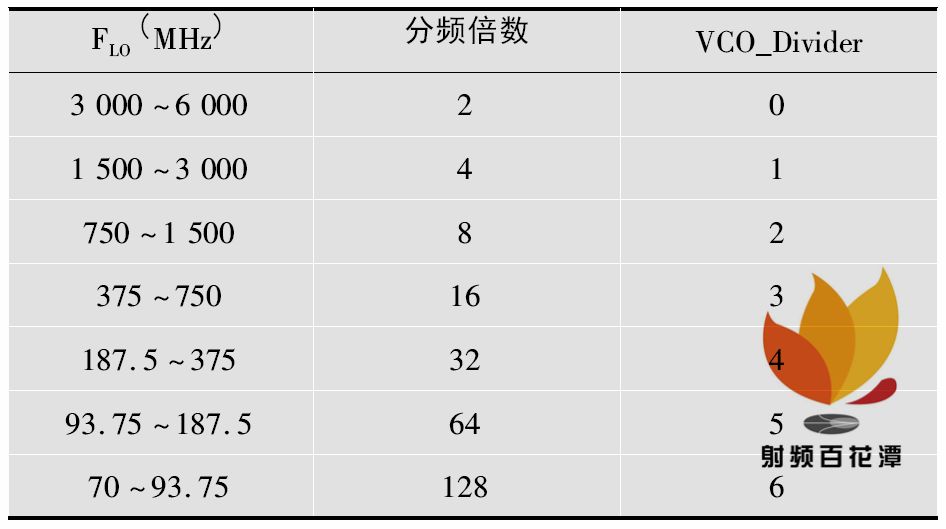

其中,压控振荡器和环路滤波器的参数分别写入到FPGA 的rom ip 核中,通过查找表的方式进行调用。射频锁相环的频率范围是6 ~ 12 GHz,发射和接收频率范围是从70~ 6 000 MHz,发射频率和接收频率是独立的,即使精度设为1 MHz,如果将整个频率范围都存入rom ip核,至少需要存11 000 多组数据,无论是工作量还是存储空间都是巨大的,因此为了优化设计,发射频率和接收频率的设置通过式1 ~ 式3 来实现。

以发射频率为例,式1:FLO为AD9361 的发射频率,FRFPLL为发射锁相环频率,VCO_Divider 是锁相环分频,根据表1 选择相应VCO_Divider 的值,例如AD9361 的发射频率FLO设置为4 635 MHz,则对应的VCO_Divider 为0,然后根据式1 得到发射锁相环的频率FRFPLL为9 270 MHz。

由于在BB - PLL 状态中已经将FREF参考时钟设置为40MHz,那么通过式2就可以得到发射频率的整数部分NInteger = 0xE7 并写入到AD9361 的0x271 和0x272 寄存器中,通过公式3 得到发射频率的小数部分NFractional = 0x5F_FFF5并写入0x273 - 0x275 寄存器中。设置接收频率的公式和发射频率相同,不同的是接收频率的整数部分NInteger要写入AD9361 的0x231 和0x232 寄存器,NFractional写入0x233 - 0x235 寄存器。

表1 发射频率FLO与锁相环分频VCO_Divider 的对应关系

RX Gain: RX Gain( 接收增益) 状态包括对LNA( 低噪声放大器) 、TIA( 跨阻放大器) 、LPF( 低通滤波器) 、接收增益表、增益控制方式等进行配置。接收增益表分为整体表和分立表,整体表配置简单,分立表配置复杂但是抗干扰能力更强。不同的频率范围又对应着不同的增益表,接收频率为70 ~ 1 550MHz、1 551 ~ 3 650 MHz、3 651 ~ 6 000 MHz 时需要设置不同增益表来调整输入信号的增益。

增益控制方式分为自动增益控制( AGC) 和手动增益控制( MGC) ,自动增益控制又分为快速增益和慢速增益,通常情况下,时分双工模式( TDD) 采用快速自动增益,而频分双工模式( FDD) 采用慢速自动增益。

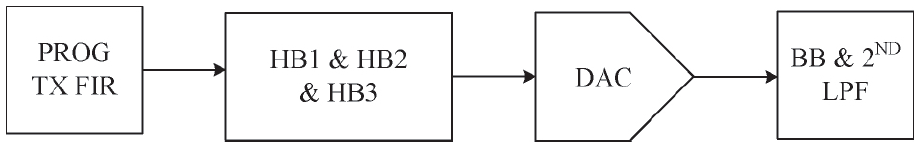

Filter: Filter( 滤波器) 状态是对AD9361 内部的数字和模拟滤波器进行配置,发射和接收端各有4个数字滤波器和2 个模拟滤波器,图3 给出了发射端滤波器的通路,经过编码后的IQ 两路数据先后经过FIR 滤波器和HB1、HB2、HB3 等3 个半带滤波器插值后送入DAC 进行数模转换,接下来用一个3 阶巴特沃斯低通滤波器BB LPF 和一个单极低通滤波器2ND LPF 来减小模拟信号的带外杂散。

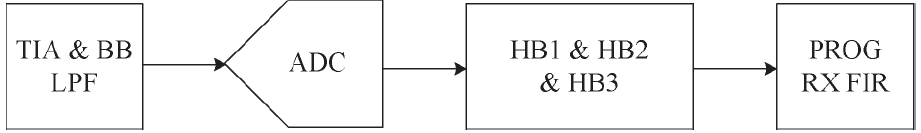

图4 给出了接收端滤波器的通路,天线接到的模拟信号经过一个单极低通滤波器TIA LPF 和一个3 阶巴特沃斯低通滤波器BB LPF 后进入到ADC 中进行模数转换,然后经过HB1、HB2、HB3 等3 个半带滤波器和FIR 滤波器输出IQ 两路数据到后面的数字信号处理模块。

图3 AD9361 发射信号滤波器通道

图4 AD9361 接收信号滤波器通道

Calibration: Calibration( 校准) 状态包括基带直流偏置校准、射频直流偏置校准、发射正交校准、接收正交校准跟踪、基带和射频直流跟踪校准。校准的目的是通过对直流偏置、增益、相位误差等进行改善来提高系统的性能,各个校准所需要的时间跟发射和接收频率成反比,频率越高,校准时间越短。

ATTEN&RSSI: ATTEN( Attenuation,衰减控制)和RSSI( Receive Signal Strength Indicator,接收信号强度指示) 状态包括发射信号的衰减值和接收信号强度的指示。衰减值可设置的范围是0 ~ 89. 75dBm,精度是0. 25 dBm,RSSI 显示与实际信号大小成反比,信号越强,RSSI 值越小。

FDD/TDD: FDD( Frequency Division Duplex,频分双工) 或TDD( Time Division Duplex,时分双工) 状态通过配置0x13 - 0x15 寄存器切换AD9361 内部的ENSM 状态机来实现FDD 或者TDD,AD9361 正常工作时的一直保持该状态。

当FPGA 接收到切换频率( FRQ change) 指令时,状态机从FDD/TDD 状态跳转到RF - PLL 状态,改变发射或接收频率后再跳转到FDD/TDD 状态正常工作; 当FPGA 接收到切换带宽( BW change) 指令时,状态机从FDD/TDD 状态跳转到Filter 状态,改变滤波器带宽后再跳转到FDD/TDD 状态正常工作;当FPGA 接收到切换衰减( ATTEN change) 指令时,状态机从FDD/TDD 状态跳转到ATTEN&RSSI 状态,改变衰减值后跳转到FDD/TDD 状态正常工作。

3 系统测试

3.1 单音测试

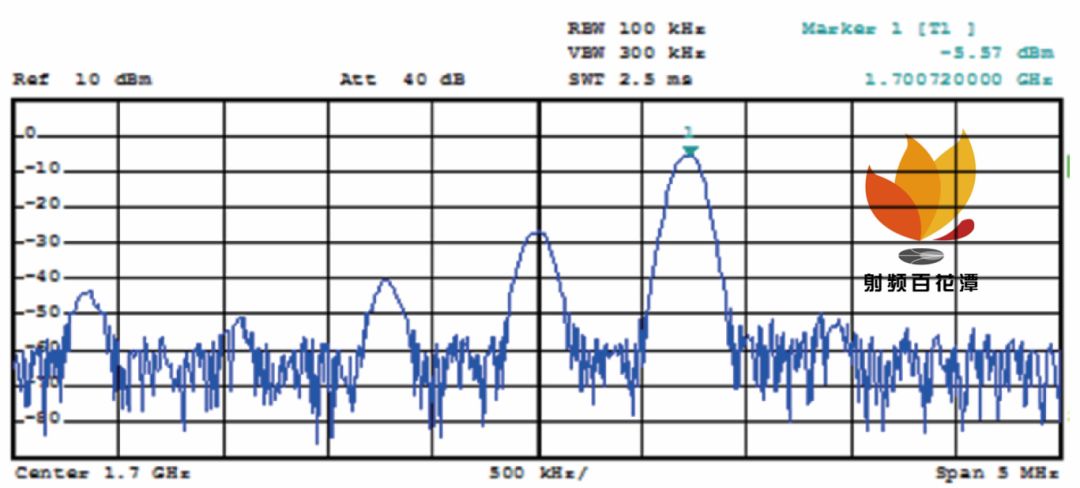

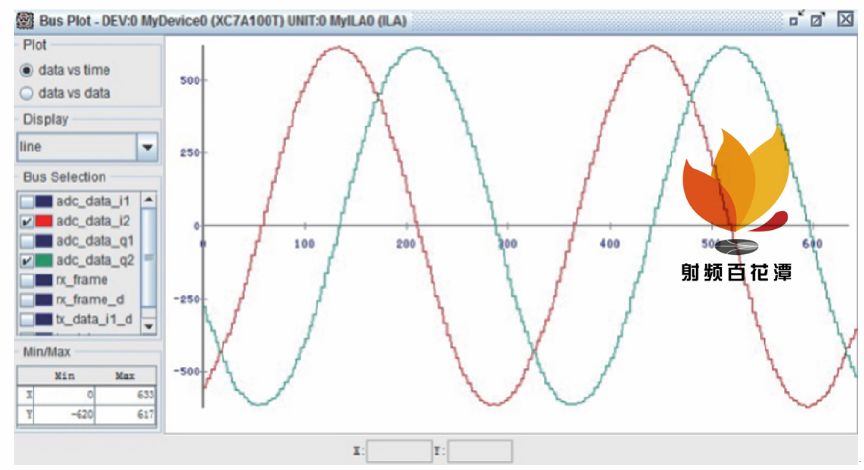

基于Artix7 - 100T FPGA 配置AD9361 发射和接收频率1. 7 GHz,发射和接收带宽1 MHz,发射衰减10 dBm,双工模式为FDD,单发单收。FPGA 内部生成一个DDS ip 核,DDS 产生720KHz 的正弦波和余弦波作为AD9361 的I 路和Q 路发射数据,图5 给出了单音频谱,可以看出频谱从1. 7 GHz 向上搬移了720 KHz,输出功率为- 5. 57dBm。图6 是ChipScope采集到AD9361 实时接收的数据,正确的还原出了发射的IQ 两路信号。

图5 AD9361 单音频谱 3.2 宽带测试

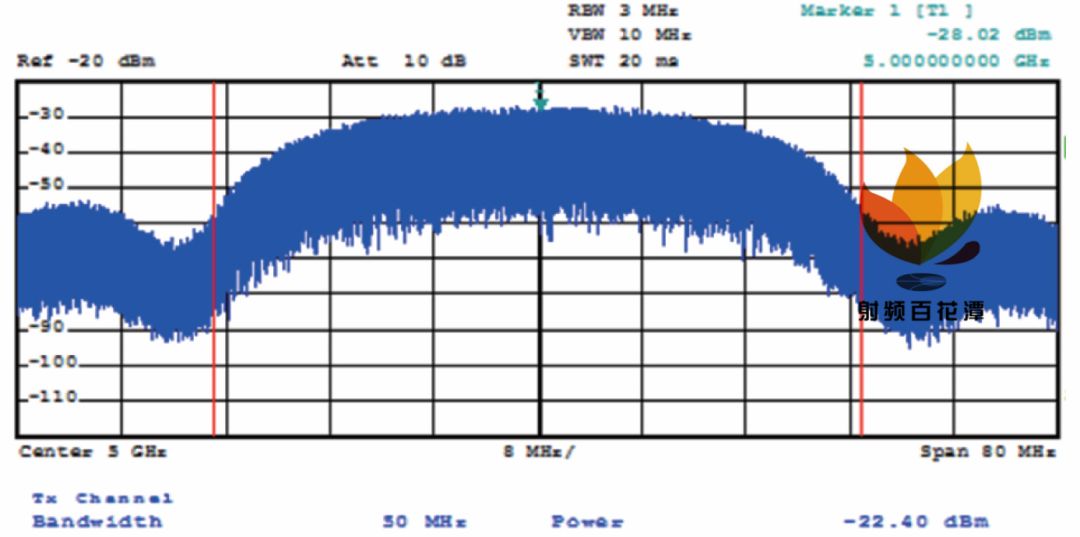

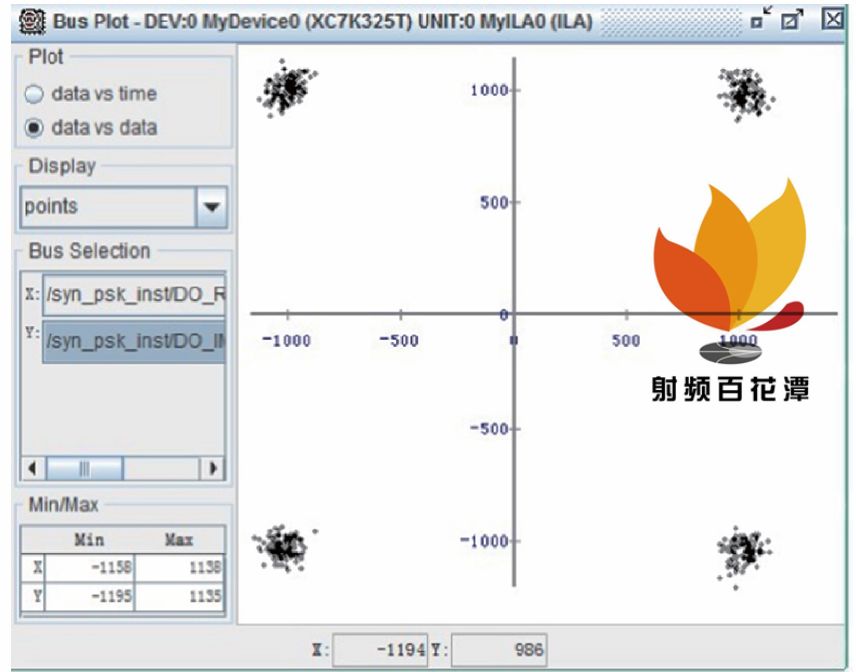

基于Kintex7 - 325T FPGA 配置AD9361 发射和接收频率5 GHz,发射和接收带宽48MHz,发射衰减25 dBm,双工模式为FDD,单发双收。FPGA内部产生一个32Mbps 业务速率的QPSK 信号,符号速率55Mbps,经过成型滤波后送入AD9361 的IQ 两路,图7给出了QPSK 调制信号的发射频谱,中心频率为5GHz,通道功率为- 22. 4 dBm。图8 给出了AD9361接收到信号后经过QPSK 解调的星座图,能够看出信号解调正常,可以进行后续的译码解帧等工作。

图6 ChipScope 采集AD9361 的IQ 两路数据

图7 QPSK 调制信号的发射频谱

图8 QPSK 解调后星座图 3.3 资源占用

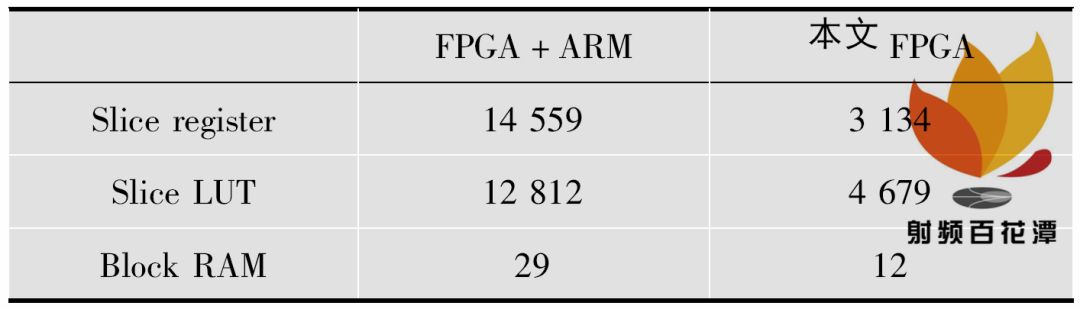

分别用ADI 官方提供的FPGA + ARM 方式和本文FPGA 的方式配置AD9361,表2 给出了在Zedboard开发板上布线后的资源占用情况,通过对比可以看出,本文采用的FPGA 独立配置AD9361 方式比FPGA + ARM 方式在资源上节省了60%以上。

表2 不同方式配置AD9361 占用FPGA 资源情况结论本文详细的介绍了基于FPGA 独立实现AD9361 射频收发器的配置方法和步骤,该方法比ADI 官方提供的FPGA + ARM 或FPGA + MicroBlaze等解决方案更加通用,会大幅降低FPGA 的资源占用率。

本文分别在Xilinx 平台Artix - 7、Kintex - 7、Zynq - 7000 等三种不同型号FPGA 上实现了AD9361 的配置,说明该方法方便移植于任意型号FPGA,甚至可以通过生成网表文件跨平台使用。此外由于不需要DDR3 作为缓存,可以节约硬件电路板卡的面积、整体功耗和成本。本方案可实现机载数据链的小型化和低成本,满足在军品和民品领域无线视频传输和遥控遥测的需求。

责任编辑:xj

原文标题:FPGA+AD9361 SDR实现机载视频无线传输

文章出处:【微信公众号:FPGA入门到精通】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22508浏览量

639440 -

SDR

+关注

关注

7文章

242浏览量

52061 -

AD9361

+关注

关注

8文章

35浏览量

38476

原文标题:FPGA+AD9361 SDR实现机载视频无线传输

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Type-C接口如何实现视频传输?

请教:6G 确定性通信原型验证,FPGA+SDR 方案该怎么搭?

FEC前向纠错技术:让无线传输“自我修复”的通信卫士

基于AMD FPGA的HDMI2.1接口实现

FEC前向纠错技术:让无线传输“自我修复”的通信卫士

2025年视频传输模块技术方案与应用指南解析

通过FPGA控制ADV7513芯片实现HDMI音视频输出

2025全球无线视频传输模块技术对比与应用方案解析

设计资料原理图:622-基于ADRV9002 +ZYNQ7020 的软件无线电 SDR(升级AD9361)

2025年高性能无线视频传输模块厂商及应用方案深度解析

2025无线视频传输模块选购指南与应用方案推荐

软件无线电-AD9361 璞致 PZSDR 软件无线电系列板卡之PZ-FL9361(FMCOMMS3)使用说明

如何对FX3进行编程以便通过USB 3.0从FPGA -> FX3 -> PC传输RGB888视频?

【PZSDR AD9361】——璞致PZ-FL9361 软件无线电模块:工业级射频解决方案的技术标杆

如何通过FPGA+AD9361 SDR实现机载视频无线传输

如何通过FPGA+AD9361 SDR实现机载视频无线传输

评论