时间的重要性不言而喻,加上时间这个维度就如同X-Y的平面加上了一个Z轴,如同打开了一个新的世界。所以今天我们就要来聊聊时序电路。

在时序电路中,电路任何时刻的稳定状态输出不仅取决于当前的输入,还与前一时刻输入形成的状态有关。是不是有点绕?这样,下次当你和对象吵架时,她把以前各种旧账翻出来一起算的时候,你别急着还嘴,赶紧趁机温习一下时序电路的概念,也许你想着想着就笑了。

总之……时序电路是有记忆功能的,因此可以设计成储存电路用来保存信息。常用的存储电路有两类:一类采用电平触发,我们称为锁存器(Latch);另一类通过边沿信号触发,也就是触发器(Flip-flop)。中文译法经常有一种不明觉厉的感觉有木有。 事实上,触发器的工作原理并不复杂。首先我们来看图1。

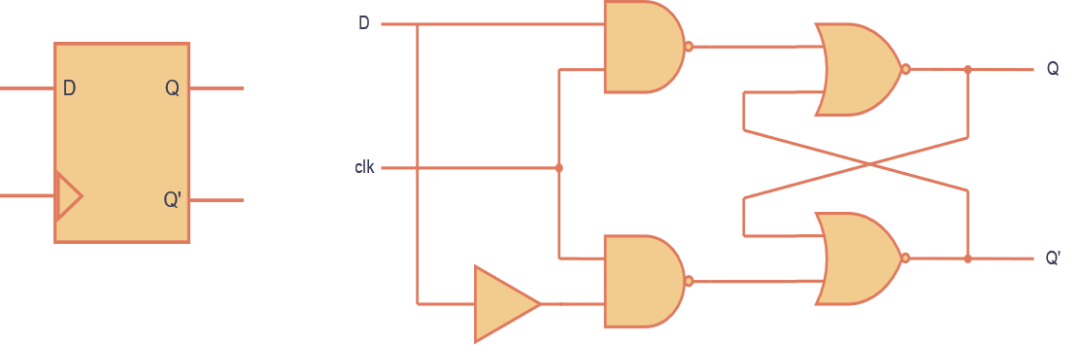

图1D触发器框图和内部门电路结构

图1所示的是一个D类触发器的框图和内部门电路结构。框图中输入端的三角形代表着时钟信号边沿触发方式。同学们可以通过门电路结构研究D类触发器的工作原理,在这里我们直接给出它的状态特性表:

| CLK | D | Q | Q’ |

| X | X | X | Q |

| X | 0 | 0 | 0 |

| ↑ | 0 | 1 | 1 |

| ↑ | 1 | 0 | 0 |

| ↑ | 1 | 1 | 1 |

其中,向上的箭头表示时钟信号从低升至高电平时触发有效;反之,从高电平降至低电平的边沿触发方式则由向下的箭头表示。现在我们给出D类触发器的Verilog代码:

module dff2 ( input clk,d, output reg q, output wire qbar ); assignqbar=~q;always@(posedgeclk)//只有clk上升沿时刻触发q<= d; // 只有当触发生效时,才将d的值赋予给q endmodule 上述代码的意思差不多等效于:你不起床就别想让我起床。就算你起床了,如果没把早餐做好,我还是不起床。 现在,我们已经有了代码,如何在小脚丫上进行实验呢?其他的好说,问题是我们要处理一下时钟信号的问题,也就是代码中的clk变量。

通常,输入变量clk直接会被指定到小脚丫的板载时钟信号上。不过,小脚丫的固定时钟信号频率为12兆赫兹,比人眼能分辨出的频率快近几十万倍,所以我们根本不可能观察到任何变化。 在我们学习时钟分频之前,观察本次实验的最好办法,就是通过手动时钟信号。因此,我们将变量分配至小脚丫的以下管脚:

| 变量 | 小脚丫元件 | FPGA管脚 |

| clk | SW1 | J12 |

| d | SW4 | H13 |

| q | L1 | N15 |

| qbar | L2 | N14 |

理论上说,将上述程序及管脚分配导入至小脚丫后,可以通过调节开关SW1和SW4来观察q和qbar的状态(L1和L2)。 我知道很多人手里没有小脚丫,并且也懒得去www.stepfpga.com上购买,所以我就抛一个问题让大家隔空思考一下(才知道微信把公众号留言功能给关闭了):假如说,这个程序在仿真上的结果是正确的,但是导入小脚丫之后就不正常工作了,你觉得会是什么原因?

责任编辑:xj

原文标题:基于FPGA的数字电路实验5:时序电路之触发器

文章出处:【微信公众号:FPGA入门到精通】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1629文章

21744浏览量

603590 -

时序电路

+关注

关注

1文章

114浏览量

21703 -

数字电路

+关注

关注

193文章

1606浏览量

80639

原文标题:基于FPGA的数字电路实验5:时序电路之触发器

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

时序电路之触发器

时序电路之触发器

评论