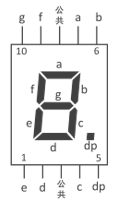

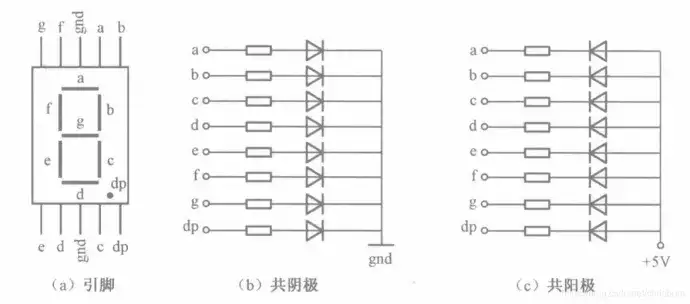

小脚丫板载的数码管是7段数码管(如果包括右下的小点可以认为是8段),它分别由a、b、c、d、e、f、g位段和表示小数点的dp位段组成,见图1。

图1 7段数码管

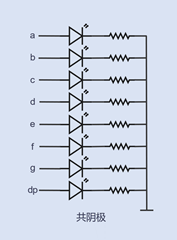

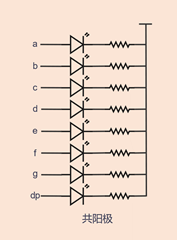

图1 7段数码管数码管的各个段位是由LED灯组成的,控制每个LED的点亮或熄灭实现数字显示。通常数码管分为共阳极数码管和共阴极数码管,结构如图所示。共阴8段数码管的信号端低电平有效,而共阳端接高电平有效。比如,使共阳端数码管的a段发光,则在a段信号端加上低电平即可。共阴极的数码管则相反。

小脚丫的板载数码管为7段共阴极数码管,可以显示数字0-9以及字母A-F共计16种选择。因此,如果我们需要数码管能显示所有的16种选择,需要至少4位输入码(24=16)。表1列出了各个数码管字符所对应的LED灯段位。

表1各数码管字符所对应的LED灯段位

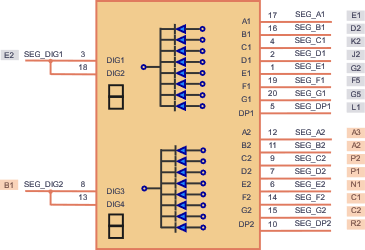

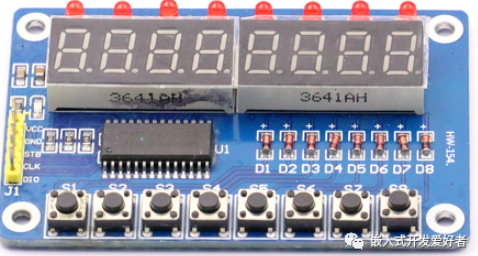

图2标注了小脚丫板载的两个数码管的各LED段位以及小脚丫上所对应的引脚。其中SEG_DIP为公共端,因此在共阴极数码管的设计中需要接低电平。可以看出,每一个数码管都含有9个引脚,因此每一个字符的显示都需要由一个9位的输出信号来实现。

接下来我们通过Verilog实现对数码管的控制。其中,我们将模块的输出定义为两个7段数码管,每个数码管有9个引脚,分别由9位信号控制。输入端由4路信号控制,可以分别对应0-F等十六个字符选择。

module segment(input wire[3:0] seg_data_1, //四位输入数据信号,可通过4个拨码开关控制input wire[3:0] seg_data_2, //四位输入数据信号,可通过4个按键开关控制output wire[8:0] segment_led_1, //数码管1,MSB~LSB =SEG,DP,G,F,E,D,C,B,Aoutput wire[8:0] segment_led_2 //数码管2,MSB~LSB =SEG,DP,G,F,E,D,C,B,A);reg[8:0] seg [15:0]; //存储7段数码管译码数据initialbeginseg[0]=9'h3f; // 0seg[1]=9'h06; // 1seg[2]=9'h5b; // 2seg[3]=9'h4f; // 3seg[4]=9'h66; // 4seg[5]=9'h6d; // 5seg[6]=9'h7d; // 6seg[7]=9'h07; // 7seg[8]=9'h7f; // 8seg[9]=9'h6f; // 9seg[10]=9'h77; // Aseg[11]=9'h7C; // bseg[12]=9'h39; // Cseg[13]=9'h5e; // dseg[14]=9'h79; // Eseg[15]=9'h71; // Fendassign segment_led_1 = seg[seg_data_1]; // 将对应字符导入数码管1并显示assign segment_led_2 = seg[seg_data_2]; // 将对应字符导入数码管2并显示endmodule

上述代码是定义7段共阴极数码管的通用模块,可以保存起来作为一个独立模块。这样,在以后遇到需要用数码管显示的实验时我们可以直接调用(之后我们还会讲解如何调用子模块),而不用再重新写一遍代码。

接下来是提问环节:

当我们指定用拨码开关SW1-SW4来控制左边数码管,按键开关K1-K4来控制右侧数码管,此时如果开关的状态分别如下图所示,数码管应该显示什么字符?

而为了帮助更多老师快速上手FPGA的使用和教学,在即将到来的寒假,我们针对高校从事教学/实验室一线工作的教师,推出一个为期5天(2021年1月25日-1月29日)的FPGA设计及应用快速培训,通过实用性非常强的典型案例动手实践,帮助大家快速、有效地上手FPGA,并能够在未来的教学、实践、电赛中大显身手,硬禾实战营也将成为参加培训的老师们长期的教学后援。

责任编辑:xj

原文标题:基于FPGA的数字电路实验3:点亮数码管

文章出处:【微信公众号:FPGA入门到精通】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1629文章

21748浏览量

603966 -

数码管

+关注

关注

32文章

1882浏览量

91189 -

数字电路

+关注

关注

193文章

1606浏览量

80667

原文标题:基于FPGA的数字电路实验3:点亮数码管

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

通过小脚丫板载的两个数码管来显示字符

通过小脚丫板载的两个数码管来显示字符

评论