GAL(Generic Array Logic, GAL,通用数组逻辑)以PAL(可编程数组逻辑,PLD的一种)为基础,此是由莱迪思半导体公司所发明,GAL的特性与PAL相同,不过PAL的电路配置、配置只能进行一次的程序刻录,不能再有第二次,而GAL则可反复对电路配置、配置进行刻录、清除、再刻录、再清除。

这种可重复刻录的特性,让GAL在研发过程时的试制阶段(prototyping stage)特别好用,一旦在逻辑电路的设计上发现有任何程序错误,若是用GAL就能以重新刻录的方式来修正错误。 此外,GAL也可以用PAL的刻录器来进行刻录及再刻录。 还有PEEL(Programmable Electrically Erasable Logic),与GAL类似,PEEL由International CMOS Technology公司提出。 CPLD

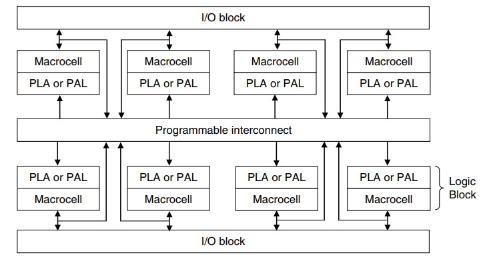

PAL、GAL仅适合用在约数百个逻辑门所构成的小型电路,若要实现更大的电路,则适合用CPLD(Complex PLD,复杂型PLD),一颗CPLD内等于包含了数颗的PAL,各PAL(逻辑区块)间的互接连线也可以进行程序性的规划、刻录,运用这种多合一(All-In-One)的集成作法,使一颗CPLD就能实现数千个,甚至数十万个逻辑门才能构成的电路。 有些CPLD可以用PAL的刻录器来进行刻录,但这种刻录方式对经常有数百只接脚的CPLD来说并不方便。

另一种刻录方式是CPLD已焊于印刷电路板上,之后透过额外的临时外接,或原有线路的内接,使CPLD与个人电脑间能获取连线,由个人电脑以串列或并行方式将新的刻录资料发送到CPLD上,而CPLD内部也具有解码电路能对接收到的资料进行还原解析,之后再进行重新的刻录,以此方式让CPLD内的程序获得更新。 FPGA

FPGA(Field Programmable Gate Array,FPGA),场式可编程闸数组或现场可编程闸数组,是以闸数组(Gate Array)技术为基础所发展成的一种PLD。 FPGA运用一种逻辑门式的网格(Grid),这种网格与普通的「闸数组」相类似,网格可以在FPGA芯片出厂后才进行配置配置的程序性规划。 FPGA通常也可以在焊接后再进行程序刻录、变更的工作,这某种程度上与大型的CPLD相似。

绝大多数的FPGA,其内部的程序配置配置是易失性的,所以在设备重新获得电力后,就必须将配置配置内容重新加载(re-load)到FPGA中,或者期望改变FPGA内的配置配置时,也必须进行重新加载的动作。 FPGA与CPLD都很适合用在特殊、特定的工作上,这是以此类芯片的技术本质来做为合适性的考量,然而有时在以经济性为主的权衡评估下也适合使用FPGA、CPLD,或者有时也会以工程师的个人偏好与经验来决定。

责任编辑:xj

原文标题:三类主要的可编程逻辑器件

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

pal

+关注

关注

1文章

43浏览量

27274 -

gal

+关注

关注

0文章

24浏览量

20241 -

可编程逻辑器件

+关注

关注

5文章

139浏览量

30308

原文标题:三类主要的可编程逻辑器件

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

德州仪器推出全新可编程逻辑产品系列

什么是现场可编程逻辑阵列?它有哪些特点和应用?

FPGA零基础学习系列精选:半导体存储器和可编程逻辑器件简介

可编程片上系统的基本特征和主要应用

可编程片上系统是什么

现场可编程门阵列是什么

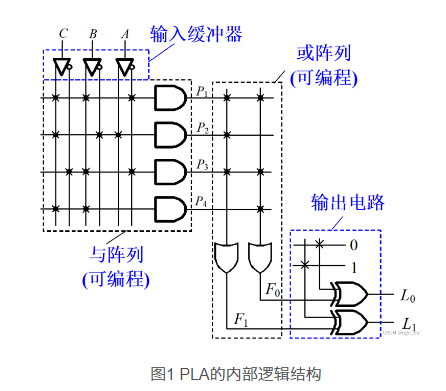

可编程逻辑阵列PLA内部逻辑结构示意

可编程逻辑器件的优化过程主要是对什么进行

近日AMD宣布将停产多种可编程逻辑器件

三类主要的可编程逻辑器件简介

三类主要的可编程逻辑器件简介

评论