双方合作包括多个签核域和跨库特征提取,以加速设计收敛

签核解决方案的创新能够解决从5纳米到3纳米的独特挑战,以确保签核准确性,并将运行速度提高20倍、内存消耗减少50%

ECO迭代减少5倍、提高硬件效率,从而提高客户的生产效率

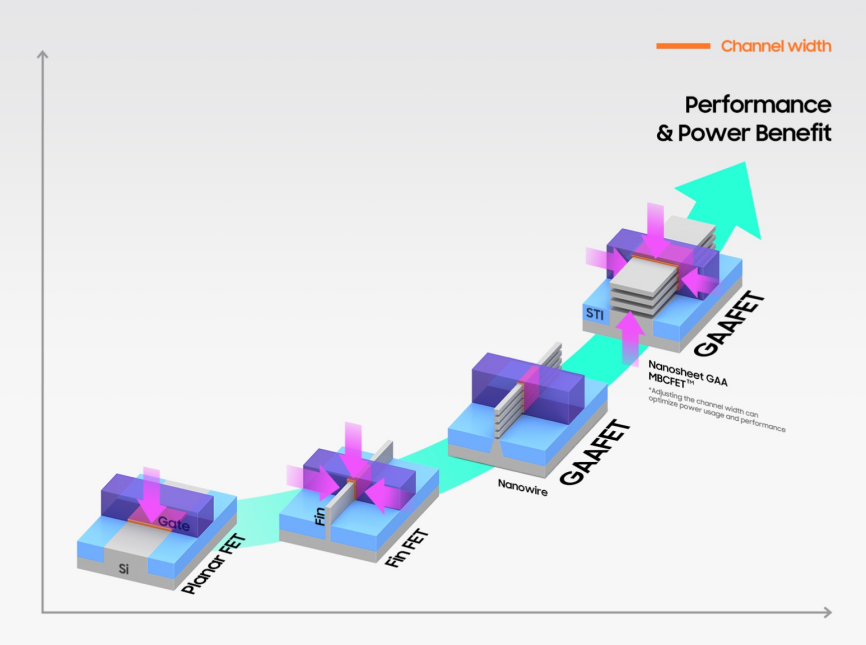

新思科技(Synopsys, Inc., 纳斯达克股票代码:SNPS)近日宣布,凭借其行业领先的黄金签核产品组合, 公司已与三星晶圆厂展开合作,以实现经过充分认证的流程,显著提升准确性、周转时间和开发者生产效率。针对5G、人工智能和高性能计算SoC,这一流程改进有助于三星5纳米至3纳米工艺节点的客户实现最佳功耗、性能、面积 (PPA) 并加速其结果生成时间 (TTR)。

三星电子晶圆设计技术团队副总裁Sangyun Kim 表示:“三星晶圆厂在诸多前沿应用领域为领先客户提供服务,这些领域要求最高水平的设计性能、鲁棒性和电源效率“。通过与新思科技的合作,我们可以为5到3纳米先进工艺节点的客户提供一流的签核流程。”

新思科技经过充分认证的签核流程包括以下解决方案:

PrimeTime®:支持超低电压变化、过孔变异和多输入开关,与SPICE的相关性为3%,总体内存占用减少50%,基于路径的分析性能提高20倍

StarRC™: 将提取的运行时间改善2倍,准确性保持在标准参考1%范围内

StarRC场求解器:作为支持高级节点的黄金参考部署

PrimeECO™:使设计完成速度提高5倍,消除了实现和签核之间代价高昂的迭代

PrimePower:使用RTL模拟矢量提供8倍的门级功率分析

SiliconSmart®:整体性能提高10倍,包括启用新思科技云服务,显著缩短库特征提取的周转时间

新思科技设计集团工程高级副总裁Jacob Avidan表示:“与半导体设计和制造领域的行业领先企业合作是我们能够持续进行设计创新的核心所在“。我们很幸运能够与三星晶圆厂合作,凭借对三星最新先进工艺技术的高度信心,共同推动各种签核技术的创新、扩展性能极限、并降低设计所需的余量。我们期待着在未来的设计和应用领域继续合作。”

本次合作涵盖Fusion Design Platform™签核解决方案的广泛产品组合,包括PrimeTime静态定时分析、PrimeECO设计收敛、PrimePower功耗分析、StarRC提取和SiliconSmart库特征提取。

责任编辑:xj

-

三星电子

+关注

关注

34文章

15880浏览量

181405 -

新思科技

+关注

关注

5文章

812浏览量

50454 -

3nm

+关注

关注

3文章

231浏览量

14054

发布评论请先 登录

相关推荐

三星3nm良率仅20%,仍不放弃Exynos 2500处理器,欲打造“十核怪兽”

新思科技携手三星加快3nm节点设计的收敛和签核

新思科技携手三星加快3nm节点设计的收敛和签核

评论