各种类型的Memory在FPGA设计中被广泛使用,例如单端口RAM、简单双端口RAM、真双端口RAM、单端口ROM以及双端口ROM。这些RAM或ROM都可通过coe文件的形式定义其初始值。那么可能在实际应用中会出现这样一种情形:设计的其他部分未做任何改动,只是更新RAM初始值。那么该如何操作更为方便呢?

如果采用传统方式,先定义好coe文件,然后重新生成IP,这样就必须重新执行整个设计流程包括综合、布局布线,编译时间可想而知。但换个角度,细细分析一下,只是初始值改动,那么能否通过ECO(Engineering Change Order)的方式实现呢,就像更改触发器初始值或者查找表的真值表内容一样?答案是肯定的。这样做好处也是显而易见的:无需重新布局布线,只需更改RAM相关属性,然后再次生成.dcp(这个不是必须的),最后生成.bit或.bin文件,这样最大程度地继承了原有设计,也最大程度地缩短了编译时间。采用此方法的前提是RAM的规格要保持不变,这里的规格包括数据位宽和RAM深度。

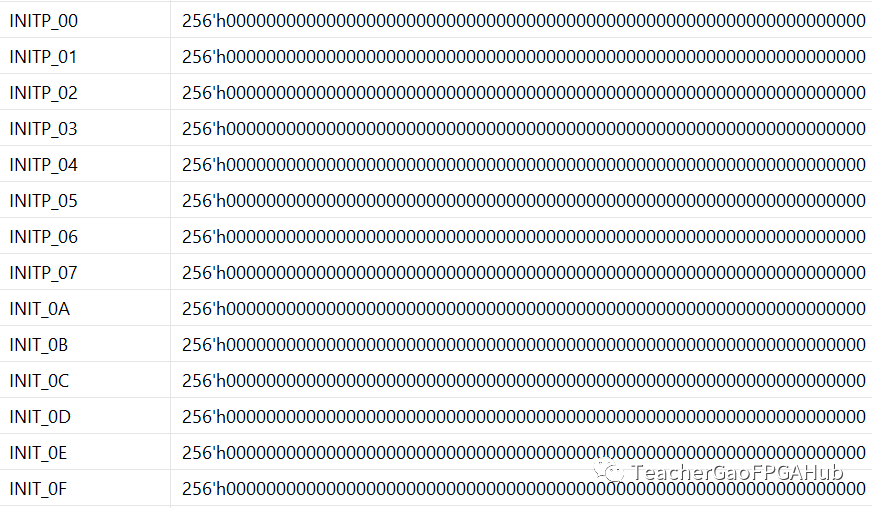

这里我们以Block RAM为例,先看看有哪些属性与初始值密切相关,如下图所示。基本上凡是以INIT打头的属性都与初始值相关。更新初始值本质上就是重新设定这些初始值。这些初始值是在IP生成阶段根据coe内容被设定的。

第一步,根据更新后的coe文件生成一个同规格的IP,并对该IP执行OOC综合。

第二步,打开第一步生成的.dcp文件,找到相应的Block RAM,获取上文提到的这些属性对应的属性值。

原文标题:ECO方式更新RAM/ROM初始值

文章出处:【微信公众号:Lauren的FPGA】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1663文章

22493浏览量

638951 -

ROM

+关注

关注

4文章

579浏览量

89363 -

RAM

+关注

关注

8文章

1400浏览量

120967

原文标题:ECO方式更新RAM/ROM初始值

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

深入解析DS1557:功能强大的非易失性计时RAM

详细解释Keil-MDK中Code、RO-data、RW-data、ZI-data的含义

单片机里的程序运行方式

奇捷科技EasyAI ECO Suite即将发布

智能显示模块怎么在显示工程中给寄存器设置初始值?我想给变量一个上电的默认值该如何设置?

智能显示模块怎么在显示工程中给寄存器设置初始值?我想给变量一个上电的默认值该如何设置?

使用J-Link Attach NXP S32K3导致对应RAM区域被初始化成0xDEADBEEF

如何操作ECO方式更新RAM/ROM初始值更方便?

如何操作ECO方式更新RAM/ROM初始值更方便?

评论