《工业级SiC MOSFET的栅极氧化层可靠性——偏压温度不稳定性(BTI)》

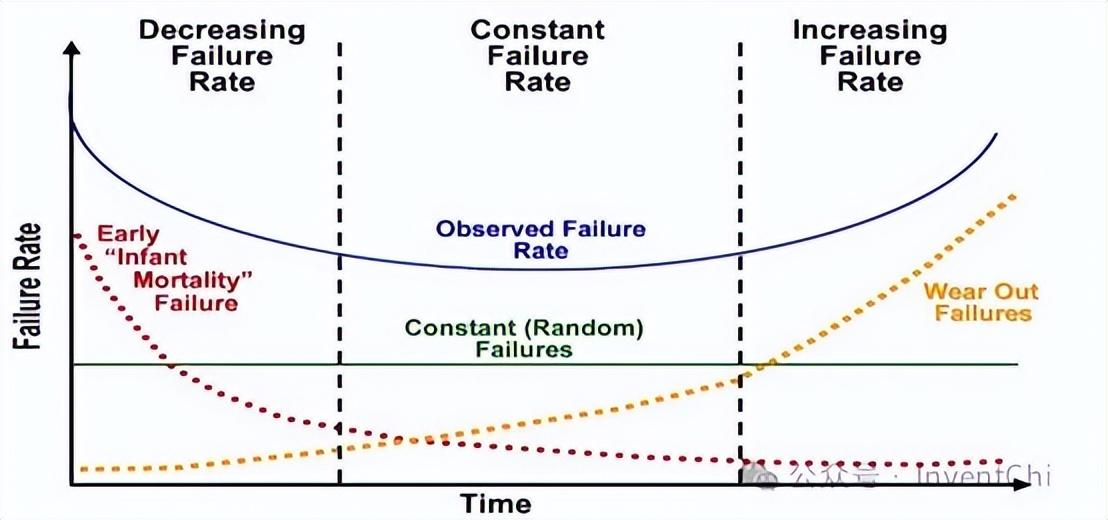

在正常使用器件时,由于半导体-氧化层界面处缺陷的产生和/或充放电,SiC MOSFET的阈值电压可能略有漂移。阈值电压的漂移可能对器件的长期运行产生明显影响,具体取决于漂移量。由于这种漂移通常是向更大的电压值偏移,因此会导致器件的导通电阻变大。这又导致损耗增加,以及散热需求增大,从而可能缩短器件的使用寿命。因此,了解阈值电压的行为并考虑它对设计余量的影响非常重要。

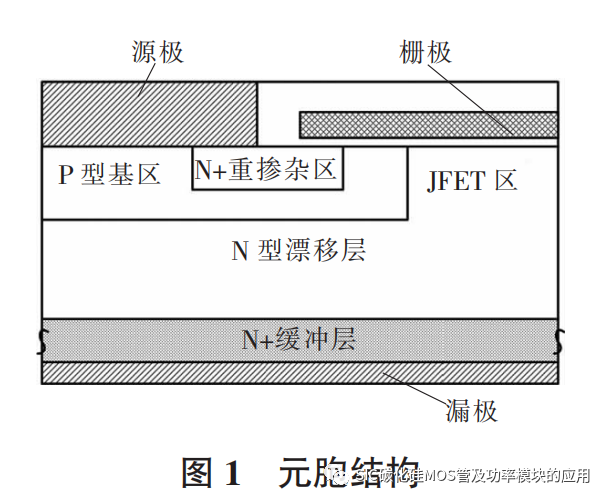

这种现象在Si技术中已非常常见,被称之为“偏压温度不稳定性”(BTI)。考虑到SiC属于宽禁带半导体的事实,即,它不仅由硅(Si)而且由碳(C)原子组成,SiC/SiO2界面的特性相比Si/SiO2界面稍有不同。在SiC/SiO2界面存在位于更大能量范围内的其它点缺陷类型,它们必须通过其它的氧化后处理(比如,用氧化氮代替氮氢混合气氛退火)进行钝化。此外,由于SiC的带隙较宽,在半导体与SiO2栅极氧化层之间更容易进行载流子交换。这些差异自然又会使得SiC MOSFET的电气特性和动态漂移特性相比Si MOSFET稍有改变。

很多努力已经付出在改善SiC MOSFET的性能上,但性能改善未必能带来更好的器件可靠性。为保证器件特性长期稳定,必须密切关注BTI这种漂移现象。在英飞凌,我们在追求一流器件性能的同时,也在设法实现最优异的器件可靠性。因此,我们开展了深入的研究,以期能够深入地了解潜在效应,评估BTI效应在现实应用中的影响,并制定出能够尽可能地抑制BTI效应的措施。

SiC MOSFET在恒定栅极偏压条件下的

1、DC BTI简介

DC BTI效应不仅存在于SiC功率器件中,在硅(Si)技术中也很常见。当在高温条件下给Si或SiC MOSFET的栅极施加恒定的DC偏压时,可以观察到阈值电压和导通电阻的变化。改变的幅度和极性取决于应力条件(偏压、时间、温度)。施加正栅极偏压应力(PBTI)时,通常可以观察到阈值电压向更高的电压偏移;而如果施加负栅极偏压应力(NBTI),阈值电压则向相反的方向偏移。这种效应是由SiC/SiO2或Si/SiO2界面处或附近的载流子捕获引起的,可以通过优化器件工艺控制在最低水平。为更好地了解和预测SiC MOSFET中的DC BTI,英飞凌对这个问题展开了深入的研究,重点了解它相比Si技术存在哪些不同。就Si MOSFET而言,英飞凌过去已经对BTI有了扎实的了解,并且已与众多著名高校一道为科学进步作出了重大贡献。已经掌握的退化物理学和电气测量技术知识,如今已被用于研究英飞凌的SiC器件。事实上,尽管材料特性不同,Si和SiC技术在DC BTI方面却存在许多相似之处。然而,它们在有些方面仍然存在不同,在测量和评估特定应用中的参数变化时必须考虑到这些不同。

2、测量SiC功率器件的DC BTI

由DC BTI引起的阈值电压变化由两个分量组成:一个是快速、可恢复的分量,另一个是准永久(恢复很慢)的分量。准永久分量决定器件的长期漂移量,而快速分量能在短时间内恢复。

为了获得可比较的漂移值,已制定测定BTI漂移的工业标准,如JESD22和它的扩展标准AEC-Q101。这些标准都是以Si技术为基础建立的,必须针对SiC技术进行完善,如下所述。

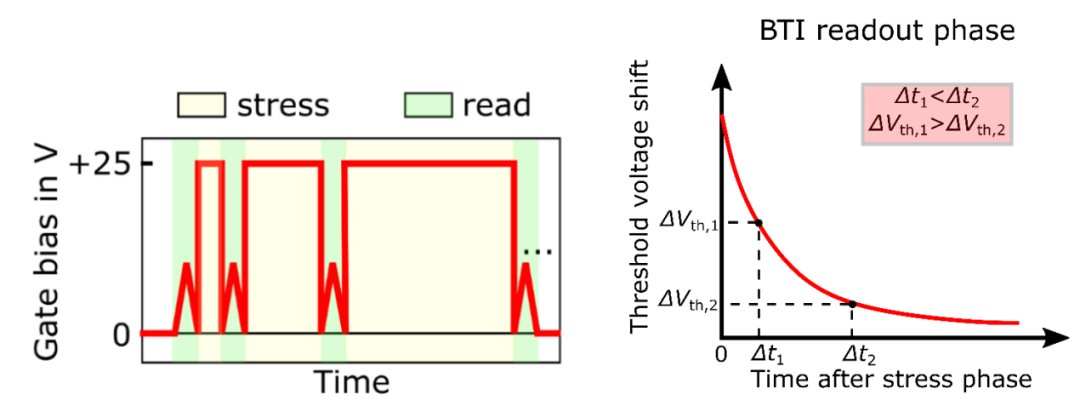

图6.以PBTI(脉冲BTI)应力为例,典型的DC BTI MSM(测量-应力-测量)序列。左图显示的是测量信号与时间的关系。右图显示的是阈值电压漂移的恢复与时间的关系,旨在表明读数延迟对提取的阈值电压漂移的影响。即使读数时间有很小的差异,提取的阈值电压漂移也有很大不同。

测量DC BTI的传统方法是以测量-应力-测量(MSM)为顺序,先反复地给栅极施加偏压和温度应力,然后读数,如图6中的左图所示。借助这种方法及合适的设备,以上所述的两个漂移分量都能被测量出来。但是,获得的阈值电压漂移在很大程度上取决于读数时间——即应力阶段与读数阶段之间的时间间隔,以及器件的状况。从图6中的右图可以看出,阈值电压漂移在应力结束后以指数级速度恢复。于是,即使读数时间有很小的差异——比如1ms vs. 100ms,提取的阈值电压漂移也有很大不同。因此,这种简单的方法存在的缺点是重现性差,且难以区分阈值电压漂移中的完全可恢复的快速分量(滞后效应)与更加依赖于应用的准永久分量。

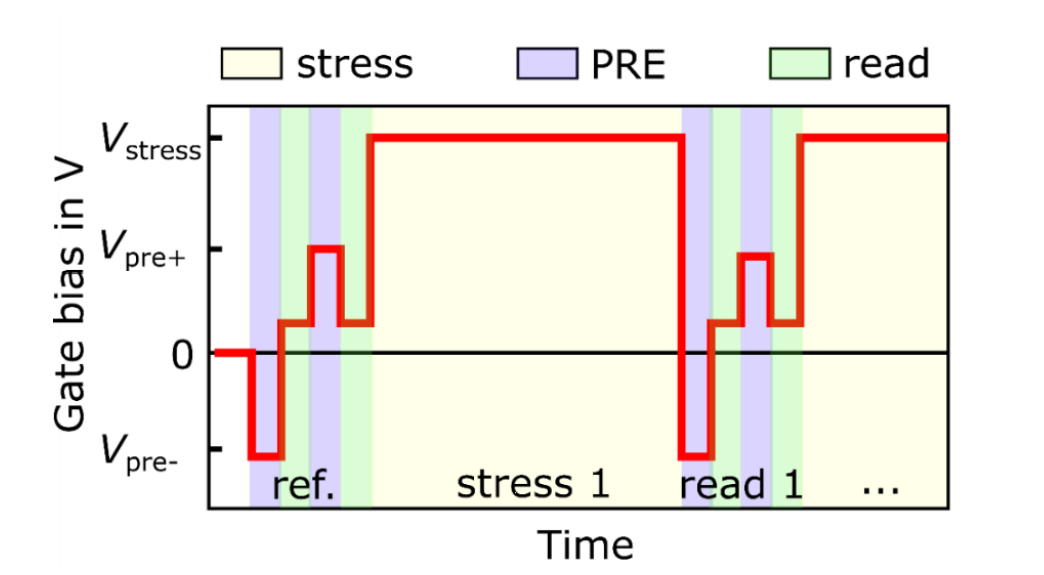

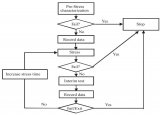

因为这个原因,英飞凌建议使用改进版的BTI测量序列,其中需要用到预处理脉冲,如图7所示。以预处理过的PBTI为例,读数阶段包含累积脉冲、在固定电流电平下的一次读数、反向脉冲和二次读数。在所有序列都完成之后,即在二次读数时,留下的主要是准永久的BTI分量,它几乎无法恢复或者恢复很慢。这意味着,预处理使得测量结果更容易被重现,更不易受到读数延迟和器件状况的影响,并允许正确地区分滞后效应与漂移效应。

图7.预处理过的PBTI的测量序列。读数阶段包含累积脉冲、一次读数、累积脉冲和二次读数。二次读数得到的是最稳定的、可重现的结果。

同一个读数阶段中的一次读数与二次读数之差代表阈值电压滞后现象。它随时间发生的漂移表示产生了新的界面态。预处理脉冲模拟的是栅极在应用中的开关过程,可将陷阱态转化为预定的电荷态,从而减少读数延迟与器件状态的影响。

3、SiC和Si功率MOSFET的DC BTI比较

在以前发表的文章中,经常是说SiC MOSFET的漂移量显著高于Si功率器件。然而我们已经证明,英飞凌的SiC功率MOSFET具有的NBTI漂移量(负BTI)很小,可与最先进的Si 超结MOSFET器件相媲美(即使在给器件施加明显的过应力时)。这一结果是通过优化器件工艺来实现的。针对SiC,我们给出了几种不同的工艺处理所带来的不同结果,以证明通过优化SiC/SiO2界面来改善或降低BTI的可能。

1

负偏压温度不稳定性(NBTI)

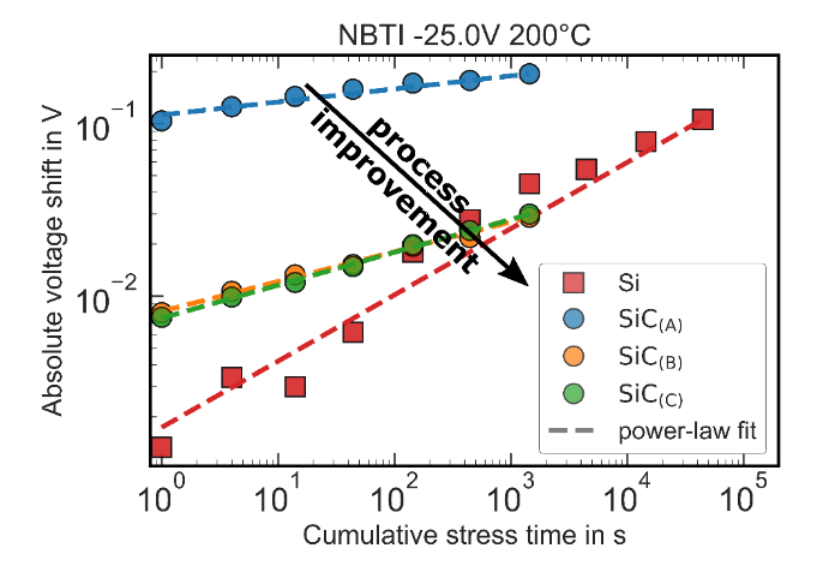

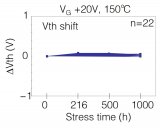

英飞凌研究了在200°C和-25V的偏压应力下的NBTI漂移(图8)。结果显示,通过几种工艺处理的改进,英飞凌SiC MOSFET的NBTI漂移可以减少一个数量级。在本试验的实验窗口中,最好的工艺改进版本所得到的NBTI漂移量,与Si MOSFET处于同一个数量级。SiC MOSFET的漂移斜率甚至更小,表示随着应力施加时间的延长,它的漂移量将比Si MOSFET少。低NBTI是英飞凌SiC MOSFET器件的典型特征之一。

图8.在200°C和-25V的偏压应力下,NBTI随时间的变化。通过改进处理工艺,英飞凌SiC MOSFET的总漂移量可被降到与同等的Si功率MOSFET类似的水平。

2

正偏压温度不稳定性(PBTI)

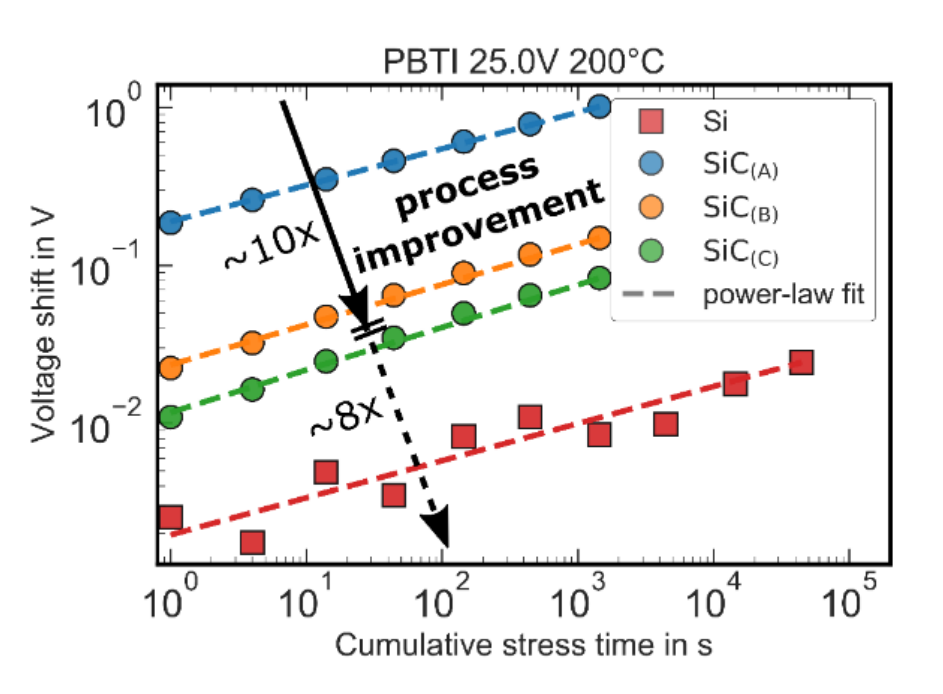

英飞凌研究了在200°C和+25V的偏压应力下的PBTI漂移(图9)。结果显示,Si和SiC的PBTI有许多相似之处,而只有少许差异。

图9.在200°C和+25V的偏压应力下,PBTI随时间的变化。取决于所用的技术和器件工艺,可以看到Si和SiC的PBTI随时间发生的变化是一致的,但绝对阈值电压漂移并不相同。SiC MOSFET的PBTI更大,但仍然位于100mV的范围以内。

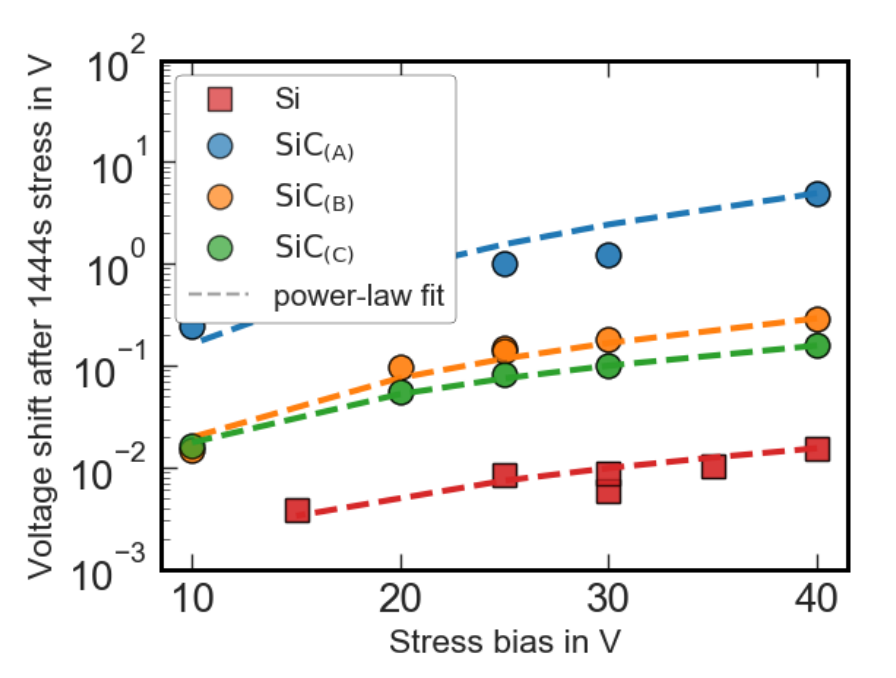

事实上,我们发现,SiC和Si功率MOSFET的PBTI随时间发生的变化、电压加速(图10)和与温度的关系都是一致的。

图10.PBTI在200°C下的电压加速。所有器件(无论是SiC还是Si技术)都显示出相同的电压加速,以及不同的绝对漂移。

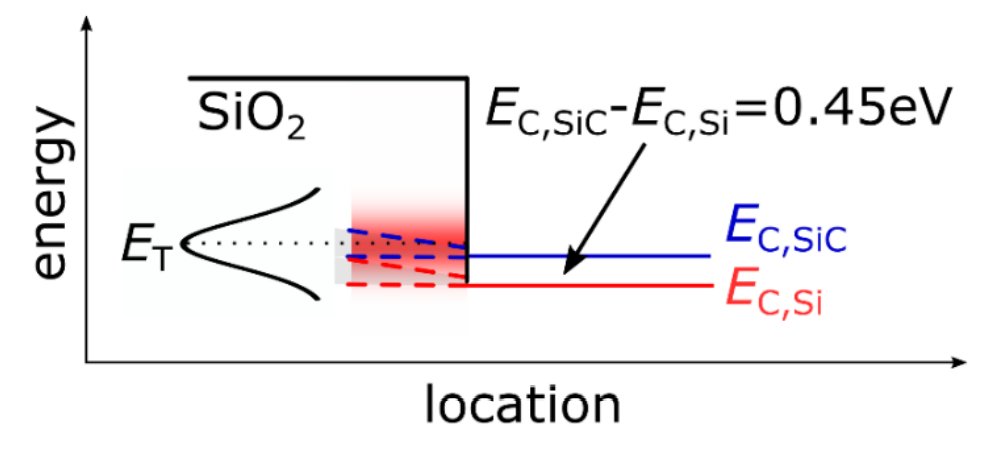

剩余差异是绝对阈值电压漂移的补偿。通过优化器件处理,我们再次实现了漂移量降低一个数量级的目标,从而使得漂移量在本试验的实验窗口中落在了100mV的范围以内。然而,在这些试验条件下,最好的SiC器件的漂移仍是参比的Si器件样品的8倍左右。对于Si功率MOSFET,PBTI通常完全不是问题。所观察到的漂移补偿是SiC能带结构不同所导致的自然结果。

图11.SiC/SiO2和Si/SiO2界面的能带图。这两种技术的栅极氧化层中存在相同的陷阱分布。由于SiC的导带底更高,所以相比Si,这一固有的陷阱能级更容易得到填充,这自然就使SiC的PBTI漂移更大——即使在假定SiO2的陷阱密度相同时。

图11显示的是SiC/SiO2和Si/SiO2界面的能带图,其中包含SiO2中靠近SiC导带边缘的一个已知的内在氧化物陷阱能级。正如我们在中所证明的,SiC导带度更高使得电子更容易被捕获到该陷阱能级中,这是SiC器件在被施加PBTI应力后产生的漂移更大的主要原因。

3

DC BTI漂移的建模

虽然DC BTI已经得到广泛的研究——尤其是Si技术的DC BTI,但目前还没有被普遍认可的物理漂移模型。然而,利用实证幂律或捕获/释放时间图等经验模型,也可能进行寿命终期漂移预测。我们的研究表明,为Si技术开发和验证的预测模型(简化幂律和简化热激发模型),也能非常方便地用于英飞凌的SiC MOSFET。因此,SiC MOSFET的DC BTI漂移能向Si技术一样进行预测。

总结

SiC的DC BTI是严重影响器件可靠性的一个问题。因此,必须通过优化器件工艺来将DC BTI降到最小,并利用合适的测量方法仔细地评估DC BTI。然而,因为能使器件性能更好(RON x A更小)的工艺条件,在NBTI或PBTI方面不一定就表现最好,所以必须采取谨慎的态度来对待DC BTI。英飞凌的SiC MOSFET具有优异的器件性能,同时还拥有很小的NBTI,可与最先进的Si功率MOSFET相媲美。SiC器件的PBTI由于带隙更大而比Si技术略高,但仍位于100mV的范围以内。由于观察发现SiC的PBTI与时间、温度和偏压的关系与Si技术类似,所以可以断定它们对应的潜在物理机制是一样的,因此可以使用与Si技术相同的、同样有预测能力的建模方法。

原文标题:【跨年技术巨献】SiC MOSFET在恒定栅极偏压条件下的参数变化

文章出处:【微信公众号:英飞凌工业半导体】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

半导体

+关注

关注

334文章

27363浏览量

218728 -

电压

+关注

关注

45文章

5607浏览量

115777 -

SiC

+关注

关注

29文章

2814浏览量

62646

发布评论请先 登录

相关推荐

瞻芯电子参与编制SiC MOSFET可靠性和动态开关测试标准

瞻芯电子交付碳化硅(SiC)MOSFET逾千万颗 产品长期可靠性得到验证

瞻芯电子第三代1200V 13.5mΩ SiC MOSFET通过车规级可靠性测试认证

碳化硅模块(SiC模块/MODULE)大电流下的驱动器研究

蓉矽半导体SiC MOSFET通过AEC-Q101车规级考核和HV-H3TRB加严可靠性验证

蓉矽半导体1200V SiC MOSFET通过车规级可靠性认证

瞻芯电子第二代650V SiC MOSFET产品通过车规级可靠性认证

瞻芯电子开发的3款第二代650V SiC MOSFET通过了车规级可靠性认证

英飞凌推出CoolSiC MOSFET G2技术,提升电力效率与可靠性

瞻芯电子两款SiC MOSFET产品通过车规级可靠性认证

3300V SiC MOSFET栅氧可靠性研究

工业级SiC MOSFET的栅极氧化层可靠性

工业级SiC MOSFET的栅极氧化层可靠性

评论