2020年7月,JEDEC固态技术协会正式发布了新的主流内存标准DDR5 SDRAM的最终规范,这意味着新一轮的内存升级换代又要开始了!

自上一代DDR4内存标准的问世到现在,已经历了9年,有数据显示目前DDR4标准产品在服务器和PC领域的渗透率都已经超过了95%,按照摩尔定律或者其他技术预测,新一代的DDR内存标准早该驾到了,由此足见在内存领域技术进步的边际成本是越来越高。

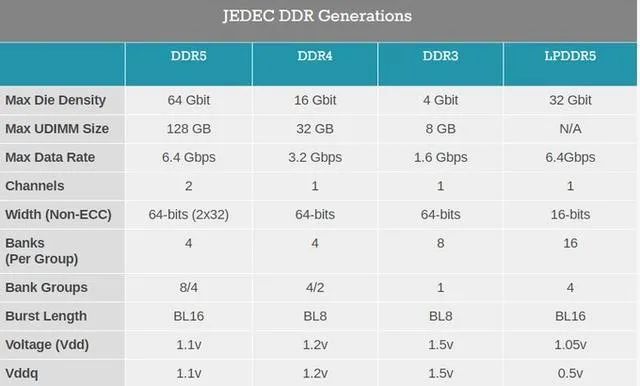

好在DDR5这把“磨”了近十年的“剑”并没有让大家失望,从JEDEC协会公布的信息来看,与上一代标准相比,DDR5将主电压从1.2 V降低至1.1 V,最大芯片密度提高了4倍,最大数据速率提高一倍,突发长度增加一倍,存储单元组数增加一倍。可以说在速度、容量、能耗和稳定性等方面,DDR5都来了一次全面的提升。

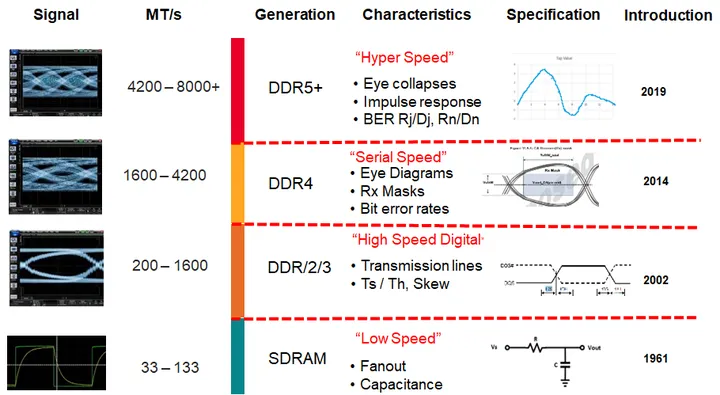

图1:不同DDR内存标准之间的比较 (资料来源:JEDEC)

DDR5标准推出之后,Micron等内存及模块制造商都已经积极行动起来,陆续推出了相关的样品,为即将到来的新一波内存升级潮积极备战。按照以往的经验,2021年DDR5将最先进入服务器市场,之后伴随着工艺稳定和产能爬坡,再逐渐向PC和消费电子等领域渗透。但不管怎么说,这个进程已经启动。

当然,在一轮技术热潮到来之际,在做出“追不追,以及怎么追”等决定之前,既要做到知其然,还要知其所以然,因此今天我们就来看看,DDR5这性能提升背后,究竟暗藏着哪些技术玄机。

DDR5升级背后的技术玄机

数据存储容量和速率是衡量DDR标准代际之间差异的核心指标,在提升此核心性能方面,DDR5放出了以下这些大招儿:

增加整体Bank数量

当存储器密度增加时,需要扩展Bank的数量来应对。DDR5标准中每个Bank组中的Bank数量(4个)保持不变,而将Bank组的数量增加一倍,达到了4或8个。通过允许在任意指定时间开启更多分页,并增加高页面点击率的统计概率,来提高整体的系统效率。增加的Bank组通过提高使用短时序的可能性来减轻内部时序限制。

增加数据突发长度

DDR5将缺省的数据突发长度(Burst Length)从DDR4标准的BL8增加到了BL16,这样就提高了命令/地址和数据总线的效率。也就是说,相同的CA总线读写事务可以在数据总线上实现两倍的数据量,同时限制在同一Bank内受到IO/阵列时序限制的风险。突发长度的增加也可减少相同的64B缓存线数据负载存取所需的IO数量,减少存取特定数据量所需的命令,这对于功耗的控制十分有利。

特别值得一提的是,数据突发长度的增加可以让DDR5 DIMM模块实现双子通道的架构,提高整体的通道并行能力、灵活性和数量,进而优化内存整体的能效。

增加新的命令

在以往DDR SDRAM标准的ALL-BANK REFRESH 命令(REFab)基础上,DDR5增加了SAME-BANK REFRESH (REFsb) 命令。SDRAM在刷新 (REFRESH)之前,需要准备刷新的Bank处于idle(闲置)状态,且这些Bank在刷新命令期间无法继续后续的写入和读取活动。因此在执行REFab刷新命令前,必须确保所有Bank均处于闲置状态,以3.9μs一次计算,一个16Gb DDR5 SDRAM 器件,其持续时间为295ns。

而新增加的REFsb在发出命令之前,每个Bank组中只需一个Bank闲置即可,其余的在发出REFsb命令时不需闲置,对非更新Bank的唯一时序限制为 same-bank- refresh-to-activate 延迟。REFsb命令以细粒度刷新 (FGR) 模式发出,每个Bank平均每1.95μs接收一次REFRESH命令,这样一个16Gb DDR5 SDRAM器件的REFsb 持续时间仅130ns。

有模拟分析数据显示,使用REFsb系统效能处理量比使用REFab时提高6%至9%;REFsb将刷新对平均闲置延迟时间的影响从11.2ns缩短到了5.0ns。

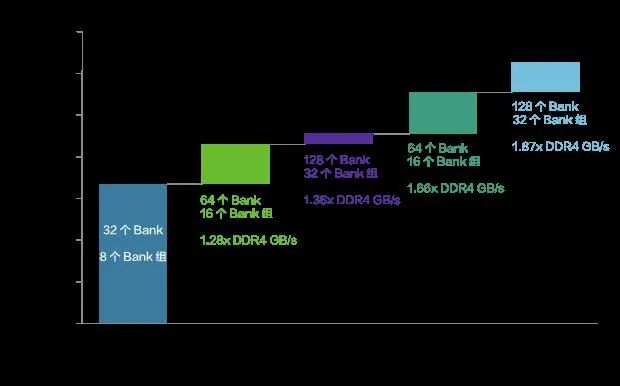

基于上述这几个方面的优化,DDR5在性能上实现了明显的提升。图2展示了,在规定的测试条件下,DDR5与DDR4相比在数据速率上的优势。

图2:DDR5与DDR4相比的性能优势(资料来源:Micron)

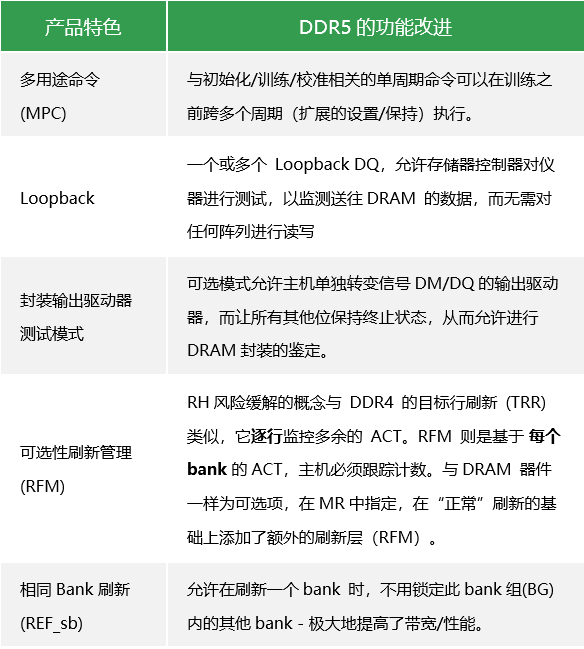

除了在核心性能上的突破,DDR5还在可靠性、可用性与服务性 (RAS)上,以及可操作性上做了诸多优化。

芯片内建错误校正码 (ECC):通过DDR5器件输出数据之前在READ命令期间执行校正,减轻系统错误校正的负担。在DDR4内存上实现ECC功能,需要额外增加一颗芯片,而DDR5原生支持片上ECC,对于提升系统可靠性大有帮助。

PPR强化功能:包括hPPR (硬) 和sPPR (软)两个独立的修复功能。主要的优化在于减少了执行sPPR修复之前需要Bank中备份的列,这样可以将备份和储存大量信息所需的系统时间缩至最短,通常每列数据约2μs。

多用途命令 (MPC):DDR5时钟频率的提高,也给初始化和训练之前的操作执行带来挑战。为此,DDR5使用多用途命令 (MPC) 来执行介面初始化、训练和定期校正等功能,提升操作的效率。

从上文可以看出,一方面DDR5通过增加Bank组、增加突发长度、引入新的REFsb刷新命令等举措,提升核心性能,降低用户总体拥有成本;另一方面通过优化RAS和可操作性为开发和应用带来更大便利,这样双管齐下,为DDR5标准打造了稳固的根基。

表1:DDR5产品特色与功能优化(资料来源:安富利)

DDR5内存条的变化

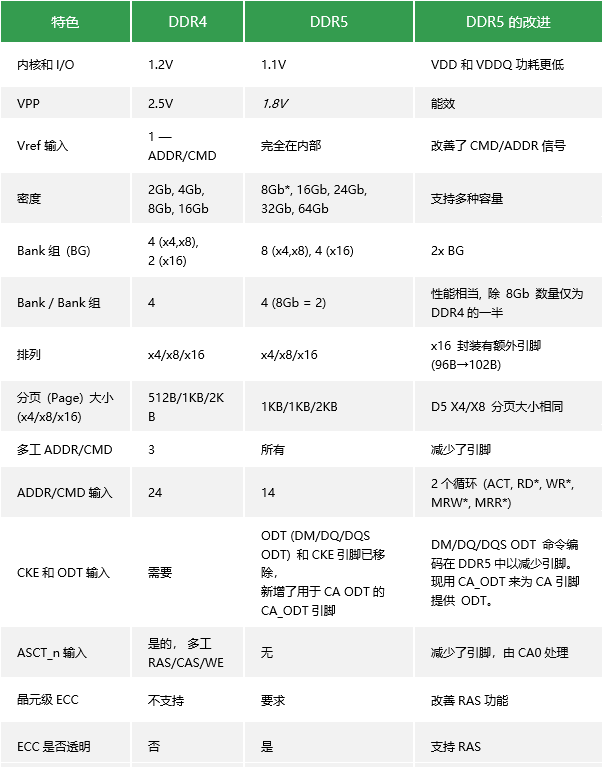

当然,想要最大程度上释放出一个全新内存标准的威力,DIMM内存模块的设计也十分重要。DDR5标准的顺利升级,也必然需要内存模块方案的变化,为其提供助力。从Micron提供的技术文档中我们可以看到,这样的变化主要体现在以下几个方面:

首先,DDR5模块与DDR4模块最大的差别就在于,标准的DDR5模块中有两个独立的子通道,每个子通道最多有两个实体封装的存储器区块 (rank)。每个DRAM封装都可设为主要/辅助拓扑,进而增加逻辑存储器区块以提高密度。独立子通道能提高并行性,并支持存储器控制器更有效率地安排时序,进而打破数据传输量的限制,满足服务器等应用中日益增加的运算需求。

其次,DDR5中增加了本地的PMIC进行电压调节,由于将电源管理的功能从主板转到更靠近内存芯片的模块上,因此这种电源架构可降低主板的复杂性、提升电源转换的效率、增加更多电源管理的功能。

再有,DDR5模块上引入了基于MIPI I3C通讯协定的边带存取功能,能够更好地支持模块上越来越多的主动器件,提高可用性,并监控关键参数以掌握模块工作时与功率、散热等相关的详细信息。

此外,在L/RDIMM模块上,还放置了一对温度传感器IC,对模块表面温度梯度变化进行持续监测,并以此为依据调整流量变化,或者改变风扇速度,通过调优来最大化系统的处理能力。

最后,DDR5模块设计的改变,也催生了CAI、MIR和扩展接地等其他新功能,以利于改善设计配置、电源噪声和模块信号隔离等特性。命令和地址上的ODT及增强的 DQ/DQS/CA/CS 训练等新功能,也可提供更好的信号处理能效、更快的时钟速率,最终实现更高的带宽。

表2:DDR5与DDR4性能比较与优化(资料来源:安富利)

用DDR5开始一个新设计

可以想见,在即将到来的2021年,如何将计算存储方案升级到DDR5,将成为很多开发者——特别是数据中心等计算密集型应用的开发者——案头上的一个重要课题。为了加速这个进程,DDR5的核心技术供应商在快马加鞭推出新产品之外,也纷纷推出了开发者支持计划,比如Micron的DDR5 技术支持计划 (TEP)中,就为经过核准通过的合伙伙伴提供了丰富的技术资源,如:

产品数据手册、电气模型、热模型和仿真模型等技术资源,以帮助其产品开发和平台搭建

选择可用的DDR5元件与模块样品

与其他生态系统合作伙伴建立联系,以助其进行DDR5可用平台的设计与搭建

技术支持和培训资料

简言之,在需求发展的大趋势下,面对DDR5,除了“升级”跟上技术进步的节奏,实际上我们没有其他的选择。现在的关键就在于,如何在升级的这条路上走得更快、更顺畅。为此,安富利作为全球领先的技术分销商,也会为你提供全面和专业的支持。

责任编辑:lq

-

芯片

+关注

关注

457文章

51345浏览量

428237 -

内存

+关注

关注

8文章

3071浏览量

74414 -

DDR5

+关注

关注

1文章

431浏览量

24235

原文标题:DDR5驾到!你的内存又双叒该升级了!

文章出处:【微信号:AvnetAsia,微信公众号:安富利】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

不挑硬件,亲民之选,亦逍遥DDR5内存装机评测

DDR3、DDR4、DDR5的性能对比

DDR5内存的工作原理详解 DDR5和DDR4的主要区别

揭秘DDR5的读写分离技术奥秘

SK海力士开发出第六代10纳米级DDR5 DRAM

DDR5内存面临涨价潮,存储巨头转向HBM生产

SK海力士DDR5芯片价格或将大幅上涨

Introspect DDR5/LPDDR5总线协议分析仪

DDR5 MRDIMM内存标准将发,存储厂商方案先行

DDR5内存条上的时钟走线

0706线下活动 I DDR4/DDR5内存技术高速信号专题设计技术交流活动

谈谈DDR5技术规格的那些事

DDR5内存接口芯片组如何利用DDR5 for DIMM的优势?

DDR5升级背后的技术玄机

DDR5升级背后的技术玄机

评论