本文给想直接使用Vitis HLS 工具在 Standalone 模式下调用 Xilinx Vision Library L1 API 的小伙伴提供了一个非常容易上手的脚本文件。

在论坛上遇到在高层次综合工具中调用视觉库遇到的大多数问题都和 opencv 库以及Xilinx Vision 库的安装路径有关,如今 Vitis HLS 2020.1 之后的版本都不再提供OpenCV 的预编译库,就更需要开发者们将各自工作环境中的库路径,环境变量都设置好。希望这篇博文能给大家调用 Vitis Vision Library 提供向导,提升效率。

Vitis Vision库

Vitis Vision 库是 Xilinx 官方将 Opencv 功能转换至易于在 FPGA 中部署的视觉加速库,可在Vitis 环境中实施。其中 Vitis Vision 库的 L1 目录提供了在 Vitis HLS 层级部署的应用实例设计。这个实例设计中 C-sim 的流程中需要调用 OpenCV 用于测试平台功能,因此需要现有的OpenCV 安装。

Vitis Vision库:

https://github.com/Xilinx/Vitis_Libraries/tree/master/vision

为了适应各种用户环境,从2020.1版本开始,Xilinx 不再提供带有 Vivado / Vitis 工具的OpenCV 的预安装版本。尽管 Vitis 在综合布局布线Vision库的流程中不需要 OpenCV,但是运行示例设计仿真是必需的。

本文使用 Vitis 2020.2 版本介绍了如何创建独立的 Vitis HLS TCL 文件,用户只要在将该 tcl脚本拷贝在 Vision Lirary 的实例目录中,即可在命令行模式下跑完 Vitis_HLS C仿真,综合,联合仿真以及导出 IP 等全部流程。

Vision 的官方文档中包含使用 Vitis HLS standalone 模式的教程,该信息位于以下位置:

https://github.com/Xilinx/Vitis_Libraries/blob/master/vision/docs/getting-started-with-hls.rst

https://xilinx.github.io/Vitis_Libraries/vision/2020.1/index.html#

要利用示例设计或在用户测试平台中引用 OpenCV 库,必须执行以下步骤:

-安装 OpenCV 工具版本3.x

OpenCV 在Linux 的安装和环境设置请参考附录A, 在 Windows 环境下建议使用 Mingw 编译Opencv 安装包。

-设置环境变量以引用 OpenCV 安装路径

-下载 Vitis Version library

-创建 TCL 脚本并在 Vitis HLS 命令行执行

注意:2020.1 Vitis Vision 库已使用 OpenCV 库的3.3版进行了验证。比该版本更新的任何版本都可以使用,但是,版本4.x可能相对于3.x版本具有库功能更改,可能需要修改示例设计测试平台。因此,建议使用 OpenCV 3.x 版运行示例设计。OpenCV 库仅提供测试平台功能,不是必需的,并且不会以任何方式影响 Vision 内核的实现。

环境设置

Linux 环境变量设置要求:

source < path-to-Vitis-installation-directory >/settings64.shsource < part-to-XRT-installation-directory >/setup.shexport DEVICE=< path-to-platform-directory >/< platform >.xpfm

export OPENCV_INCLUDE=< path-to-opencv-include-folder >

export OPENCV_LIB=< path-to-opencv-lib-folder >

export LD_LIBRARY_PATH=$LD_LIBRARY_PATH:< path-to-opencv-lib-folder>

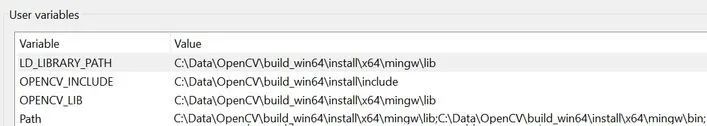

Windows 环境变量设置要求:

示例如下所示,并且每个用户的设置会有所不同,具体取决于 OpenCV 和编译器工具的安装目录。

注意:必须在用户的环境中正确设置 LD_LIBRARY_PATH 动态库的搜索路径环境变量和OpenCV PATH 信息,此脚本和 Vitis Vision 示例设计才能正常工作。此外,OpenCV 的包含库和二进制文件的路径必须包含在系统的环境变量中。否则,将导致仿真期间库包含错误。

操作步骤

要运行 Vitis HLS tcl 脚本,请执行以下操作:

-将修改好的 tcl 脚本放在

-打开 Vitis HLS 命令行外壳并 cd

-运行以下命令:vitis_hls -f run_hls_standalone.tcl

Vitis HLS TCL脚本详细解释

该AR提供了一个 TCL 脚本,用于在 makefile 流之外运行 L1 调整大小示例设计。该脚本基于Windows 环境。该脚本基于以下环境设置:

-OpenCV 版本3.4.11

Linux:

set XF_PROJ_ROOT"/home/vicky/Xilinx/Vitis_Libraries-master/vision"

set OPENCV_INCLUDE"/home/vicky/opencv/include"

set OPENCV_LIB"/home/vicky/opencv/lib"

Windows:

- OpenCV include directory /Data/OpenCV/build_win64/install/include

- OpenCV library directory /Data/OpenCV/build_win64/install/x64/mingw/lib

- Vitis Vision Directory /Data/Vitis_Libraries/Vitis_Libraries-master/vision/

TCL脚本文件包含以下部分,本文将逐一介绍

·代表 OpenCV 和项目环境的变量声明

·项目创建命令

·使用 Vitis Vision 库添加设计文件包括路径

·使用 OpenCV 和 VitisVision 库添加 Testbench 文件包括路径

·使用 OpenCV 链接器参考进行 C 仿真

·Vitis HLS IP 综合

·具有 OpenCV 链接器参考的 RTL 协同仿真

· 导出IP

1

变量声明:

变量声明部分的第一部分声明了一些变量,这些变量复制makefile流和该流生成的settings.tcl文件的环境变量。这些变量指向 Vitis Vision Includes,OpenCV 头文件和 OpenCV预编译的库。这些位置可能会根据用户系统的安装路径而有所不同。

设置 XF_PROJ_ROOT“ C:/ Data / Vitis_Libraries / Vitis_Libraries-master / vision”#Vitis Vision库的包含目录

设置 OPENCV_INCLUDE“ C:/ Data / OpenCV / build_win64 / install /include” #OpenCV头文件目录

设置 OPENCV_LIB“ C:/ Data / OpenCV / build_win64 / install / x64 /mingw / lib” #OpenCV 编译的库目录

下一个变量声明部分有助于创建 Vitis HLS 项目,并有助于使脚本可移植:

·设置 PROJ_DIR“ $ XF_PROJ_ROOT /L1 / examples / resize”

·设置 SOURCE_DIR“ $ PROJ_DIR /”

·设置 PROJ_NAME“ hls_example”

·设置 PROJ_TOP“ resize_accel”

·设置 SOLUTION_NAME“ sol1”

·设置 SOLUTION_PART“xcvu11p-flgb2104-1-e”

·设置 SOLUTION_CLKP 5

最后,最后一部分声明变量,这些变量表示 HLS 引用和使用库所需的引用路径和标志。这里我们发现在一个易用性高的脚本中,使用变量而不是代码有助于理解如何使用这些选项。

设置 VISION_INC_FLAGS“ -I $XF_PROJ_ROOT / L1 / include -std = c ++ 0x”#Vitis Vision 包含路径和 C ++ 11 设置

设置 OPENCV_INC_FLAGS“ -I $OPENCV_INCLUDE”#OpenCV 包含目录引用

设置 OPENCV_LIB_FLAGS“ -L $OPENCV_LIB”#OpenCV 库参考

注意:

在 Windows 中,库引用必须包含版本号。本示例使用 OpenCV 3.4.11安装。精确的包含格式将取决于用户的安装,并且可能与下面列出的格式不同。

设置 OPENCV_LIB_REF“ -lopencv_imgcodecs3411-lopencv_imgproc3411 -lopencv_core3411 -lopencv_highgui3411 -lopencv_flann3411-lopencv_features2d3411”

在 Linux include 语句不使用版本号,并给出如下:

设置 OPENCV_LIB_REF“-lopencv_imgcodecs -lopencv_imgproc -lopencv_core -lopencv_highgui -lopencv_flann-lopencv_features2d”

2

项目创建:

项目创建部分非常简单,它会创建一个新的项目目录和项目文件:

open_project -reset$PROJ_NAME

设计文件包括:

设计文件已添加到本节中的设计中。该命令:

-引用单个HLS内核文件:add_files“ $ {PROJ_DIR} /xf_resize_accel.cpp”

-引用 Vision 库和特定于项目的包含合成目录:-cflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} /build

-引用了用于 C 仿真的Vision库和特定于项目的包含目录:-csimflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR}/ build”

完整的命令如下所示:

add_files“ $ {PROJ_DIR}/xf_resize_accel.cpp” -cflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} / build”-csimflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} / build”

Testbench 文件包括:

testbench 文件将在本节中添加到设计中。命令:

-引用 Test bench 文件:add_files -tb“ $ {PROJ_DIR} /xf_resize_tb.cpp”

-引用 Vision 库和特定于项目的包含目录:-cflags“ $ {OPENCV_INC_FLAGS} $ {VISION_INC_FLAGS} -I $ {PROJ_DIR}/ build”

-引用 Vision 库和特定于项目的 C 仿真目录:-csimflags“ $ {OPENCV_INC_FLAGS} $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} /build”

请注意,在测试台标志和设计文件标志中添加了$ {VISION_INC_FLAGS}变量。此设置引用OpenCV 包含文件。

完整的命令如下所示:

add_files -tb“ $ {PROJ_DIR}/xf_resize_tb.cpp” -cflags“ $ {OPENCV_INC_FLAGS} $ {VISION_INC_FLAGS} -I ${PROJ_DIR} / build” -csimflags“ $ {OPENCV_INC_FLAGS} $ {PROSION_IN /建立”

3

项目设置:

现在已经添加了所有需要的 C 源文件,执行项目创建的最后一步。这些命令设置 HLS IP 的顶层函数,并创建一个所需的项目solution。

set_top $ PROJ_TOP#设置HLS IP的顶级文件

open_solution -reset $SOLUTION_NAME#创建项目解决方案

set_part $ SOLUTION_PART#设置解决方案部分

create_clock -period $SOLUTION_CLKP#设置项目目标时钟周期

4

c-sim:

本部分通过将 HLS IP 和 Testbench 设计发送给编译器进行编译和执行,来执行 HLS 流的 C仿真阶段。此命令用于设置编译器链接器标志和 testbench 文件,以及:

-引用 OpenCV包含和预编译的库目录:-ldflags“ -L $ {OPENCV_LIB} $ {OPENCV_LIB_REF}”

-包括用于验证测试台的图像作为主要功能的参数:-argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

完整的命令如下所示:

csim_design -ldflags“ -L ${OPENCV_LIB} $ {OPENCV_LIB_REF}” -argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

5

C到RTL综合:

本部分执行 Vitis HLS C 到 RTL 合成阶段。此阶段不需要标志或选项。

csynth_design

6

C/RTL协同仿真:

本部分在合成后执行 Vitis HLS IP的 RTL 协同仿真。HLS 会自动根据 C test bench 生成RTLtestbench 进行协同仿真,以下指令用于设置编译器链接器标志和 testbench 文件,以及:

-引用 OpenCV包含和预编译的库目录:-ldflags“ -L $ {OPENCV_LIB} $ {OPENCV_LIB_REF}”

-包括用于验证测试平台的图像:-argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

完整的命令如下所示:

cosim_design -ldflags“ -L ${OPENCV_LIB} $ {OPENCV_LIB_REF}” -argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

7

导出IP:

Vitis HLS 流程的最后阶段是设计的输出。本示例导出RTL的设计并运行 Vivado Synthesis,以获取准确的资源利用率和估计的时序结果。

export_design -flow syn -rtlverilog

注意:导出 RTL 的设计并运行 Vivado Synthesis 进行布局布线的过程需要在 Vivado 工具中先载入有效的 license

附件为在 Ubuntu 18.04 版本在 2020.2 上运行成功的 tcl shell, 大家可以下载后稍作修改,根据本文流程在自己的环境中进行实验,有问题欢迎在本帖下方留言。

责任编辑:lq

-

变量

+关注

关注

0文章

613浏览量

28319 -

OpenCV

+关注

关注

29文章

626浏览量

41229 -

Vision

+关注

关注

1文章

195浏览量

18041

原文标题:Vitis Vision | 利用Vitis HLS tcl shell 一键跑通视觉加速例程

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

优化 FPGA HLS 设计

国内直联使用ChatGPT 4.0 API Key使用和多模态GPT4o API调用开发教程!

BK1661 全集成的单芯片 L1 频段 GNSS 解决方案

BK1662 单芯片L1/L5双频GNSS解决方案

BK1616P 全集成的单芯片 L1 频段 GNSS 解决方案(高性价比FLASH版本)

用malloc和calloc功能来实现DAQ,在调试模式下调用calloc和malloc函数时似乎卡住了,为什么?

在Windows 10上创建并运行AMD Vitis™视觉库示例

Vitis2023.2使用之—— classic Vitis IDE

AMD Vitis™ Libraries Vision L3 Isppipeline U50流程示例

AMD-Xilinx的Vitis-HLS编译指示小结

Vitis 统一软件平台文档

研讨会:利用编译器指令提升AMD Vitis™ HLS 设计性能

使用Vitis HLS工具在Standalone模式下调用Xilinx Vision Library L1 API

使用Vitis HLS工具在Standalone模式下调用Xilinx Vision Library L1 API

评论