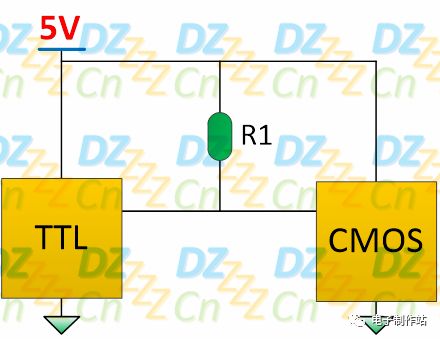

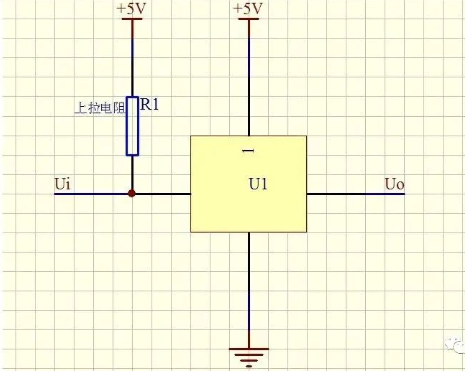

除了前一节讨论的拉电阻基本使用方法外,上拉电阻也可以提升高电平的电压阈值,以便于前后级信号相匹配,比如,TTL逻辑电平驱动CMOS逻辑电平时,我们通常会添加一个上拉电阻R1,如下图所示:

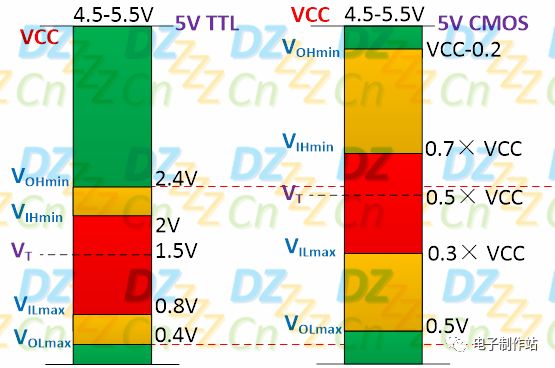

But Why? 我们先来看看TTL电平标准图与CMOS电平标准图,如下图所示:

可以看到,TTL逻辑输出的低电平最大值VOLMAX(0.4V)小于CMOS逻辑输入低电平最大值VILMAX(0.3×VCC=1.5V),因此,TTL低电平驱动CMOS逻辑是完全没有问题的,但是TTL逻辑输出的高电平最小值VOHMIN(2.4V)却低于CMOS逻辑输入高电平的最小值VIHMIN(0.7×VCC=3.5V),换言之,CMOS逻辑可能不能够识别TTL逻辑高电平(注意“可能”这两个字)。

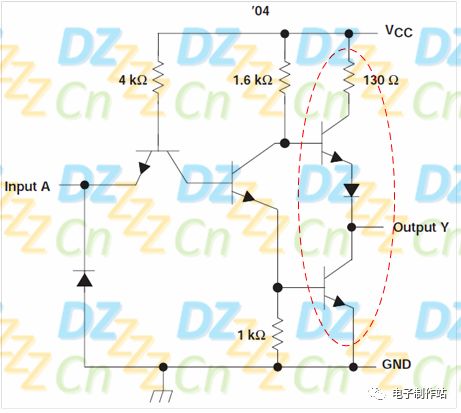

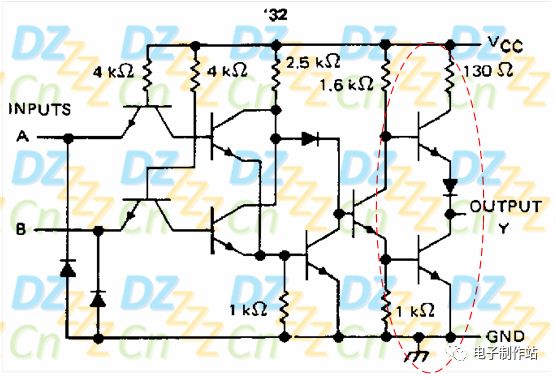

那为什么添加上拉电阻后就能够使TTL逻辑可靠驱动CMOS逻辑呢?我们看看TTL逻辑电路的输出结构,如下图的所示:(下图来自TI公司六反相器7404数据手册)

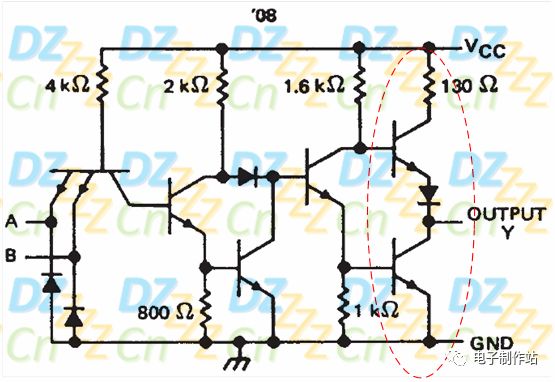

事实上,所有TTL逻辑输出结构都是一致的,如下图所示2输入与门:(下图来自TI公司四个两输入与门7408数据手册)。

如下图所示2输入或门:(下图来自TI公司四个两输入或门7432数据手册)。

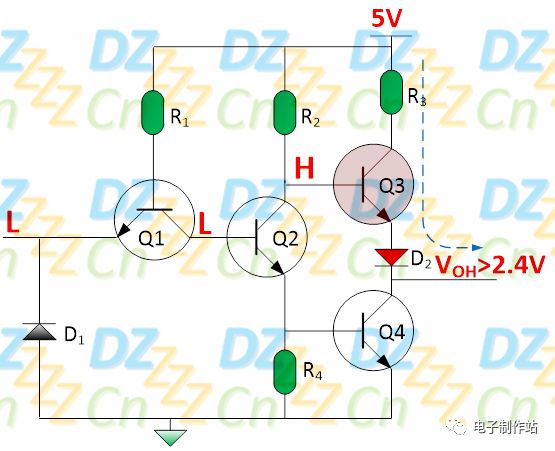

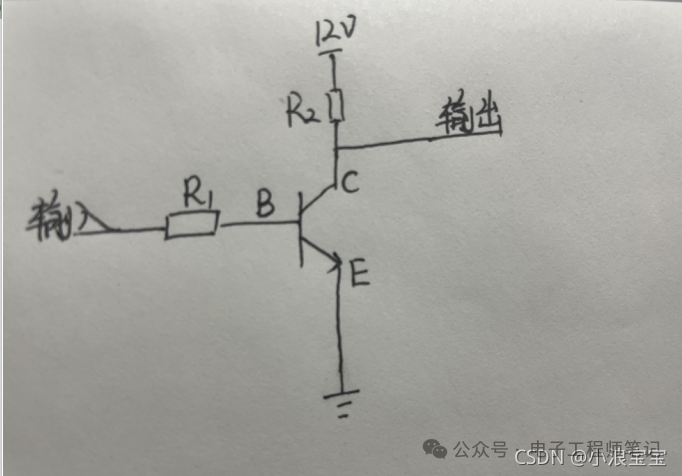

其它TTL逻辑输出结构也是类似的,此处不再赘述。TTL逻辑输出为高电平时内部状态如下图所示:

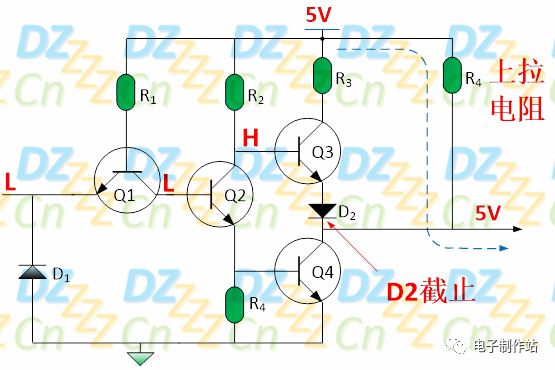

按照TTL电平标准,输出高电平VOH至少2.4V(VOHMIN=2.4V),换言之,这个输出电压也可能高于或低于CMOS高电平输入识别阈值最小值3.5V(不可靠),而添加上拉电阻后的TTL逻辑电路状态如下图所示:

由于上拉电阻R4的存在,使得三极管Q3与二极管D2都处于截止状态,因此输出电平被上拉至5V高电平,妥妥地超过了CMOS逻辑高电平判断阈值的最小值( 3.5V),这样CMOS逻辑电路就能够可靠地进行高电平判断。

但是,反过来CMOS逻辑电平能够可靠地驱动TTL逻辑电平,读者可自行对照两者的逻辑电平标准图就真相大白了。

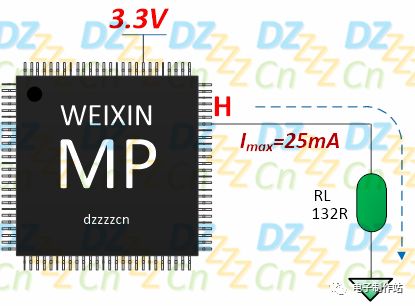

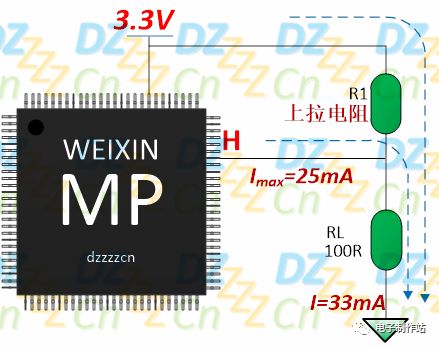

上拉电阻也可以提升单片机引脚的高电平驱动能力。前面我们已经介绍过,任何单片机的IO引脚的驱动电流都是有限的(比如,STM32单片机引脚的驱动能力为25mA),如下图所示:

3.3V单片机IO引脚最大可以驱动约132欧姆的电阻(负载),如果驱动的电阻小于132欧姆,输出高电平“H”就因电流驱动能力不足而使得输出电压下降,这时我们可以添加一个上拉电阻,如下图所示:

100欧姆负载需要约33mA的驱动电流,但单片机IO引脚只有25mA可以提供,额外的8mA将由3.3V直流电源通过上拉电阻R1提供。

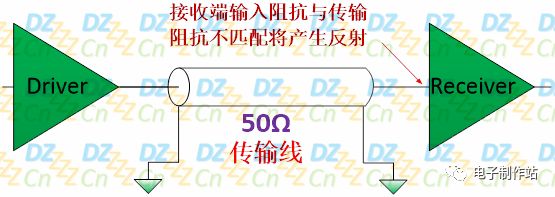

在高速数字设计电路中,信号的传输路径可用传输线来表征,一般差分传输线阻抗约100欧姆左右,单端传输线的阻抗约为50欧姆左右,如果接收端的输入阻抗与传输线阻抗不匹配(匹配就是相等的意思),则会引起信号反射,如下图所示:

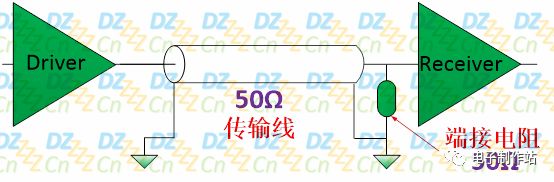

事实上,大多数接收端的输入阻抗远大于传输线阻抗,将传输线出来的信号直接与接收端对接必定将产生反射,从而引起信号完整性(Signal Integrity, SI)问题,因此,我们通常都会使用各种端接手段进行阻抗的匹配,添加下拉电阻就是其中一个手段,如下图所示:

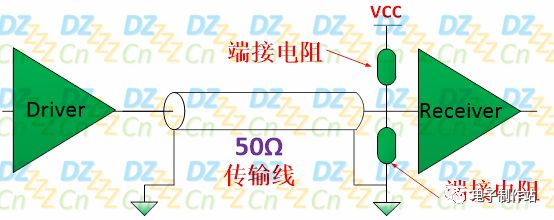

也可以使用上下拉电阻配合的方式进行阻抗的匹配(远端戴维南端接),如下图所示:

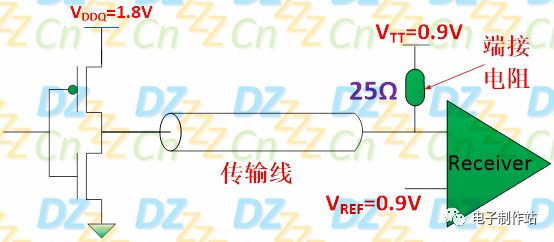

如果读者有过DDRII SDRAM的应用经验,会发现其中有一个VTT电压,如下图所示:

VTT就是端接电压(termination voltage),它通常是VDDQ的一半。差分传输线的端接原理也是相似的,至于更多细节方面可参考系列文章《高速数字逻辑电平标准之SSTL》及《高速PCB设计之端接》,此处不再赘述。

我们在说某个电阻是上拉电阻或下拉电阻的时候,它其实还同时有限制电流的能力,只不过在使用拉电阻过程中,上拉或下拉的功能占主导地位,也因此而得名,你可以把端接电阻称为上拉电阻或下拉电阻,但你总不会称其为限流电阻吧?

责任编辑:xj

原文标题:上/下拉电阻

文章出处:【微信公众号:玩转单片机】欢迎添加关注!文章转载请注明出处。

-

CMOS

+关注

关注

58文章

5729浏览量

235771 -

电阻

+关注

关注

86文章

5536浏览量

172385 -

TTL

+关注

关注

7文章

503浏览量

70326

原文标题:上/下拉电阻

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DAC101S101初次上电瞬间下拉电阻的开关是默认闭合的吗?

【RS-485总线】详解RS-485上下拉电阻的选择

上/下拉电阻详解

上/下拉电阻详解

评论