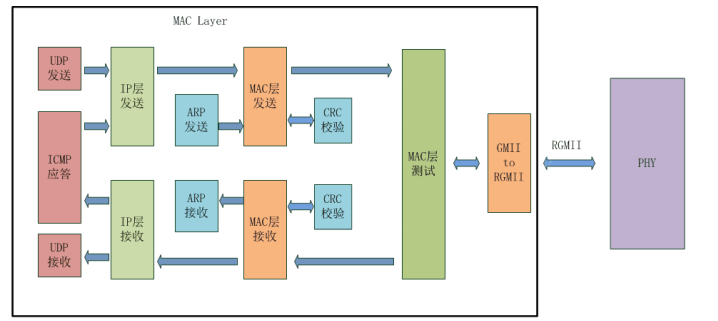

在开发以太网接口的过程中经常看到 MII、RMII、GMII、RGMII等英文缩写名称。在开发接口前,先将这些名词搞清楚。

1 MII

MII(Medium Independent Interface)的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

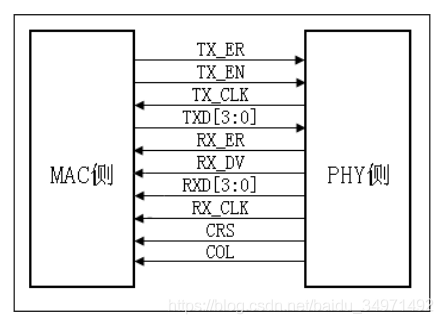

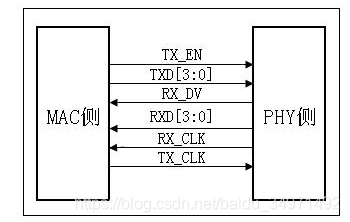

MII支持10兆和100兆的操作,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多

RXD(Receive Data)[3:0]:数据接收信号,共4根信号线;

TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。对于10Mbps速率下,TX_ER不起作用;

RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。对于10Mbps速率下,RX_ER不起作用;

TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;

RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;

TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只有PHY在半双工模式下有效;

COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效。

MII接口一共有16根线。

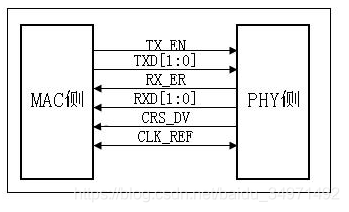

2 RMII

RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线,所以它一般要求是50兆的总线时钟,是MII接口时钟的两倍。

3 GMII

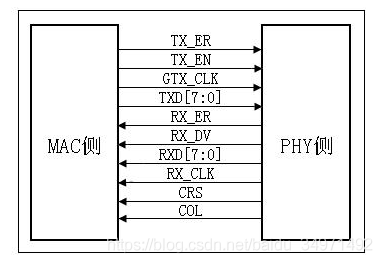

与MII接口相比,GMII的数据宽度由4位变为8位,GMII接口中的控制信号如TX_ER、TX_EN、RX_ER、RX_DV、CRS和COL的作用同MII接口中的一样,发送参考时钟GTX_CLK和接收参考时钟RX_CLK的频率均为125MHz(1000Mbps/8=125MHz)。

在这里有一点需要特别说明下,那就是发送参考时钟GTX_CLK,它和MII接口中的TX_CLK是不同的,MII接口中的TX_CLK是由PHY芯片提供给MAC芯片的,而GMII接口中的GTX_CLK是由MAC芯片提供给PHY芯片的。两者方向不一样。

在实际应用中,绝大多数GMII接口都是兼容MII接口的,所以,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK(两者的方向是不一样的,前面已经说过了),在用作MII模式时,使用TX_CLK和8根数据线中的4根。

GMII是千兆网的MII接口。GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式。

4 RGMII

RGMII接口表示简化了的GMII接口。RGMII均采用4位数据接口,工作时钟125MHz,并且在上升沿和下降沿同时传输数据,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式,支持传输速率:10M/100M/1000Mb/s ,其对应clk 信号分别为:2.5MHz/25MHz/125MHz。

责任编辑:xj

原文标题:基于FPGA千兆以太网的开发(1)

文章出处:【微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1635文章

21834浏览量

608217 -

接口

+关注

关注

33文章

8770浏览量

152381 -

千兆以太网

+关注

关注

0文章

67浏览量

13948

原文标题:基于FPGA千兆以太网的开发(1)

文章出处:【微信号:leezym0317,微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

以太网端口的类型和特性

车载以太网与传统以太网的区别

以太网要怎么连接

工业以太网和普通以太网区别在哪

以太网接口与网线接口的关系

基于FPGA千兆以太网的开发:以太网接口中的名词解释

基于FPGA千兆以太网的开发:以太网接口中的名词解释

评论